# TRIGGER PROCESSOR FOR THE APEX EXPERIMENT AT ARGONNE

John W. Dawson, Stuart J. Freedman, and William N. Haberichter Argonne National Laboratory, Argonne, Illinois 60439 ANL-HEP-CP--90-96

## Abstract

An electron-positron spectrometer is being constructed at Argonne to search for correlated pairs emitted after heavy ion collisions. The trigger for this experiment requires the detection of a positron in either arm of the spectrometer. We describe the trigger for the experiment which selects events with positron annihilation radiation detected in an array of NaI crystals.

# INTRODUCTION

The observation of narrow positron emission lines associated with certain heavy ion collisions remains an unexplained phenomena. Subsequent experimental evidence that the emitted position are correlated with electrons suggests that a new light neutral particle may be the cause. So far experiments to verify this conjecture have failed. A new experiment called APEX[1] is now being constructed at the Argonne superconducting linear accelerator (ATLAS). The new instrument is designed to make precise measurements of the energies and momentum of the positrons and electrons. This features allows the invariant mass to be measured directly and thus the experiment focuses on providing conclusive evidence about the possibility of a new particle.

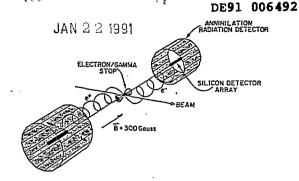

The APEX apparatus is a large low field solenoid with a detector array at either end, shown schematically in Fig. 1.. Positrons and electrons coming from the target with energies below an MeV move in helical orbits which intersect silicon

Fig. 1 Schematic illustration of the APEX apparatus. Major components are labelled. For the sake of clarity, the heavy ion detectors have been omitted.

detector arrays at either end of the solenoid. The cone shaped heavy metal shielding near the target prevents gamma rays from overwhelming the detectors. kinematic parameters of positrons and electrons are determined from a combination of energy, timing, and position measurements with the two silicon arrays. A critical feature of the apparatus is the ability to identify positrons. To accomplish this each silicon detector array is surrounded by a cylindrical array of 24 NaI detectors as shown in Fig. 1. Annihilation radiation from positrons interacting in a silicon detector provides the positron tag. annihilation point is determined by 0.511 MeV gamma ray tomography. The radial positions at which back-to-back 0.511 MeV annihilation photons strike the NaI array are inferred from the segmentation of the array. The corresponding points along the array are inferred from pulse height information from the two phototubes attached to each of the 50 cm long Naï detectors. The NaI detectors are especially treated and light attenuation is relatively high.

Work supported by the U.S Department of Energy, Divisions of High Energy Physics and Nuclear Physics under contract W-31-109-ENG-38.

The trigger for the experiment is based entirely on the NaI detectors and the accelerator duty cycle. The condition for a trigger is the detection of two roughly back-to-back NaI detections with individual energies consistent with being caused by a 0.511 MeV photon; triggers must occur within 25 ns of the beam pulse to be caused by real positrons coming from the target. The accelerator microstructure consists of narrow (< 1 ns) pulses every 80 ns. Obviously the triggering decision must be made faster that the beam pulse spacing.

### TRIGGER HARDWARE

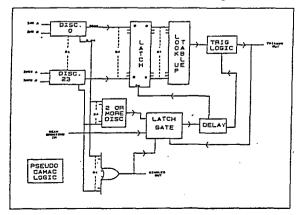

APEX involves a large solenoidal spectrometer, with the trigger formulated from the signals from two barrel shaped arrays of NaI crystals 50 cm long by 6 cm thick with phototubes at each end. There are two processors, one for each array, and the inputs to the trigger processors are the 48 phototube anode signals from the NaI annihilation detector arrays. input impedance of the processors is large and the inputs are bridged providing signals to the downstream ADC's and fast discriminators that read out the annihilation detectors into the regular data flow. A block diagram of the trigger electronics is shown in Fig. 2. Signals from the ends of the individual NaI detectors are first summed. Longitudinal position information is not used in the hardware trigger, and by summing the

Fig. 2 Block diagram of APEX trigger electronics.

signals the variation in pulse height is reduced to 15%. The characteristic NaI pulse shape is rather slow for triggering purposes: approximately 30 nsec rise time and 800 nsec fall time, and in addition the pulse has random distortions resulting from the statistics of photon collection. Accordingly the pulses are first differentiated to reduce the width, and then integrated to smooth the photon fluctuations. Information about the pulse height should come only from the leading edge to permit the required speed of the trigger, and we have attempted to configure the input circuit to accomplish this. The input implements filtering followed by a novel window-discriminator in ECL logic to reduce the false trigger rate from cosmic ray muons which simulate the topology of back-to-back photons.

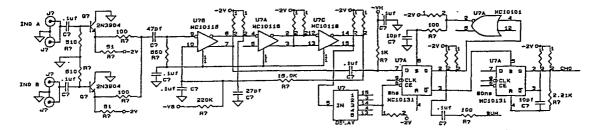

The signals from the two phototubes connected to each of the 24 NaI modules are first summed and clipped. The summed signals are discriminated with a low threshold level (which corresponds to 10-20% of the 0.511 MeV photopeak amplitude), and with a high level which may be adjusted to be some factor (10-100) times the lower level. If the pulse exceeds the upper level the lower level output is vetoed. The input discriminator Fig. 3 makes use of the ECL propagation delay to achieve this window discrimination without a separate discriminator. This "high level" discriminator veto eliminates large pulses primarily coming from cosmic ray muons (about 25 Hz per arm). All the important processor operations are synchronized to the ATLAS pulse rate. the first level the trigger processor arms a pattern finding processor if two of the 24 NaI scintillators fire within the coincidence resolution time during a prescribed period following the beam pulse signal. A two level coincidence causes the pattern of all counters hit during the period to be latched and checked after a delay. If the pattern corresponds to one of the preloaded "valid trigger topologies" a trigger is generated.

The trigger processor in housed outside the CAMAC environment, but is controlled by a module located in the "acquisition"

Fig. 3 Input discriminator circuit.

CAMAC crate. Control signals, diagnostics, and data acquisition are handled through this link to CAMAC. The preset "valid trigger topologies" are written and readout with standard CAMAC commands. After a valid trigger the latched hit pattern is available in a CAMAC register which can be read into the ordinary data flow. After a valid trigger is generated both processors are disabled until they are re-enabled through CAMAC.

### INPUT/OUTPUT DESCRIPTION

### Inputs:

- 1. 48 signal inputs; one for each photomultiplier on each array.

- NIM level gate synchronized with the beam; locks the processor timing to the ATLAS beam cycle period (80 nsec). Input from the experiment is a 10 nsec NIM pulse in time with the beam.

- 3. NIM level signal to set busy latch which disables triggers; allows each processor to be locked by a trigger from the other. The input signal indicates that a valid trigger was generated by the other processor.

- NIM level input to clear the processor trigger (trigger latch clear); resets the processor, enabling the trigger mode.

### Outputs:

48 signal outputs; carried on three 34 pin headers to the downstream electronics.

- NIM level trigger output; indicates a valid trigger condition has been detected.

- 3. NIM single detector hit logic signal.

- NIM two or more signal; indicates that the two or more condition has been satisfied.

# Pseudo-CAMAC Operations:

- 1. F(0) Read trigger data--24 bit read of latched trigger bits.

- F(2) Read and increment memory--low 4 bits data; top 12 bits address.

- F(4) Read coincidence or singles toggle.

- 4. F(8) Clear the internal address register from CAMAC (hit pattern); also clears on C or Z.

- 5. F(10) Clear the trigger latch and activate; also clears on C or Z.

- 6. F(16) Write to memory--low 4 bits data; top 12 bits address.

- 7. F(20) Write discriminator level; changes the lower level discriminator setting to all channels (8 bits).

- F(22) Write singles or coincidence mode (1 bit).

- 9. F(24) activate data-taking mode.

- 10. F(26) de-activate data-taking mode.

# REFERENCES

Proposal for an ATLAS Positron Experiment "APEX", Submitted to United States Department of Energy, (February 1989).

# DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor any of their employers, makes any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.