CERN 93–07 Electronics and Computing for Physics Division 20 December 1993

## ORGANISATION EUROPÉENNE POUR LA RECHERCHE NUCLÉAIRE CERN EUROPEAN ORGANIZATION FOR NUCLEAR RESEARCH

## THE MPPC PROJECT FINAL REPORT

Massively Parallel Processing Collaboration

Editor: F. Rohrbach

#### © Copyright CERN, Genève, 1993

Propriété littéraire et scientifique réservée pour tous les pays du monde. Ce document ne peut être reproduit ou traduit en tout ou en partie sans l'autorisation écrite du Directeur général du CERN, titulaire du droit d'auteur. Dans les cas appropriés, et s'il s'agit d'utiliser le document à des fins non commerciales, cette autorisation sera volontiers accordée.

Le CERN ne revendique pas la propriété des inventions brevetables et dessins ou modèles susceptibles de dépôt qui pourraient être décrits dans le présent document; ceux-ci peuvent être librement utilisés par les instituts de recherche, les industriels et autres intéressés. Cependant, le CERN se réserve le droit de s'opposer à toute revendication qu'un usager pourrait faire de la propriété scientifique ou industrielle de toute invention et tout dessin ou modèle décrits dans le présent document.

Literary and scientific copyrights reserved in all countries of the world. This report, or any part of it, may not be reprinted or translated without written permission of the copyright holder, the Director-General of CERN. However, permission will be freely granted for appropriate non-commercial use.

If any patentable invention or registrable design is described in the report, CERN makes no claim to property rights in it but offers it for the free use of research institutions, manufacturers and others. CERN, however, may oppose any attempt by a user to claim any proprietary or patent rights in such inventions or designs as may be described in the present document.

ISBN 92-9083-056-5

CERN 93-07 Electronics and Computing for Physics Division 20 December 1993

### ORGANISATION EUROPÉENNE POUR LA RECHERCHE NUCLÉAIRE CERN EUROPEAN ORGANIZATION FOR NUCLEAR RESEARCH

# THE MPPC PROJECT FINAL REPORT

Massively Parallel Processing Collaboration

Editor: F. Rohrbach

GENEVA 1993

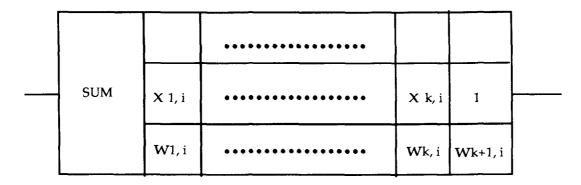

$\mathcal{S}_{ij} = \{ x_i \in \mathcal{S}_{ij} \mid x_i \in \mathcal{S}_{ij} \mid x_i \in \mathcal{S}_{ij} \}$

$\mathcal{A}_{i}$  ,  $\mathcal{A}_{i}$  ,  $\mathcal{A}_{i}$  ,  $\mathcal{A}_{i}$  ,  $\mathcal{A}_{i}$

#### **ABSTRACT**

We report on the work done in massively parallel processing with a view to studying possible solutions for extracting interesting high-energy physics particle events at future high-luminosity hadronic colliders operating in the TeV energy domain. We concentrate on a special Single Instruction Multiple Data (SIMD) architecture: the Associative String Processor (ASP). The Massively Parallel Processing Collaboration (MPPC) Project, grouping nine European institutes, was launched by CERN to carry out this R&D programme. This report, written by partners of the MPPC collaboration, describes the main results achieved at the end of the project: construction of ASP machines, parallel software development and application studies in high-energy physics and in other fields of science. A final, positive assessment of the ASP concept has been made by the Collaboration.

#### **CONTRIBUTORS**

S. Anvar<sup>1</sup>, E. Augé<sup>2</sup>, A. Basso<sup>3</sup>, J.-L. Bertrand<sup>2</sup>, R. Bishop<sup>4</sup>, R. Bock<sup>5</sup>,

J. Bogdany<sup>6</sup>, P. Borgeaud<sup>1</sup>, J.C. Brisson<sup>1</sup>, F. Bugeon<sup>1</sup>, G. Burgun<sup>1</sup>,

D. Calvet<sup>1</sup>, A. Ducorps<sup>2</sup>, F. Dufaux<sup>3</sup>, J. Feyt<sup>5</sup>, O. Gachelin<sup>1</sup>,

M.-N. Gaujour<sup>7</sup>, Ph. Heusse<sup>2</sup>, T. Higgins<sup>4</sup>, M. Izycki<sup>8</sup>, I. Jalowiecki<sup>9</sup>,

A. Krikelis<sup>4</sup>, M. Kunt<sup>3</sup>, B. Lavigne<sup>2</sup>, J. Lancaster<sup>4</sup>, R.M. Lea<sup>4,9</sup>,

H. Le Provost<sup>1</sup>, C. Maillet<sup>1</sup>, M. Martin<sup>8</sup>, M. Mur<sup>1</sup>, G. Odor<sup>6</sup>,

L. Orsini<sup>5</sup>, J.C. Raoul<sup>1</sup>, V. Robert<sup>1</sup>, F. Rohrbach<sup>\*5</sup>,

A. Ster<sup>6,8</sup>, B. Thooris<sup>1</sup> and G. Vesztergombi<sup>6</sup>

<sup>&</sup>lt;sup>1</sup> CEA-CEN Saclay (France), <sup>2</sup> LAL, Université Paris-Sud, IN2P3-CNRS, Orsay (France), <sup>3</sup> EPFL - Ecole Polytechnique Fédérale de Lausanne, EPFL/LTS (Switzerland), <sup>4</sup> ASPEX-Microsystems Ltd., Uxbridge (United Kingdom), <sup>5</sup> CERN, Geneva (Switzerland), <sup>6</sup> KFKI, Budapest (Hungary), <sup>7</sup> Thomson-TMS, Saint-Egrève (France), <sup>8</sup> Université de Genève - Faculté des Sciences (Switzerland), <sup>9</sup> Brunel University, Uxbridge (United Kingdom).

<sup>\*</sup> Spokesman

#### **FOREWORD**

The MPPC Project, originally set up in 1989, was approved in 1990 and a Memorandum of Understanding for the execution of the project was signed by:

#### Main Partners\*

| M. Aymar          | Chef de la Direction des Sciences de la Matière (I  | OSM).        |

|-------------------|-----------------------------------------------------|--------------|

| TVI. I X YIII CIL | Chich de la Direction des Sciences de la Matiere (1 | <b>JOINT</b> |

CEA-CEN Saclay, France

M. Davier Directeur du Laboratoire de l'Accélérateur Linéaire d'Orsay,

LAL, Université Paris Sud, IN2P3 CNRS, Orsay, France

W. Hoogland Director of Research, CERN, Geneva, Switzerland

Prof. R.M. Lea Chairman and Managing Director,

ASPEX-Microsystems Ltd., Uxbridge, United Kingdom

P. Lehmann<sup>†</sup> Directeur de l'IN2P3, IN2P3-CNRS, Paris, France

#### Associated Partners\*

Mrs M.-N. Gaujour CCD Marketing Manager, Thomson-TMS, France

Prof. M. Kunt Laboratoire de Traitement des Signaux, Ecole Polytechnique

Fédérale de Lausanne (EPFL), Switzerland

Prof. R.M. Lea Brunel University, Uxbridge, United Kingdom

Prof. M. Martin Université de Genève - Faculté des Sciences, Switzerland

G. Vesztergombi KFKI, Budapest, Hungary, a new associated partner from 1991

We underline the importance of collaborating with specialists outside the highenergy physics domain for this project. In particular, the importance of the collaboration with experts in signal and image processing like the LTS at EPFL must be emphasized.

A first status report was presented to the Detector Research and Development Committee (DRDC) at CERN at the beginning of 1991. The Project was terminated at the end of 1992. Although all the projected goals were not reached, the main objectives have been achieved: the construction, installation and running in each Main Partner institute of a fine-grain multiprocessor Associative String Processor (ASP) machine, and a broad study of applications of the ASP architecture for real-time processing in high-energy physics and in other fields of research. This work led to a preliminary, positive assessment of the ASP concept.

<sup>\*</sup> The Main Partners collaborated in the full MPPC programme (hardware and software) as opposed to the Associated Partners, not committed to the development of the ASP hardware.

<sup>†</sup> Deceased.

Ad ASTRA per ardua...

### **CONTENTS**

|    | List of Contributors                              | v   |

|----|---------------------------------------------------|-----|

|    | Foreword                                          | vii |

| 1. | INTRODUCTION                                      | 1   |

| 2. | THE ASSOCIATIVE STRING PROCESSOR (ASP) CONCEPT    | 3   |

|    | 2.1 The basic ASP chip                            |     |

|    | 2.1.1 The associative processing element (APE)    |     |

|    | 2.1.2 Chip implementations                        |     |

|    | 2.2 The hybrid module                             |     |

| 3. | MACHINE ARCHITECTURE                              | 9   |

|    | 3.1 The ASP machine architecture                  | 10  |

|    | 3.2 The ASP global bus                            | 18  |

|    | 3.3 The low-level ASP controller (LAC)            | 18  |

|    | 3.4 The ASP boards                                |     |

|    | 3.4.1 The ASPA card (chips)                       | 20  |

|    | 3.4.2 The HASPA card (modules)                    | 22  |

| 4. | THE ASP EMBEDDED NODE (ASPEN)                     | 24  |

| 5. | THE ASTRA MACHINE SOFTWARE                        | 26  |

|    | 5.1 Writing an ASTRA application                  | 27  |

|    | 5.2 Software development tools: the compilers     |     |

|    | 5.3 Operating system tools and run-time libraries |     |

|    | 5.4 ASP documentation                             |     |

|    | 5.4.1 ASPEX documentation                         |     |

|    | 5.4.2 CERN documentation                          | 29  |

|    | 5.5 | Graphics tools                                                   | 30   |

|----|-----|------------------------------------------------------------------|------|

|    | 5.6 | Other ASTRA programming methods                                  | 30   |

|    | 5.7 | An example of applications programming on the ASTRA machines     | 31   |

| 6. | Α ( | CCD INTERFACE TO ASTRA                                           | 31   |

|    | 6.1 | Description of the CCD readout and its interface to the ASTRA    |      |

|    |     | machine                                                          | 31   |

|    | 6.2 | Test results of the CCD-ASTRA system                             | 33   |

|    | 6.3 | A CCD interface for the MPPC machine                             | 33   |

| 7. | API | PLICATIONS                                                       | 35   |

|    | 7.1 | Application studies on a VASP simulator                          | 35   |

|    |     | 7.1.1 Tracking and calorimetry for the SDC level-2 trigger       | 35   |

|    |     | 7.1.2 The LHC high-transverse-momentum muon second-level         |      |

|    |     | trigger                                                          | 37   |

|    |     | 7.1.3 The transition radiation tracking (TRT) detector for LHC.  |      |

|    |     | Simulations for applications of ASP modules for a 100 kHz        |      |

|    |     | trigger                                                          | 40   |

|    |     | 7.1.3.1 Feature extraction                                       | 40   |

|    |     | 7.1.3.2 Benchmark definition                                     | 41   |

|    |     | 7.1.3.3 Benchmark results                                        | 42   |

|    |     | 7.1.3.4 Discussion of the ASP implementation                     | 43   |

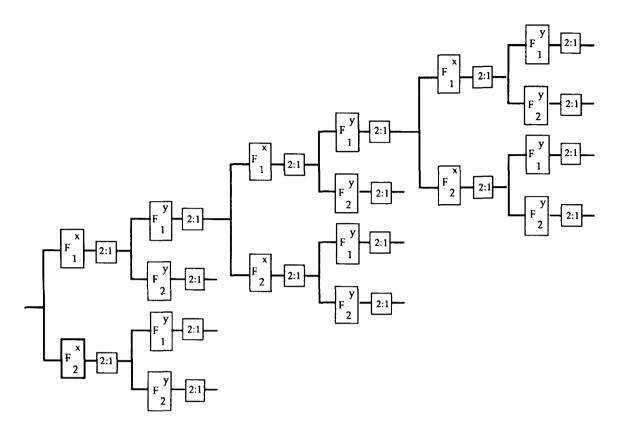

|    |     | 7.1.4 Image coding applications                                  | 45   |

|    |     | 7.1.4.1 Image compression based on a Gabor-like wavelet trans    | form |

|    |     |                                                                  |      |

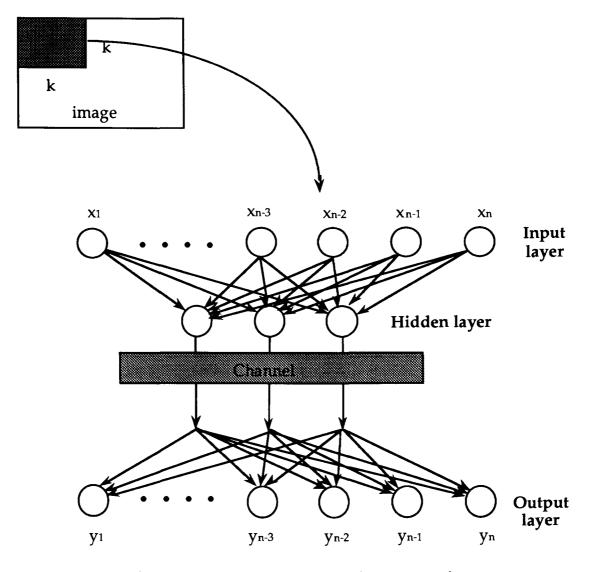

|    |     | 7.1.4.2 Neural autoassociation for image compression: a massiv   | ely  |

|    |     | parallel implementation                                          | 48   |

|    |     | 7.1.4.3 Conclusions concerning the use of ASP for image          |      |

|    |     | compression                                                      | 51   |

|    | 7.2 | Application studies on ASTRA machines                            |      |

|    |     | 7.2.1 Online data-processing in a high-energy physics experiment |      |

|    |     | 7.2.2 The SDC second-level trigger                               | 53   |

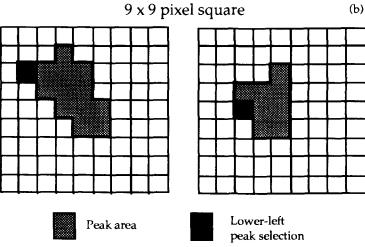

|    |     | 7.2.3 Image processing for peak-finding from cluster data        |      |

|    |     | 7.2.3.1 The peak-finding algorithm                               |      |

|    |     | 7.2.3.2 Algorithm timing results                                 | 56   |

|    | 7.3 | ASPEN evaluation in the NA48 experiment                          | 56   |

| 8. | PEF | RSPECTIVES                                                       | 57   |

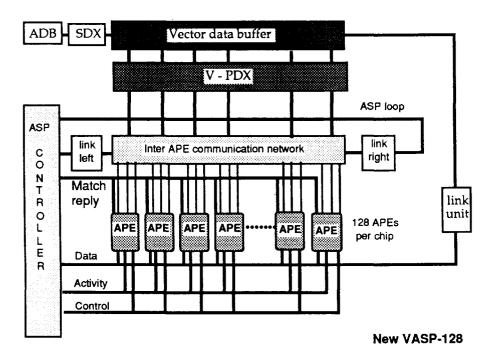

|    | 8.1 | A new chip: the VASP-128                                         | 57   |

|    |     | Development of a two-dimensional ASP                             |      |

| 9.   | SUMMARY AND CONCLUSIONS                               |  |

|------|-------------------------------------------------------|--|

| APF  | ENDIX                                                 |  |

| A.1  | FIRST EXAMPLE: WRITING THE SKELETON OF AN ASTRA       |  |

|      | PROGRAM63                                             |  |

| A.2  | SECOND EXAMPLE: AN EXTENDED PROGRAM, ARRAY OF SUMS 67 |  |

|      | A.2.1 Passing data between HAC and IAC                |  |

|      | A.2.2 Passing data between IAC and LAC                |  |

|      | A.2.3 The pSums implementation                        |  |

|      | A.2.4 The pSums makefile75                            |  |

| Refe | ences 77                                              |  |

#### 1. INTRODUCTION

The starting point of the Massively Parallel Processing Collaboration (MPPC) Project [1] is to be found back in 1988: at that time, it was already recognized that there would be a strong need for real time sophisticated triggering systems for the detectors used with the hadron colliders of the future. Interesting, rare physics events for new discoveries will have to be extracted in real-time from the enormous physical background due to the high value of the total proton–proton cross-section. The task of the triggering system would consist of extracting essential features for tagging interesting physics events from the massive amount of raw information (many megabytes) delivered at a high rate (40–66 MHz) by the multimillion detector channels surrounding a proton–proton collision area.

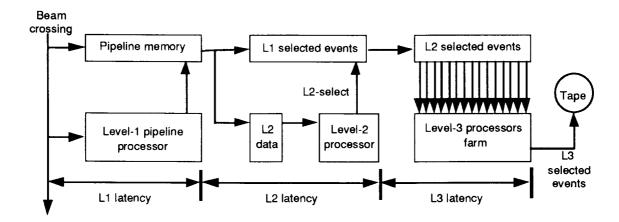

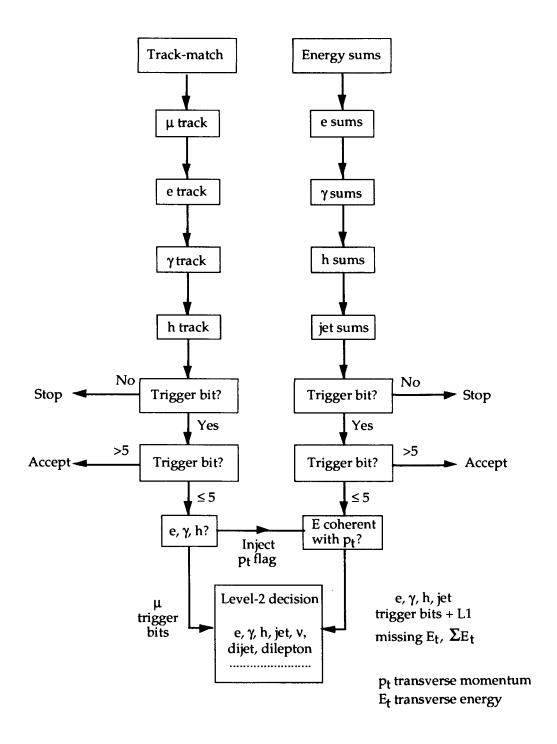

This trigger task was foreseen as a three-step process called level-1, level-2, and level-3 trigger (see Fig. 1).

Figure 1 Three-level trigger organization

Each level is characterized by an acceptable rate and by a latency time. The level-1, mainly hard-wired processor is able to sustain the rate of one event each 16–25 ns with a latency of a few microseconds. Based on a local data analysis, the level-1 process is supposed to reduce the rate by a factor of 1000–5000, allowing an average rate to the level-2 of one event every 10–50  $\mu$ s. Events selected by the level-1 process will be stored in a buffer memory; the accepted latency, which in turn determines the size of this buffer, will be between 50 and 200  $\mu$ s. The level-2 process will be based on a rough, global, topological analysis of the event and energy threshold combinations. As far as this is physics-dependent, the level-2 algorithms need to be flexible, i.e. programmable. The rejection factor is estimated to be between 50 and 100. The level-3 process will be handled by a farm of 1000–5000 high-speed microprocessors on standard boards which

make a detailed physical analysis of each selected level-2 event. The selected level-3 events are then recorded on tape at the rate of about 10 events per second.

In 1988, no tools were available or in sight for performing the complex task of the level-2 trigger.

In 1989, a new Single-Instruction Multiple Data (SIMD) architecture—the Associative String Processor (ASP) devised by ASPEX Microsystems Ltd.—was identified as potentially able to solve the bottleneck foreseen for a level-2 trigger. This led to a collaboration which was established to study potential applications of ASP in High-Energy Physics (HEP) second-level-trigger applications. With this task in mind, the collaboration set up the MPPC Project [2].

This project was focused on two topics: the evaluation of algorithms using massively parallel processors for solving difficult triggering problems, and the learning of the required know-how in designing, building, and using a machine equipped with a large number of parallel processors.

As a first goal, the collaboration dedicated a large fraction of its manpower to establish algorithms and to execute them on the ASP simulator running on a Sun workstation. Later, algorithms were ported on the real machine.

The second pole of the activity concentrated on the specification, design, construction, and commissioning of a machine based on the ASP concept: thousands of integrated processing elements arranged in a string and providing a flexible and scalable architecture endowed with an intelligent and powerful communications network.

A first status report on the MPPC Project was presented to the Detector Research and Development Committee (DRDC) at CERN in 1991 [3]. The main project results have been regularly reported in international conferences and workshops [4–7]. The present report gives an account of all the work done in hardware and software and the main application results obtained by the collaboration during the project.

The first implementation of the machine, ASP System Test-bed for Research and Application (ASTRA)\*, is now operational at CERN, Orsay, Saclay, and ASPEX. As planned, they are used as test benches for online application algorithms and provide real timing values. An ASTRA user-friendly environment has been created at CERN and is available for physicists interested in testing fast, massively parallel, triggering algorithms on the ASTRA machine.

The R&D MPPC Project at CERN ended in 1992 with the installation of the first ASTRA machine. The development of ASP machines continues at CEA-CEN Saclay and at ASPEX Microsystems Ltd.

To be closer to the real use of ASP in HEP experiments, ASPEN, a prototype of an embedded machine has been designed at Saclay. This machine, based on a real-time, distributed processing power philosophy, associates conventional microprocessors (DSP) with a string of ASPs to obtain maximum flexibility and efficiency.

<sup>\*</sup> The ASTRA machine was formerly known as the ASPA machine.

The final goal of these studies is to run online applications in physics experiments.

#### 2. THE ASSOCIATIVE STRING PROCESSOR (ASP) CONCEPT

The ASP consists of a string of Associative Processing Elements (APEs). ASP devices belong to the Single-Instruction, Multiple-Data (SIMD) class of parallel processors. One instruction is simultaneously applied to a large number of identical Processing Elements (PEs), each storing a different datum. Each element possesses its own local memory and is able to perform elementary instructions. To provide the ability for data-dependent processing, each PE is able to make an association between its own stored data and a key pattern which is presented in parallel to all PEs. This associative parallel strategy forms the basis of the ASP architecture concept: the conventional successive addressing of each PE is replaced by an associative global data access (content addressing). All the elements share the same bus, and are also interconnected with high efficiency in order to transfer flags and data.

ASP modules are the basic blocks for the construction of programmable, scalable, fine-grain SIMD machines.

Synchronous and asynchronous communication between APEs is provided through a dynamically reconfigurable inter-APE communications network, with a string topology. Parallel processing is performed on active subsets of APEs, preselected in order to run the steps of dedicated algorithms. The architecture is reconfigurable by programming. The string can be arranged in a loop through the controller and segmented with bypass possibilities. It is fault-tolerant: blocks of faulty APEs may be deactivated without breaking the string.

Loading and unloading data in the string is done on a 32-bit word or byte exchange basis. A typical set of machine operations, which can be considered as its basic cycle, consists of a sequence of suboperations:

- a search then a tag of matching APEs, with a possible shift of the tag along the string, accompanied by a clear of bits, bytes or words;

- the activation of tagged APEs or of a pattern of APEs related to them that will participate in the next step;

- the execution of Read or Write suboperations in the activated elements.

The architecture is scalable to hundreds of thousands of APEs, due to high integration (VLSI/WSI) and low power consumption (≈1 mW per APE). The target cost is low (\$1 per APE) leading to the possibility of massive integration.

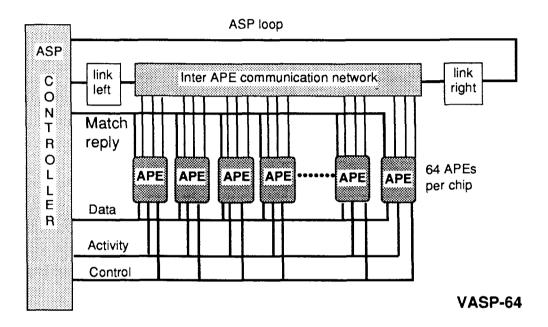

#### 2.1 The basic ASP chip

The chip used in this project is the VASP-64 (see Fig. 2). The VASP-64 chip contains a string of 64 APEs connected to a programmable intercommunications network allowing the APEs to communicate together. The network is used to connect APEs together in a string. A logic block handles the commands (control bus) and the data (data and activity bus) required to execute an operation, and allows one to select a bit/byte or word data format and to mask the data or activity bits.

Figure 2 The associative string processor

VASP chips may be cascaded to build a multichip APE string of any length required by the application. Programmable block links are interspersed in the communications network at eight APE intervals, allowing the string to be partitioned into segments between which communication may be isolated/linked to the neighbouring segment.

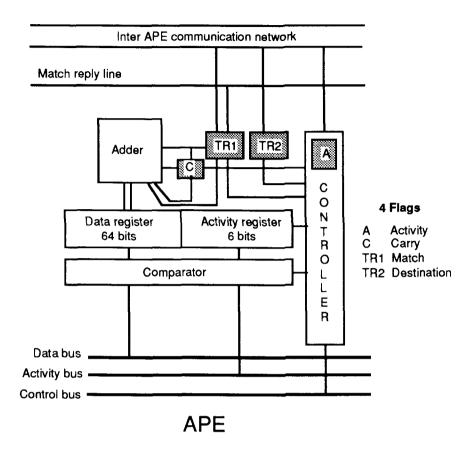

#### 2.1.1 The associative processing element (APE)

The internal structure of an APE is shown in Fig. 3. It contains two main registers, a 64-bit-wide data register and a 6-bit-wide activity register. The data register can be written from the data bus and its contents can be read out on the same bus. The activity register may only be written. The contents of these registers can be compared with the state of the data and activity busses in a bit-parallel fashion. The result of the comparison, match or mismatch, is stored in one or both of the tag registers 'Tr1' or 'Tr2'.

Figure 3 The associative processing element

The serial full adder is able to add two one-bit values representing the contents of two bits of the data register, selected by a search operation, together with the contents of the carry register. The sum is stored in 'Tr1' and the new carry overwrites the contents of the carry register. Other add operations are available between the data bus, the data register, or the flag 'Tr1'.

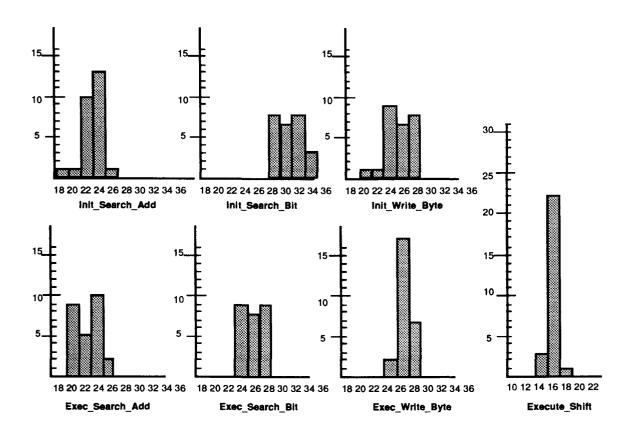

#### 2.1.2 Chip implementations

The first implementation of the VASP-64 was done by ES2 $^{\dagger}$  in a CMOS 2  $\mu$ m dynamic technology using an electron-beam implantation with a time slot of 40 ns in August 1990. The mass production using a mask implantation showed a degradation of the characteristics. The measured time slot, 70 ns, was considered too slow and a new design was started with Hughes [8] on a Silicon On Sapphire (SOS) 1  $\mu$ m static technology (see results for VASP-64/H1-B2 Fig. 4). The present implementation (H1-B3) on a 0.8  $\mu$ m design rule gives a time slot of 25 ns for the slowest subinstruction and has been available since spring 1993.

<sup>†</sup> ES2, European Silicon Structures, Zone industrielle, 13106 Rousset CEDEX, France.

Horizontal scale: time slot in nanoseconds Vertical scale: number of chips

Figure 4 The ASP status: H1-B2 chip speed results

#### 2.2 The hybrid module

A hybrid module (HASP) was designed to allow for maximum processor element density and maximum direct parallel interfacing via conventional electronics to the readout of particle detectors. For this task, dense packages of ASPs had to be constructed. They were based on a modular design using hybridization on insulators of the VASP-64 chips. Three designs were successively developed.

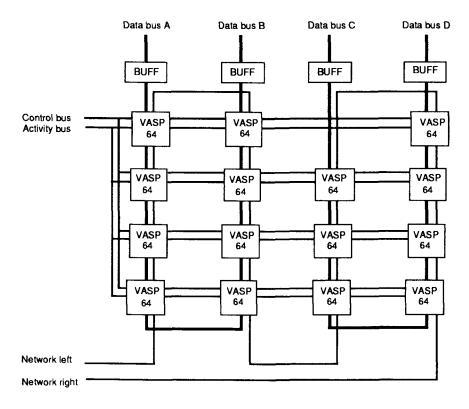

In September 1990 a preliminary design for a HASP with 1024 APEs and four I/O channels was completed (see Fig. 5). Further studies showed that, owing to the large number of pins, an expensive custom package would be required and space for implementing four input channels per HASP was not available on the circuit board.

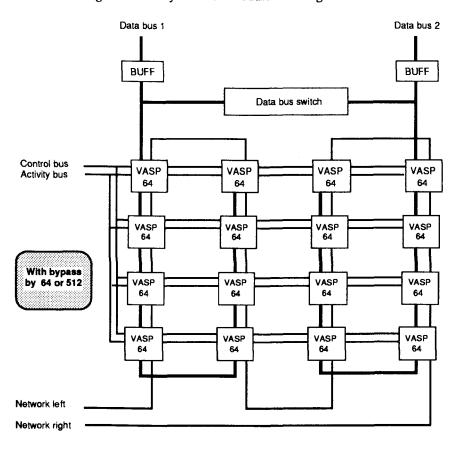

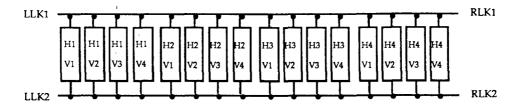

The revised design had two I/O ports which could be configured as  $2 \times 512$  APE substrings or one substring and allows bypass of 64 or 512 APE blocks (see Fig. 6). This revised design was targeted to a standard 184-pin package. In addition to the VASP chips the HASP contained glue buffers and Programmable Array Logic (PAL) devices.

Figure 5 The hybrid ASP module: first organization

Figure 6 The hybrid ASP module: second organization

A thermal analysis of the HASP design had been undertaken. The results showed that a reasonable airflow (1 m per sec) across the surface of the HASP would hold the device junction temperature below 70 °C.

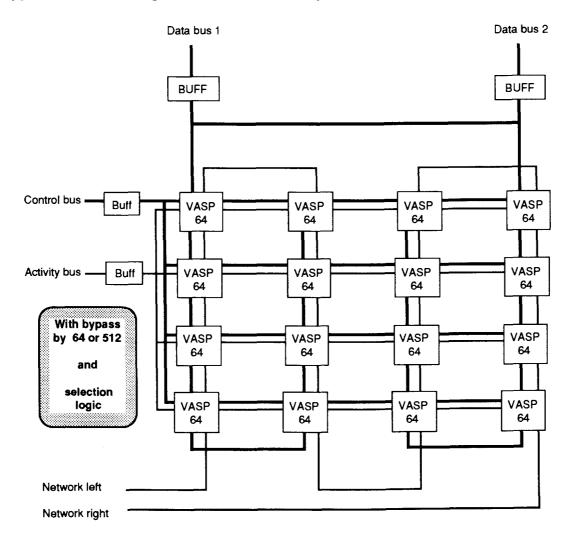

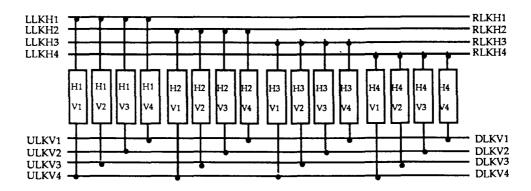

The design was issued to PolyCon, an American hybrid manufacturer, but in December 1991, for internal reasons, PolyCon resigned not far from the target. Then Hughes, which was in charge of the SOS version of the VASP-64, accepted to redesign and to produce the hybrid. Taking advantage of this unfortunate event, this third design used the results of an ASP prototype machine built in the mean time. This new HASP contained 16 VASP-64 chips (1024 APEs) together with two data ports. Each 32-bit data port had bidirectional buffers; the control bus and activity bus were internally buffered. Bypass and selection logic were included in the hybrid (see Fig. 7).

Figure 7 The hybrid ASP module: final organization

Unfortunately, Hughes also failed to manufacture this hybrid. Therefore the collaboration stopped the hybrid studies and concentrated on the discrete chip machine.

#### 3. MACHINE ARCHITECTURE

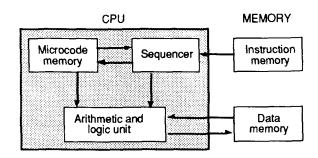

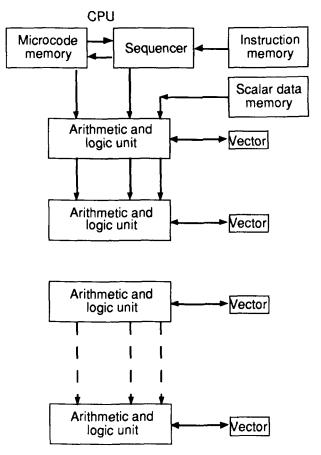

Figure 8 shows the well-known Single Instruction applied to Single Data (SISD) general architecture for a microprogrammed processor. To increase the processing power it is possible to design parallel architectures by using many processing devices (Arithmetic and Logic Unit or ALU) working in parallel on an array of data and leading to a Single Instruction applied to Multiple Data (SIMD) structure (see Fig. 9). In a multi-ALU machine two types of data can be considered, scalar and vector. Each ALU works simultaneously on its own vector data, whereas scalar data is broadcast over all ALUs.

Figure 8 Structure of a microprogrammed processor (SISD)

Figure 9 Structure of a vectorized processor (SIMD)

Some limitations slow down the speed of such a machine. The first bottleneck is the competition to get simultaneously vector data in the main memory; the second problem is to disable parts of the ALU depending on previous results during the processing.

The ASP chip is ideally suited to build SIMD machines in which the ASP string is used as a multi-ALU. The ASP structure avoids some difficulties of a SIMD machine: vector data are distributed and kept in each ALU (APE), access to each APE is an associative process, one can work with a subset of the string driven by the data.

#### 3.1 The ASP machine architecture

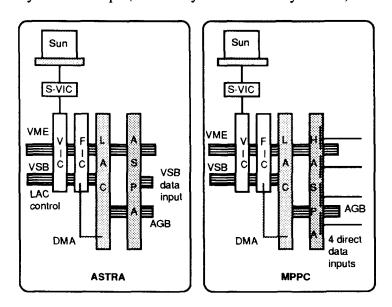

In order to evaluate on real machines the ASP concept for online, real-time applications, the MPPC collaboration worked to design and construct four multipurpose, real-time ASP machines (one for each main partner). Two types of ASP machines were designed, one with the ASPA board (2 K<sup>‡</sup> processors) using individual chips (known as the ASTRA machine), and the other one with the HASPA board (8 K processors) using hybrid modules.

Each machine is built in a pseudo-VME crate using a triple-height eurocard board (see Fig. 10). They are hosted by a UNIX workstation linked to a VME crate through a SVIC 7213 and a VIC 8250 [9], [10]. The VME crate is equipped with a standard VME processor (FIC 8232 [11]), a single-board, low-level controller (LAC) optimized to generate all possible ASP instructions, and one or more VME processing boards containing an array of ASP chips (ASPArray or HASPArray boards).

Figure 10 The ASP machine organization, ASTRA machine left, MPPC machine right.

<sup>&</sup>lt;sup>‡</sup> K is equivalent to 1024.

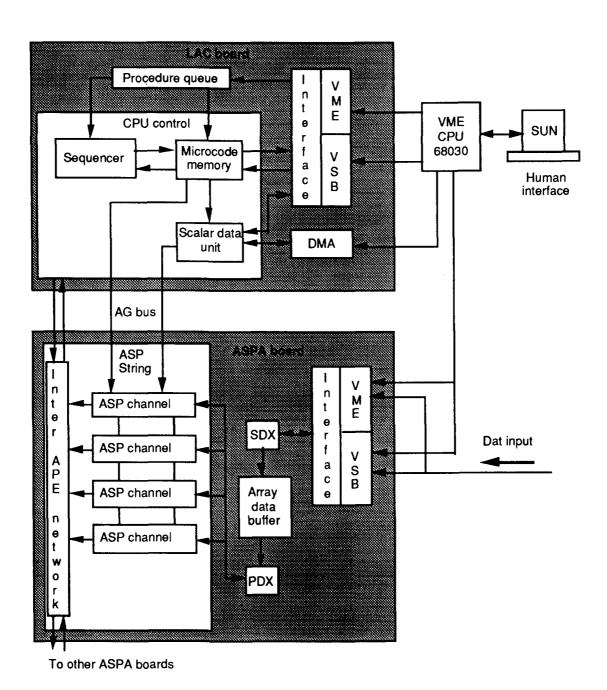

Figure 11 shows the architecture of the ASTRA machine and Picture 1 shows the machine itself working at CERN.

Figure 11 The ASTRA machine architecture

Picture 1. L. Orsini working on the ASTRA (ASPA) machine at CERN. The two extended VME boards, the LAC and the ASPA are clearly identified. Eight ASPA boards can be installed in the VME crate, making a 16K machine.

Picture 2. The LAC board

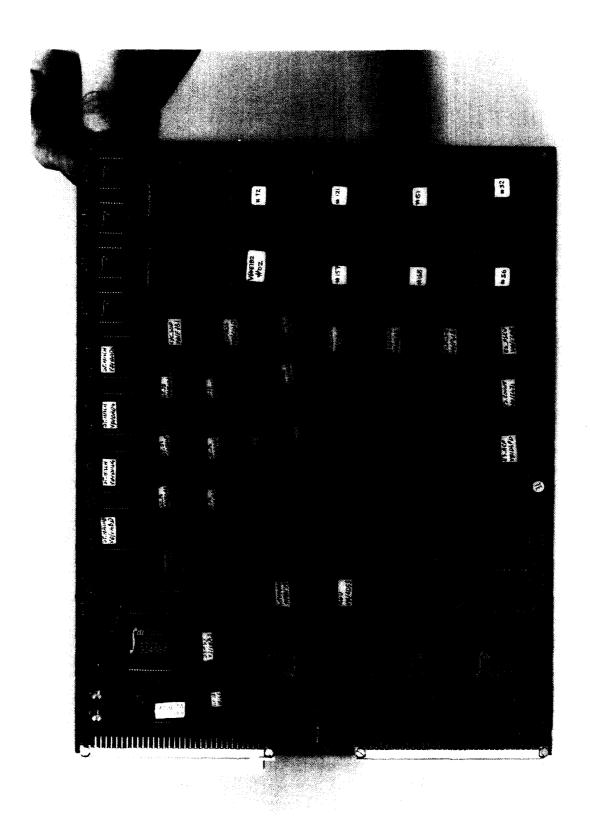

Picture 3. The ASPA board; the 32 VASP-64 chips are easily identified on the right.

Picture 4. The complete ASPEN prototype showing the ASP board (top) and the DSP board (bottom)

Picture 5. A close-up view of the ASPEN interface circuitry; the eight VASP64 ASP chips are clearly identified on the top.

LAC board Procedure queue М Ε VME CPU control Sun CPU 68030 Microcode ٧ Sequencer memory а s Human В interface Scalar data DMA unit AG bus **HASPA** board VME interface ODB control ١ n 2 hybrid ASP t ADB 🖁 Front-end data input 1 0 2 hybrid ASP Front-end data input 2 ADB modules Α Р 2 hybrid ASP Ε ADB Front-end data input 3 modules n θ 2 hybrid ASP ADB Front-end data input 4 t modules W 0 IDB control Synchro **ASP string** To other boards

The architecture of the MPPC machine is shown in Fig. 12.

Figure 12 The MPPC machine architecture

For both machines, the Sun workstation (used as a human interface to the machine) is called a High-Level ASP Controller (HAC) and drives the FIC (a commercial 68030 VME CPU board) called Intermediate-Level ASP Controller (IAC). This FIC drives the ASP machine by three different accesses: VME and VSB busses, and a proprietary fast DMA channel. The ASP machine itself is composed of one Low-Level ASP Control board (LAC) and a maximum of eight ASP Array boards (ASPA or HASPA). The ASP machine must be considered as a vectored coprocessor of the 68030. On the LAC board, the microcode memory stores the algorithm procedures to be executed by the ASP string.

A bidirectional inter-APE network interconnects the LAC and the ASP boards in a double loop. Its purpose is direct communication between APEs; this network works in two modes: shift the content of the APE string over to the next string for comparison, or execute a remote activation of a selected APE.

The ASPA board contains 32 VASP chips (2048 APEs) allowing a machine up to 16K processors maximum. A parallel access to each board can be achieved by a direct connection to the VSB connector on the backplane through a small adaptor card. In this case each connected instrument must act as a master to generate the VSB protocol.

The HASPA board was designed to use the hybrid module described previously (see Fig. 7) which contains 16 dies of VASP-64 circuit. Each HASPA board contains eight HASP modules giving a total of 8192 APEs per board. Each pair of modules has its own Array Data Buffer (ADB) to allow a faster feed for data; four connectors allow the connection of external data acquisition logic. These connectors allow a data input rate of 320 Mbytes per second per board. The ADB memory is a double-port memory large enough to store more than one event so that it can be fed with the next event during the processing of the previous one.

#### 3.2 The ASP global bus

The backbone of the ASP machine is a proprietary bus, the ASP Global bus (AGbus). The communication between the LAC and the ASP array is done by this AGbus on the P3 connector of the extended VME card.

The scalar data are transmitted on 32 lines in the form of a 32-bit binary word or in ternary mode§ in case of bytes or bits. The activity bits use 12 lines and are always transmitted in ternary mode.

The instructions from the LAC are transferred over the AGbus in a compressed form (20 bits). They are expanded inside the ASP boards. The AGbus also carries synchronization signals and status (e.g. match). Four daisy chains are used between boards in the AGbus backplane to implement the inter-APE network.

#### 3.3 The low-level ASP controller (LAC)

The Low-Level ASP Controller (LAC) card provides the environment to execute the ASP application program on one or more associated ASP boards using the AGbus. The LAC is controlled by higher level ASP controllers over its VME and VSB interfaces. A DMA Peripheral Bus (DPB) connects the IAC CPU card to the LAC directly.

<sup>§</sup> Allows the transfer of true, false, and don't care information.

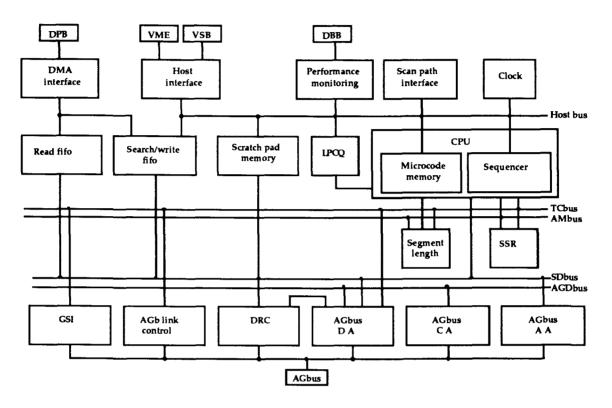

The LAC block-diagram is shown in Fig. 13. The major parts are a CPU formed by a sequencer and a microcode memory to store the LAC operating system and the low-level procedures used in application programs. This Micro Instruction Buffer (MIB) is a 152-bit-wide memory, 64K words deep at the maximum, allowing a subinstruction rate above 40 MHz.

Figure 13 The LAC architecture

The Low-Level Procedure Control Queue (LPCQ) receives commands from the IAC to be executed by the ASP machine. Scalar data can be shifted left or right by the Scalar Shift Register (SSR), and can be stored in a high-speed scratch pad memory and in two fifos, the Search/Write fifo and the Read fifo. The Data Conversion Register (DCR) provides conversion to fit the ASP data representation (bit, byte or word). The AGbus Data Assembler (AGbus DA) assembles data words to be broadcast over the AGbus to ASP boards. The AGbus Control Assembler (AGbus CA) and AGbus Activity Assembler (AGbus AA) assemble a control word and activity bits to be broadcast also to ASP cards. The Global Status Inductor (GSI) interfaces the AGbus to the global status indicator. The AGbus Link Controller provides control and monitoring of the inter-APE network.

Many of these features may be accessed by the host; the host bus connects the host interface to the major parts of the card. Other internal busses interconnect LAC elements. The Test Condition bus (TCbus) connects test condition sources to the branch logic of the sequencer; the Address Modifier bus (AMbus) connects address modifier sources to the

address generation logic of the sequencer. The Scalar Data bus (SDbus) is formed by two 32-bit-wide data busses, the read (SDbus.rd) and the search/write (SDbus.sw) busses. The LAC Data bus (LACDbus), the AG Data bus (AGDbus) and the CTRLbus carry micro-order fields from the micro-program store to functional blocks of the LAC and through them to the AGbus. The scan path bus connects all registers of the board not accessible from the host bus into a serial bus. The performance monitor and the scan path interface allow monitoring and debugging of the machine through the Debug Board Bus (DBB).

The LAC card is a multilayer board with six layers of signal and two layers for ground and Vcc planes. The microcode memory is made in two banks and, using 8K or 32K pin compatible memories, it is possible to obtain 8K, 16K, 32K or 64K size. Most of the glue logic is done with Xilinx PGAs. The realization of the LAC board is shown in Picture 2.

#### 3.4 The ASP boards

The two ASP array boards designed contain either ASP chips (ASPA) or modules (HASPA) and their associated Array Data Buffers (ADBs).

#### 3.4.1 The ASPA card (chips)

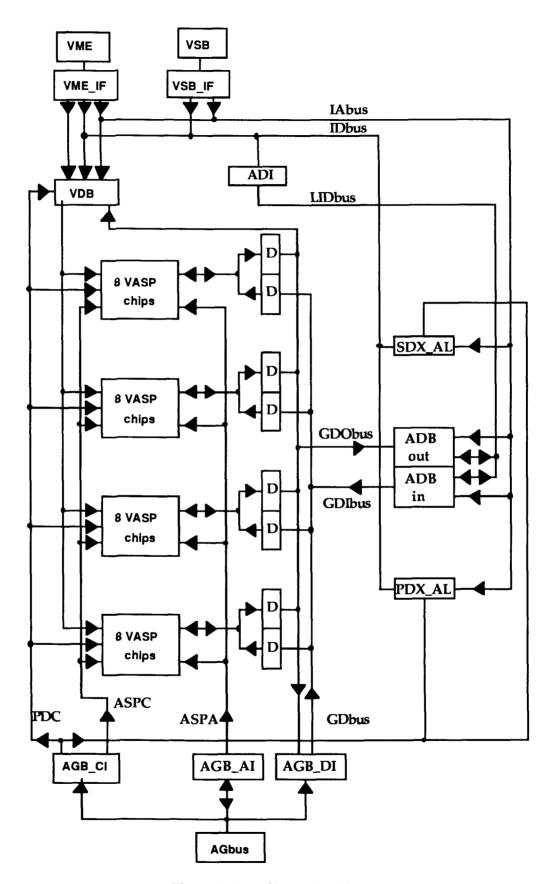

The ASPA card block diagram is shown in Fig. 14 and the realization of the board is shown in Picture 3. The main part is the ASP Array (ASPA) comprising four ASP channels with eight VASP-64 chips per channel to give a total of 2048 APEs. Two sets of look-up memories are used to expand the AGbus instructions into two 16-bit subinstructions sent to the ASP chips and into a 32-bit pattern distributed over the card control bus.

The ADB comprises two dual-ported memory planes, providing one output and one input data channel for the ASP array. Each memory plane is divided into two pages, A and B, which allow simultaneous internal and external access. The ASP communicates with the ADB memory through the Global Data bus (GDbus) formed by two 32-bit-wide busses, the Global Data Input bus (GDIbus) and the Global Data Output bus (GDObus). The Primary Data exchange Address Logic (PDX-AL) generates the ADB addresses on the PDXbus during sequential 32-bit transfer between the ASP array and the ADB. The LAC microprogram may access ADB planes of a selected page for a PDX transfer independent of an SDX operation.

The host through a VME or a VSB interface may access the ADB plane of the other page simultaneously for a Secondary Data exchange (SDX) either in random access or in sequential access. SDX Address Logic (SDX-AL) is responsible for generating ADB addresses during sequential transfer.

Figure 14 The ASPA card architecture

The IDbus is an internal data path for the VME or VSB interface, LIDbus is the internal data bus to input the ADB. Between these two busses, the ASPA Data Interface (ADI) is used to align data in a single byte, word (double byte) or long word (quad byte) for the host access to the ADB, and to perform conversion for the ASP ternary mode. The VASP Debugger (VDB) is a means for the host to monitor the internal state of a selected VASP-64 chip. The content of the selected chip is stored in a dual-port memory which can be subsequently read by the host.

The ASPA card is a multilayer board with six layers of signal and two layers for ground and Vcc planes. Most of the glue logic is done with Xilinx PGAs.

#### 3.4.2 The HASPA card (modules)

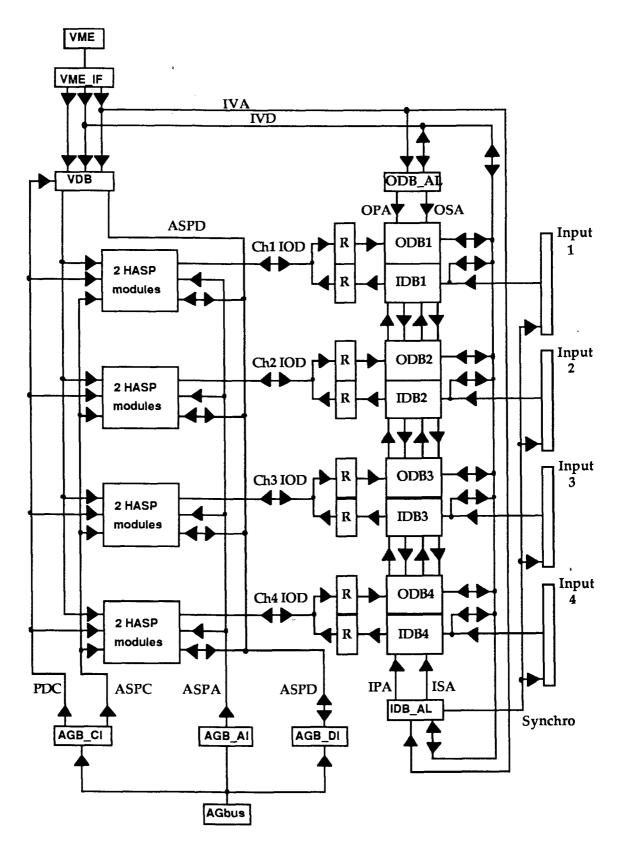

The architecture of the HASPA board is roughly the same as that of the ASPA board but with a number of processors increased by a factor 4 and the implementation of four direct parallel inputs for data transfer.

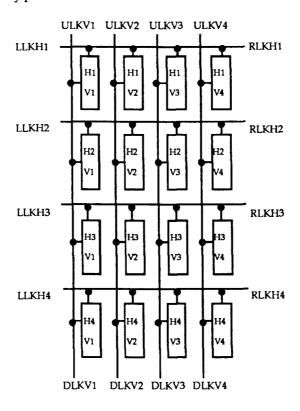

The block diagram is shown in Fig. 15. This board contains eight modules of 1024 APEs working as a string of 8192 APEs. The string is divided into four channels of 2048 APEs, each channel being associated with an ADB buffer. Each channel is the equivalent of an ASPA board.

Each ADB buffer contains two sets of dual-port memory: the Input Data Buffer (IDB) and the Output Data Buffer (ODB). Each IDB and ODB plane is divided into two pages of  $2K \times 32$  bits. For the IDB, one page is connected to two modules. For the ODB, one page is connected to the same two modules and the other page is tied to the VME interface. Such a structure allows the machine to be run in a full pipeline mode: front-end data may be written onto one page of each IDB buffer while other data are read from the other page by the modules; similarly, some results may be written by the modules onto one page of each ODB buffer while other results are collected from the other page via VME. However, it is also possible to keep an instance of the input data in the IDB until these data have been processed by the ASP. This allows the input data to be read back together with the ASP results for selected events. The control of the input data transfers is handled by the Input Data Buffer Address Logic (IDB-AL). When using the four front panel connectors, the protocol is asynchronous. Protocol errors and buffer overflows are detected. Transfers with an unequal number of words in each port are allowed. Similarly, the Output Data Buffer Address Logic (ODB-AL) allows transfers with an unequal number of words from the ASP to the four ODB buffers. This characteristic is of special interest for feature extraction algorithms.

With the exception that the HASPA board is not connected to the VSB bus, all the other elements (communications to the LAC and the VME, VDB debugging logic) are roughly similar to those of the ASPA board.

Figure 15 The HASPA card architecture

The HASPA card consists of two boards: a mother board and a daughter board covering about a third of the main board. Both are multilayer boards with six layers of signal and two layers for ground and Vcc planes. The daughter board contains essentially the direct input connectors, the differential receivers, and the input memory. The IDB-AL and ODB-AL are implemented in two 3090 (100 MHz) Xilinx PGAs.

Unfortunately, owing to the lack of hybrid modules, the two HASPA boards built have been only partially commissioned.

#### 4. THE ASP EMBEDDED NODE (ASPEN)

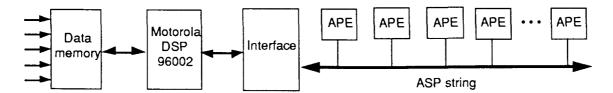

With a view to using the ASP in real-time embedded applications, a software and hardware environment capable of meeting the requirements of future trigger and acquisition systems in terms of response time, scalar processing, and data I/O has been developed at Saclay. This development led to a new machine (ASPEN). In the ASPEN architecture [12], a high-performance, standard microprocessor acts as the ASP controller and scalar processor (see Fig. 16).

Figure 16 The ASPEN architecture

The ASP software execution is supervised by the microprocessor, and the control flow of scalar and vector operations is directed by the microprocessor program execution. The ASP string operates as a co-processor, and can be seen as a parallel-processing accelerator. The ASP program may run in fine synchronization mode, where it receives requests on an instruction-by-instruction basis, or can run in asynchronous mode to execute predefined block procedures. Special rendezvous synchronization points are automatically inserted by the software to exchange data and results between the microprocessor and the ASP. In addition, the ASP vector elements may be seen in the microprocessor memory space as normal variables that may be accessed sequentially or according to dynamic activity criteria.

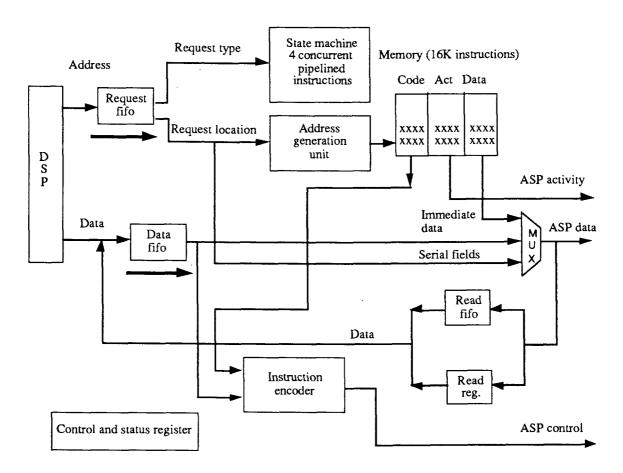

In the first implementation of this architecture, the microprocessor is a high-end, dual-port, floating-point, digital signal processor (Motorola DSP96002). Pictures 4 and 5 show the ASPEN machine which is currently working at Saclay. The first external bus port is dedicated to the ASP interface, while the second port is left free for front-end data interfacing and dialogue with other parts of the system. Figure 17 shows the main elements of the interface.

Figure 17 The ASPEN interface organization

A key element of this interface is a static memory which is loaded with the suboperation codes, the static operands and activity values, either for a single operation or for a block of operations. This memory is seen by the DSP through a fifo as a standard RAM. Addressing a location inside the memory will start the execution of a specific operation: the LSB part of the address will extract information from the memory while the MSB part will indicate the type of cycle to be executed.

The requests sent by the DSP through the fifo are pipelined by four state machines working in parallel in a five-step sequence (see Table 1, cycles m, m+1): Request detection (D), Fetch (F), Analysis (A), Execution (E) and Read (R). When the pipeline is established, the detection step occurs during the read step (Table 1 shows the pipeline progression for a typical sequence of five instructions: V, W, X, Y, Z). This structure maintains the rate of one request for each DSP cycle.

Table 1. The ASPEN pipeline structure of the request

| Cycle | Pipeline level |   |   |   |   |

|-------|----------------|---|---|---|---|

|       | D              | F | A | Е | R |

| m-4   | V              | - | _ | _ | _ |

| m – 3 | W              | V | _ | _ |   |

| m-2   | X              | W | V | _ | _ |

| m-1   | Y              | X | W | V | _ |

| m     |                | Y | X | W | V |

| m + 1 | _              | Z | Y | X | W |

| m + 2 | _              | _ | Z | Y | X |

| m + 3 | _              | _ | _ | Z | Y |

| m + 4 | _              |   |   | _ | Z |

If dynamic scalar data is needed for an operation, it is provided on the DSP data bus through the data fifo. Results are written in the read fifo or directly on the B port of the DSP. A unique request from the DSP may start a block of operations in the ASP string. During the execution of a DSP request by the ASP, the DSP may continue to work unless it has to wait for the ASP result.

This first ASPEN system was simulated, built and successfully tested in a 512 APEs configuration. It has been under continuous operation since October 1992. Two generations of VASP-64 circuits have been used on this machine: ES2 CMOS circuits and Hughes SOS H1-B1 and H1-B2 versions, operating at up to 30 MHz instruction rate.

#### 5. THE ASTRA MACHINE SOFTWARE

This section describes the status of the operating system, based on UNIX, and the programming environment developed for running an application on the ASTRA machine.

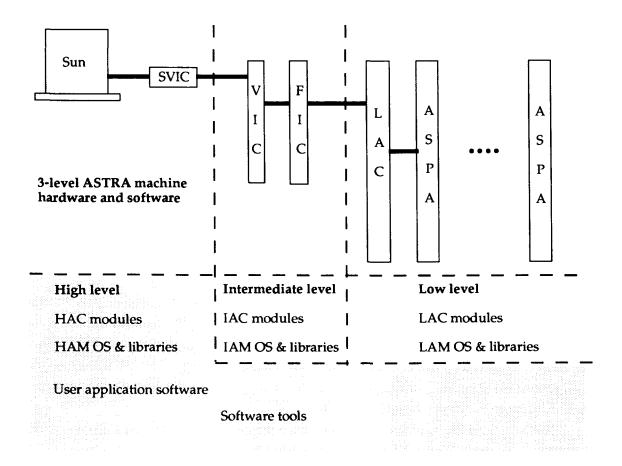

The target machine, as described in the previous sections, consists of several hardware modules. The three independent hardware activities, working jointly, give the idea to present the machine as having three intercommunicating levels: the HAC (High-Level ASP Controller) to refer to the Sun SPARCstation; the IAC (Intermediate-Level ASP Controller) to refer to the FIC8232 (68030 processor); and the LAC (Low-Level ASP Controller, see Section 3.3). The system and application software reflect the three-level hardware of the machine (see Fig. 18).

Figure 18 Three-level software for the CERN ASTRA machine

#### 5.1 Writing an ASTRA application

The ASTRA programmer has to write applications with the three-level architecture of the machine in mind. An ASTRA application requests the programmer to support a software main module for each hardware level of the machine: he has to write the HAC, IAC and LAC modules defining the interfaces between each module. A number of facilities are available in order to write this kind of three-level application.

The main idea is to program each layer using services provided by the lower layer. That is, the HAC part will use the IAC procedures in remote to drive execution on the IAC, and the IAC part will use the LAC procedure in remote to drive execution on the LAC. The system so defined uses a Cross Procedure Call (or Remote Procedure Call) mechanism for control and data communication between each hardware level. The procedures defined in one module and called in a module of a different level are called cross-exported procedures. The way the cross procedure calls are executed is completely transparent to the application programmer.

#### 5.2 Software development tools: the compilers

The language used for writing an ASTRA application is Modula-2 with some restriction for each level. Since the target machine consists of three different hardware modules, three different commercial compilers are used to generate the corresponding target executable code. The three compilers are:

gpm: Garden Points Modula-2 for Sun SPARCstation architecture [13];

ace: The ACE Cross Modula-2 Compiler for MOTOROLA 68030 architecture [14], [15];

lamc: The ASPEX Microsystems Ltd. Cross Compiler for Low-Level ASP Controller [16], [17].

In order to simplify the task of the programmer, a multi-level compiler generator is provided. The programmer has to write the definition and implementation modules for each level. Those modules will be compiled using a program called 'aspc' [18] which drives the execution of the right compiler according to the target level that the module represents. Furthermore, the aspc compiler will generate the necessary code for implementing the cross-exported procedures.

The compiled modules are linked to form a single application program ready to be executed on the three-level hardware components of the machine.

The linker program is called 'aspl'; the aspl links the modules taking into account the three different hardware targets.

#### 5.3 Operating system tools and run-time libraries

The ASTRA operating system assists the user in running a three-level application.

The machine initialization, the target code downloading, the program execution and the cross-communication modules are the tasks of the ASTRA operating system.

A set of run-time libraries is available. These are provided for each level, for cross-procedure call management, for specific instrument resources interface, and for data communication.

These operating system tools are:

- LAC-OS

- IAC-OS

- · HAC device driver

- SVIC-VIC link initialization tools

- LAC and APEA initialization tools (APEA is equivalent to ASPA)

- LAC and IAC downloading tools.

The run-time libraries are:

- · Cross-procedure scheduling, polling and synchronization management

- Shared memory management between HAC and IAC

- · LAC SDB fifos interface

- APEA ADBs interface

- APE debugging tools

- General-purpose LAM libraries.

#### 5.4 ASP documentation

The documentation which is available for ASP allows any beginner to understand the basic concept of ASP, to use the ASP simulator, and to write application programs running on the ASTRA machine. The basic documentation was issued by ASPEX and a number of documents, written by CERN/MPPC, are available to help the non-specialist.

#### 5.4.1 ASPEX documentation

ASPEX Microsystems Ltd. provides a set of basic ASP documentation for the ASTRA machine and for ASP simulation. These documents are:

- A User's Manual of the LAM Compiler [16]

- A LAM Programmer's Reference Manual [17]

- A User's Manual for the ASPC, Version 1.1 and ASPL [18]

- An ASTRA Application Programmer's Reference Manual [19]

- A User's Manual for the VASP-SIM Simulator [20]

- A VASP-SIM Procedure Library User's Manual [21]

- A VASP-SIM Procedure Library User's Manual of the Advanced Arithmetic Package [22].

#### 5.4.2 CERN documentation

In order to help and assist the programmer working on the CERN ASTRA machine, additional documents have been issued by the MPPC Collaboration at CERN. They complete the original ASPEX documentation and are very useful for ASP programming beginners:

• The 'ASP Cook Book' which was written for the ASP beginner in order to present in a simple didactic way the principles of the ASP concept [23];

- The 'ASPA Programming User Guide' which shows in full detail how to start programming an application on the CERN ASTRA machine [24];

- The 'ASPA Installation Guide' presents all the relevant information about the installation of the hardware and software tools of the CERN ASTRA machine and its environment [25].

#### 5.5 Graphics tools

A dedicated graphics interface has been developed at CERN in order to provide a self-explanatory output of the debugging facilities: the contents of each APE can be dumped and visualized in a Sun window at any step of the program. At the moment, it only works when using the simulator installed on the Sun. The implementation of the graphics interface for the ASTRA machine will be a 1993 upgrade of the system. A Modula-2 graphics interface has been implemented for GPM using the OpenWindows 3.0 graphics environment at the HAC level. All these graphics facilities are documented in 'Graphic tools for the ASTRA machine' [26].

All the relevant ASP-CERN documents have been regrouped in the open documentation which is available for the ASTRA users: the CERN-ASPA Machine User's Book [27].

Another important programming help facility was created in 1993 by ASPEX: the ASTRA (ASP System Test-bed for Research and Applications) debugging team which provides the ASTRA programming user with a fast debugging feedback loop [28].

#### 5.6 Other ASTRA programming methods

Two other solutions have been developed for programming the ASTRA machine. In particular, when the ASPA and LAC cards were delivered at CERN, a simple two-level ASTRA-OS was developed using only HAC and LAC, for Modula-2 and C interfaces. This system uses a programming approach similar to the standard three-level operating system. As this system implies a lot of communications between the Sun and the LAC through the S-VIC, producing heavy overheads, it was only considered for development of simple offline applications.

Another system has been developed by LAL-Orsay for a specific, real-time application (see Section 7.1.1). This system puts emphasis on the IAC which is in charge of data I/O. The IAC works under the OS-9 operating system, and the code was written in the C programming language. It makes use of the low-level compiler (lamc) from ASPEX.

### 5.7 An example of applications programming on the ASTRA machines

Two introductory examples for the CERN ASTRA machine are given in the Appendix. Section A.1 gives the basic skeleton of an ASTRA program and Section A.2 shows an example of a complete case-study application program.

#### 5.7 An example of applications programming on the ASTRA machines

Two introductory examples for the CERN ASTRA machine are given in the Appendix. Section A.1 gives the basic skeleton of an ASTRA program and Section A.2 shows an example of a complete case-study application program.

#### 6. A CCD INTERFACE TO ASTRA

In order to be able to test the processing power of the ASP, a large amount of data was require. A CCD camera was found as a rather simple device able to generate this large data file at a suitable rate.

A first VME prototype of a single direct output, transferring the CCD data (pixel by pixel) at a readout speed of 100 ns per pixel, was constructed at CERN. The interface is flexible enough to support various types of CCDs (full-frame or image-memory transfer), even with a different number of pixels for lines and columns.

Besides applications in HEP, the CCD camera linked to the ASTRA machine was used as a data source for testing iconic processing algorithms and as a demonstration platform for the ASTRA machine.

### 6.1 Description of the CCD readout and its interface to the ASTRA machine

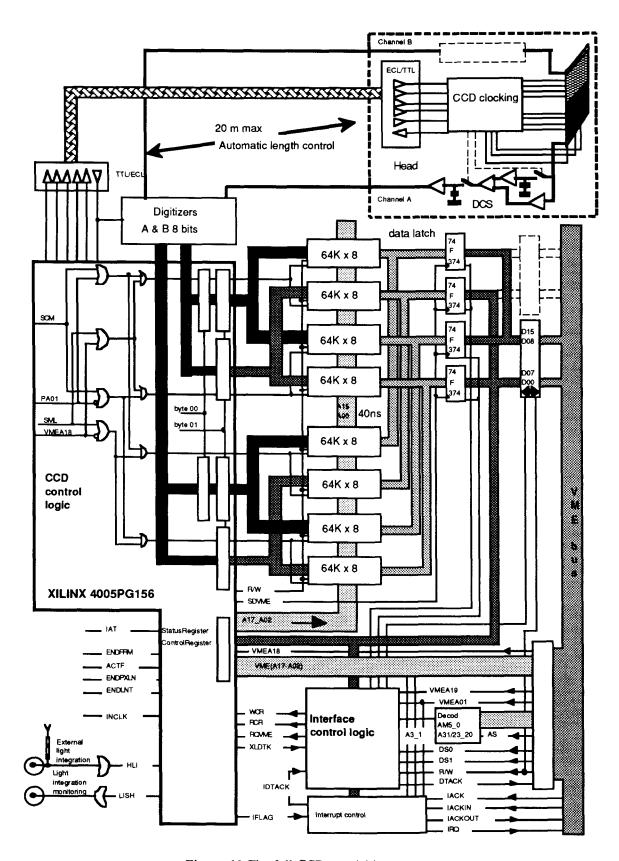

The card is plugged into a VME slot of the ASTRA machine and is controlled by the CPU master of the crate or by the Sun host through a SVIC-VMV-VIC interface (32 bits). Different CCD targets from Thomson-TMS [29] were used: the TH7863 (imagememory CCD;  $384 \times 288$  pixels), the TH7883 (full-frame CCD;  $384 \times 576$  pixels) and the TH7895 (two outputs). The configuration of the CCD data acquisition system built for these CCDs is shown in Fig. 19.

The lines are sequentially transferred to the output register which is read pixel by pixel at the output diffusion. The sequential readout time at 10 MHz is 15 ms for the TH7863 and 30 ms for the TH7883. A pixel cycle is divided into three time slots of 33 ns each: reset, floating, signal. With the double-correlated sampling the analog value of the pixel is stable for ~ 80 ns for 8-bit digitization. The memory is organized in four benches of 64 Kbyte sequentially loaded by the digitized value of successive pixels. It can be read from the VME in 32 bits representing four adjacent pixels.

CCD interfaces were built around a 4005 Xilinx FPGA. Implementation of the hardware in Xilinx FPGAs allows the same card to be configured for full-frame or image-memory CCDs. The card can also be programmed to be used with the HASPA high-speed interface. Free-run or one-shot mode are available for image-memory CCDs.

Figure 19 The full CCD acquisition system

The interface has been enhanced with 512 Kbyte of memory and two analog channels to work with a  $512 \times 512$  pixel, two-output CCD (Thomson TH7895).

A printed circuit board has been designed and is populated with 16 special memory units giving a total of 1088 Kbyte to work with the  $1024 \times 1024$  pixels CCD (TH7896 from Thomson) in two-channel mode. The 10-bit digitization, the on-line pixel correction, and the VSB interface are not yet implemented.

#### 6.2 Test results of the CCD-ASTRA system

The TH7863 CCD linked to the ASTRA machine has been running for a test-bench demonstration. For this purpose, the image as seen by the CCD was stored in the VME memory area and mapped inside the ASP in 2K patches through the DMA channel (8 bits per pixel loaded in each PE). As an example of feature extraction, the patch was then processed using morphological operators for contour outline (edge detection) of the image. For this algorithm, the measured processing time in the ASTRA was 24 µs per patch and is independent of the size of the patch. For this application, the image processing at video rate is clearly achieved.

#### 6.3 A CCD interface for the MPPC machine

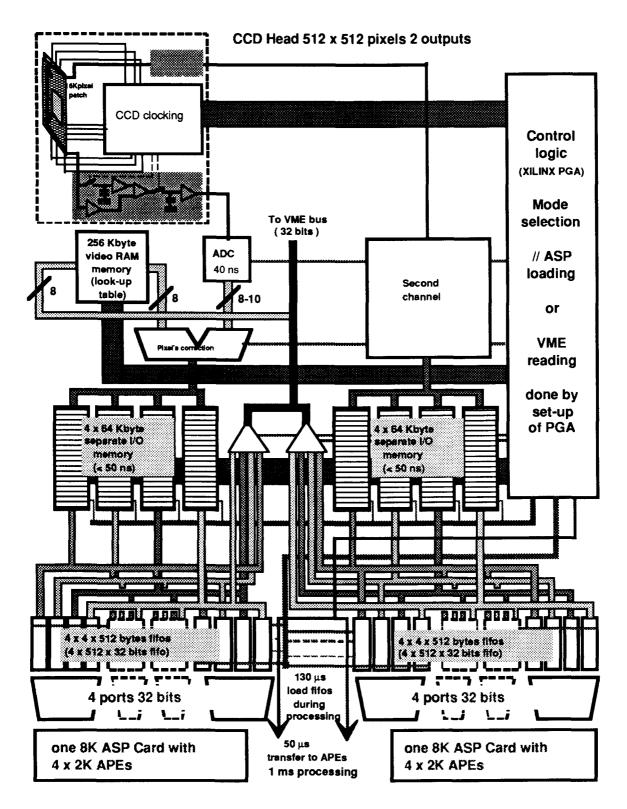

The main interest of the 16K MPPC machine would have been its ability to run complicated algorithms in parallel on a large amount of data, generating a huge processing power. In parallel to the development of the HASPA card a study has been carried out for realizing the CCD-HASPA interface.

The design of the interface between the data source and the machine uses the full parallel I/O capability of the HASPA card. For this purpose, the data are presented in words of 32 bits. Figure 20 gives a block diagram of the interface between the CCD VME card and a two-HASPA-card machine.

The FPGA programming allows various patterns of rectangular patches smaller than or equal to 16K pixels to be processed. The transfer time, including all overheads mainly due to the patch pattern preparation in the FPGA, must be smaller than the image patch processing time. The 32 fifos of 512 bytes can be loaded in less than 250  $\mu$ s, the transfer from fifos to APEs needs 50  $\mu$ s, and the process time for a typical image was estimated by simulation to be ~ 1 ms.

With the 16K machine, a 256K pixel frame could be processed in 16 ms, which is fast enough for handling online, video-rate image processing.

It is worth pointing out again that the processing time does not depend on the image size, provided the number of APEs be enough to accommodate all the pixels.

Figure 20 The two-output CCD (512 × 512 pixels) interface for the 16K MPPC machine

#### 7. APPLICATIONS

During the course of the MPPC project, all partners studied, according to their individual motivation, a large variety of ASP applications. Almost all of these applications arise in the context of preparatory work for the future Large Hadron Collider for triggering physics events.

The generally accepted trigger structure, borne out by physics simulations, is the following: after a reduction of the initial event rate of 40 MHz by a custom-made, possibly analog, first-level trigger, relying on calorimeter windows and muon identification, the event passing rate is of the order of ~ 100 kHz. At this rate, reduction 'algorithms' of some complexity will be required to reduce rates further. They are based on data from the first-level trigger and on additional local detector data that may be extracted from some buffering device or intercepted 'on the fly' as data pass from one system part to the next, e.g. as they are pushed from geographically spread front-end pipelines to data concentrators.

At the beginning of the project, before the first ASP compact machine became available, the only way of studying parallel algorithms was to run simulations on a VASP simulator supplied by ASPEX.

#### 7.1 Application studies on a VASP simulator

Timing results given by the VASP simulator working on a Sun station are based on the assumption that the ASP machine could work with a 25 ns time slot for sub-instructions.

#### 7.1.1 Tracking and calorimetry for the SDC level-2 trigger

The first study of the second-level trigger of the SDC detector was made at Saclay on the VASP simulator to get an idea of the feasibility. The architecture of the trigger was later updated. However, this study gave a lot of information about the timing and the way to program this kind of algorithm.

A complete program was developed and run on the VASP simulator for an architecture based on the idea of two ASP machines working in parallel: the first one analyses the data coming from the tracking, and the second one the data coming from the calorimetry, each detector using its own granularity (see Fig. 21). The decision is taken at the end by comparing the transverse momentum from the tracking with the energy from the calorimetry.

Figure 21 The SDC level-2 tracking and calorimetry trigger

The tracking algorithms should identify muons, electrons, photons and hadrons using the tracks in the detectors: this confirms or not the results of the level-1 trigger. The event will be killed if no particles are detected, stored if the number of particles is greater than five, otherwise, for a number of particles from one to five, a comparison is done with the calorimetry results.

The analysis of the energy deposited in the various parts of the calorimeter allows the identification of electrons, photons, hadrons, or jets. This is followed by a cut on the energy level of the identified particle. Each particle is treated by an algorithm using summation of energy in the neighbouring region. The final decision depends on the number of particles identified.

All these algorithms have been tested on the VASP simulator. The processing time for the different configurations has been estimated. For example, the determination of two electrons needs 22  $\mu$ s, 1 gamma + 1 hadron needs 29  $\mu$ s; a library of procedures useful for the algorithms allows more tests and investigations to be done easily.

These results were found to be very encouraging and new studies have been started to improve performances (see Section 7.2.2).

#### 7.1.2 The LHC high-transverse-momentum muon second-level trigger

At the Large Hadron Collider (LHC) the high luminosity  $(4 \times 10^{34} \text{ cm}^{-2} \text{ s}^{-1})$  will create a severe environment for the detectors, making physics discoveries a difficult challenge.

The most promising particles for TeV physics, which could be used to trigger interesting events, are the relatively rare high p<sub>t</sub> (transverse-momentum) muons which remain after filtering out all the other unwanted charged particles. A first challenging goal is to discover the Higgs particle through its decay into four muons.

In the most optimistic phase of the first-generation detector design, accepting Monte Carlo simulation predictions at face value, the general opinion tends to minimize the need for a second-level trigger decision. The main argument put forward is as follows: using a simple first-level decision on the p<sub>t</sub> muon threshold adjusted at a sufficiently high value, the trigger rate could be tuned down directly to the value required by the level-3 trigger (kHz range).

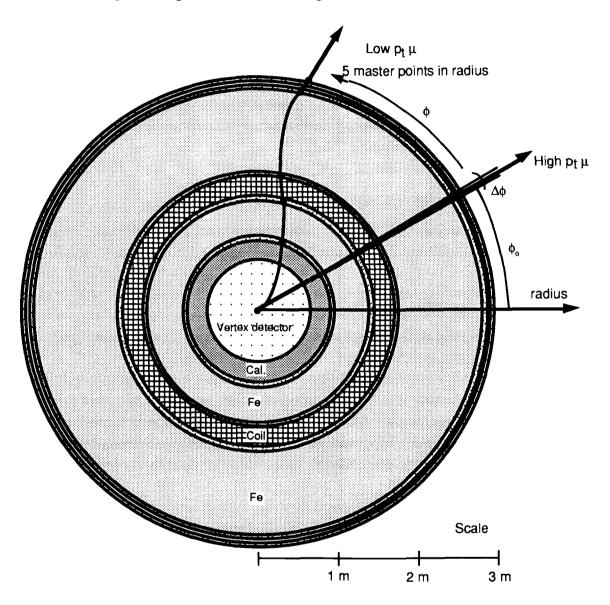

However, physicists must be prepared for many eventualities: the background rates may be underestimated, or one needs for the physics search to run p<sub>t</sub> muons at a lower threshold, or the binary yes/no p<sub>t</sub> muon information coming from the first-level trigger is not sufficient as a signature for the high p<sub>t</sub> muons, etc. This is why a detector model (see Fig. 22), optimized for a second-level muon trigger for LHC [30], was studied and simulated using the ASP architecture. Owing to its inherent parallelism, the proposed algorithm automatically provides multimuon information if there is any, assigning to each muon the charge sign and momentum.

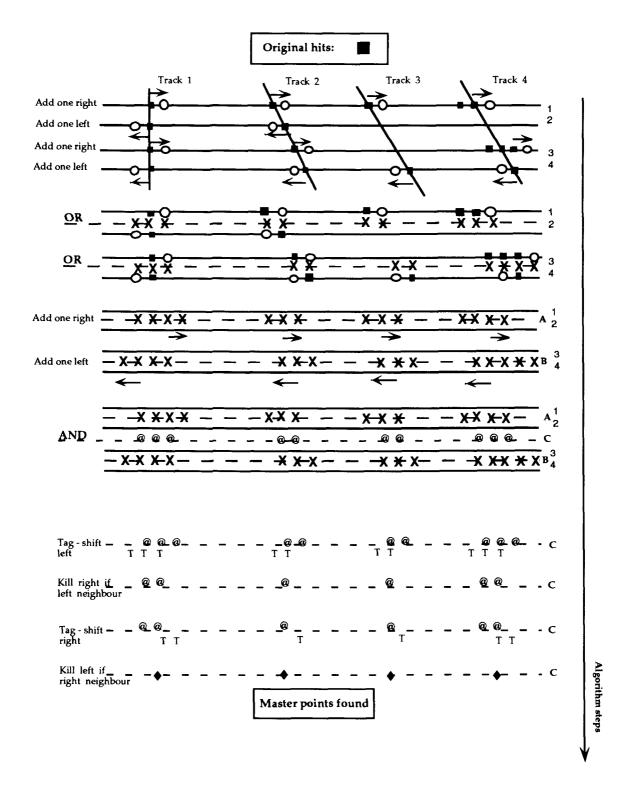

The proposed second-level-trigger ASP procedure has three phases: the loading (detector mapping into the ASP), the preprocessing (master-point determination of the muon hits) and the tracking (based on a pt dependent track-code search algorithm).

In the simulation we assumed five superlayers with four detector layers in each [Ref. 3, p. 69]. In the loading phase, providing a parallel feed into the ASP substrings, one can perform within 5  $\mu$ s the 'iconic bit-mapping' of wire hits to the memory cells of the associative processing elements of the string.

Figure 22 The LHC muon tracking modelling

In the preprocessing phase one performs an 'iconic averaging' of hits in order to calculate the master-point coordinates (see Fig. 23). This algorithm takes into account the chamber inefficiency (no hits in some layers) and the possibility of multiple hits in the same detector layer (the passage of a given particle can produce double or even multiple hits).

Track 1: Ideal straight track, full efficiency Track 2: Inclined track, full efficiency Track 3: Inclined track with 2 missing hits

Track 4: Inclined track with multi-hits and a missing hit

Figure 23 The 'iconic average' algorithm, illustrated for typical muon track signals

The overall efficiency of this algorithm to get all five master-points belonging to a given track is 97.5%, assuming a realistic chamber efficiency of 95%. The processing time is close to  $5 \mu s$ .

The tracking phase provides the sign and a momentum estimate for all the master-point sets which coincide with any of the predetermined  $p_t$  muon track-code combinations. The search for all particles is performed in parallel along the track-code list. The reference ordered list, in decreasing  $p_t$  values, of valid track-codes is precalculated by Monte Carlo simulation.

The number of valid track-codes above a given threshold depends on the  $\phi$  coordinate binning. The effective  $\Delta$ - $\phi$  granularity of the 'iconic mapping' is dictated by the size of the multiple Coulomb-scattering at the selected momentum threshold. Accepting this value as a guideline one can limit the necessary number of track-codes to below 100, which ensures the execution time within 10  $\mu$ s.

In most of the first-level triggers there will be no match, thus the procedure is finished in total within  $20 \,\mu s$ . For the lucky cases, of course, the third-level processing will start. Part of this subsequent procedure—multiplicity, muon sign analysis, etc. can already be executed in the ASP itself by correlating the successful track-code matches.

## 7.1.3 The transition radiation tracking (TRT) detector for LHC. Simulations for applications of ASP modules for a 100 kHz trigger

This study arose in the context of the preparatory work for LHC and was done as part of the RD11 (EAST) project, as one possible implementation of second-level triggers [31].

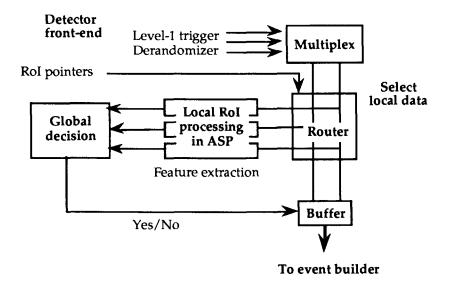

In this architecture, it is assumed that first-level trigger results and additional local detector data are pushed from selected regions of interest of the detector space to the processing machine under assessment through dedicated data routers. External hardware, namely local buffers and the first-level trigger, sends control signals and local data, selected in a region of interest (RoI), into the architecture in question.

This is usually described as a 'push' architecture, as opposed to a readout in which the device executing the algorithm also manages the readout ('pull' architecture).

#### 7.1.3.1 Feature extraction

The investigations on the basis of the ASP architecture were limited to the 'feature extraction' part of these algorithms, i.e. to the task of converting raw front-end-formatted data to quantities ('features') meaningful from the physics point of view. Features are interesting in restricted areas of individual subdetectors only, and the task of feature extraction is not unlike image processing tasks. Feature extraction can in a natural way make use of multiple devices operating in parallel, on different RoIs, and for different subdetectors.

The work on ASP was part of a systematic study of possible architectural solutions for two feature-extraction tasks. These were defined as characteristic second-level trigger tasks in terms of physics goals, detectors, and triggering algorithms, and with fixed assumptions about detector and first-level trigger electronics. Benchmark implementations of such algorithms were done on seven competing architectures, on available hardware where possible, by detailed simulation otherwise. Conclusions about the ASP must be seen in the context of this comparative study.

Both algorithm definitions were the result of close collaboration with R&D projects (RD1 and RD6) pursuing the corresponding detector developments. The algorithms, or rather the problems together with a possible algorithmic solution, are defined in internal EAST notes [32]. The pilot tasks and algorithms reflect a certain state of detector development, frozen for our purpose. Both algorithms have the objective of optimizing the retention of electrons (signal) and the rejection of QCD jets or other phenomena misjudged in the first-level trigger (background).

#### 7.1.3.2 Benchmark definition

The physics features extracted from fine-grain local data in multiple detector windows have to be combined later into global decisions by correlating data from different subdetectors and RoIs. This global decision has not been addressed with ASP in mind, as a different parallelism will be at work, and high-level programmability will be postulated in order to evolve algorithms reliably with the improved physics and detector understanding.

Feature extraction will also have to be preceded by a 'router', which extracts the RoI data and formats them for the feature extraction device. The embedding is shown in Fig. 24.

Figure 24 The router

Very briefly, the pilot tasks are as follows:

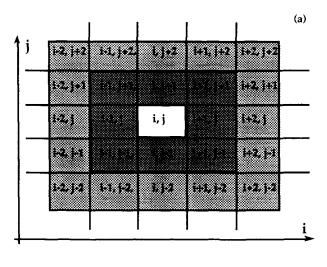

- a calorimeter algorithm for a RoI of 16 × 16 towers. Each tower of our calorimeter is subdivided into 2 × 2 electromagnetic cells, one hadronic and one mixed (wedge-shaped) cell. Each cell is defined by its energy, a quantity known to a precision of 12 or more bits (gray value). In our simulation the RoI of 256 towers corresponds to Δη × Δφ = 0.5 × 0.5, in physical space. The objective of the algorithm is to find features, i.e. decision variables suitable for distinguishing electrons from pions or from hadronic jets, or even pions from jets. Inside the RoI, a near-circular region has first to be defined in which the peak energy deposition is fully contained (cluster area). The second moment of the cluster radius in two dimensions, or energy sums in different ring-shaped zones and longitudinal volumes of fine granularity, have to be calculated over the cluster area since these variables best distinguish electrons from other background phenomena. They are likely to contain all relevant information for electron/pion/jet discrimination that cannot be explored in a first-level algorithm. They also allow improvement of the positional resolution inside the RoI.

- a tracking algorithm based on a straw geometry as pursued in the RD6 project (transition radiation tracker or TRT), operating in a magnetic field. In the projection natural for the TRT, i.e. in the z/φ plane, which corresponds closely to the readout coordinates straw/plane number, tracks appear as straight lines, with the slope dφ/dz corresponding to pt, the position along φ indicating azimuth, and start and end point crudely indicative for z.

The input data appear as an  $80 \times 240$  image, with each pixel taking the value 0, 1, or 3. The algorithm then recognizes patterns of digitizing that correspond to high-momentum tracks, taking into account the pulse-height distribution of digitizing for identification of electrons. The algorithm consists either of making histograms along z (the simplest being without a result for  $p_t$ ), or along roads of different  $d\phi/dz$  (with an indication of  $p_t$ ).

For both pilot tasks, the algorithms were simple enough to be reprogrammed or even hardware-implemented depending on the architecture to be studied. For a clear definition, algorithms were given in a high-level language, but some freedom was left so that equivalent but different algorithms were considered acceptable. Data sets for testing were provided. They contained data values inside RoIs, for signal and background collisions, at different levels of luminosity (minimum-bias background).

#### 7.1.3.3 Benchmark results

The benchmark results were published in Ref. [33]. The comparisons as presented in the following tabular form are, of course, an oversimplification. More detailed discussions than can be exposed here are given in several internal EAST notes [34]. The ASP results were obtained using the proprietary ASP simulator, assuming a clock

frequency of 20 MHz. The ASP execution times (see Table 2) came out best amongst the SIMD machines studied, but did not quite match the expected 100 kHz rate. Several pipeline implementations did, however, achieve this goal.

Table 2. Benchmark results

| Architecture / algorithm studied | Measured (best possible) execution time | Latency estimate | Comment                          |

|----------------------------------|-----------------------------------------|------------------|----------------------------------|

|                                  | (µs)                                    | (µs)             |                                  |

| ASP/TRT                          | 33.5 (9.5)                              | 50.0 (25.5)      | 10 (2) systems of 2048 APEs each |

| ASP/Calorimeter                  | 20.6                                    | Not available    | 5 systems of ≤ 2048 APEs         |

#### 7.1.3.4 Discussion of the ASP implementation

For the TRT algorithm, local pre-histogramming along z (a look-up table reducing every 16 bits along z into a 4-bit count) was assumed to be done outside the ASP. The information loss related to this packing operation is local, and does not preclude the subsequent histogramming at different slopes  $d\phi/dz$ . Apart from increased time for data transmission, histogramming with unpacked data increases the execution time to 46  $\mu$ s. For the calorimeter, the algorithm implemented uses different test statistics from most other implementations, but has been shown to be qualitatively equivalent. It is based on applying thresholds to six different energy sums (central peak, near-neighbourhood ring, wider neighbourhood for both electromagnetic and hadronic energy), i.e. on simple convolutions. The widest areas considered are  $6 \times 6$  towers; the window slides dynamically over all possible positions in the RoI. The resolution for some energies is refined to the electromagnetic tower size, i.e. a fourfold number of cells is considered.

Implementation details: different slopes were done in parallel, in independent ASP substrings. This assumes a parallel data copy into several identical ASP systems of 2048 APEs each. For the calorimeter, the six sums (= convolutions) are done in parallel in five independent ASP strings, with different precision used in the sums. The total number of APEs is 6400, the largest substring is 2048. Here, too, data have to be replicated into multiple strings/APEs, to achieve efficient execution.

The timings given are for the board design of MPPC, ignoring the data duplication and the input bottleneck related to the existence of a single 32-bit-25 MHz channel for 2048 processors. The 'best time' (TRT) assumes only very crude histogramming along z, or tracks that span no more than three bins in φ. For the calorimeter algorithm, the logical connection between the results of the individual convolutions is not included in the timing. A separate timing has been performed for a TRT algorithm including the router

function. The router is a data reformatting unit necessary to present to the second-level trigger architecture a RoI in a suitable and invariable data order, independent of the modularity and readout order of the detector front-end electronics. In the present TRT prototype, the router also reduces the information from three bunch crossings into a single two-bit signal for each straw. The additional time for logical connection of time slices and data interleaving is 5  $\mu$ s. The factor of 3 in required bandwidth would, obviously, constitute an increased I/O challenge to the ASP design.

In contrast with the conventional benchmarking of mainframe computer systems, which typically use very large application programs in a high-level language ('dusty decks'), compiler performance or adherence to portability standards was not part of our evaluation criteria. The main criteria for this real-time benchmark were:

- algorithm execution time, separated into the two aspects decision time (the time interval between successive decisions) and latency (time interval for a given event between start of data input and output of results): this assesses the overall feasibility of a given architecture to contribute as a second-level trigger device. Target numbers are 100 kHz for frequency, and of the order of 1 ms for the maximum latency of the entire level-2 system;

- practical solutions to the high bandwidth input: this addresses a typical bottleneck for many commercial systems which are targeted at compute-intensive problems, and also challenges the flexibility of architectures or their manufacturers in interfacing to specific user constraints;

- possible constraints on the order of input data; this aspect is relevant as we deal with architectures that typically achieve performance by high parallelism with distributed memory, or by pipelining data in a certain sequence. We assess here how much of the data selection (the router is shown in Fig. 24) has to be loaded with tasks that in a general-purpose device would be part of the algorithm itself;

- interfacing to a high-level decision-making unit and to the (physicist) user. The

critical parameters in assessing the embedding difficulties of an architecture are

flexibility with respect to algorithm parametrization, and the hardware

possibilities of passing results (physics features) to a global device for overall

decision making.

For this particular application, the ASP implementation has, in fact, put quite severe constraints on the order of data, has left the input bandwidth and the data replication problems unsolved in its existing hardware, and has not addressed 100 kHz communication of features with a workstation-type processor (64-byte packets).

#### 7.1.4 Image coding applications

This particular application of ASP was studied at EPFL in the Laboratoire de Traitement des Signaux, led by Professor M. Kunt.