Fakultät für Elektrotechnik und Informationstechnik Lehrstuhl für Entwurfsautomatisierung Univ. Prof. Dr. -Ing. Ulf Schlichtmann

## **PhD-Thesis**

## A New Assertion Language Covering Multiple Levels of Abstraction

Volkan Esen

Lehrstuhl für Entwurfsautomatisierung der Technischen Universität München

### A New Assertion Language Covering Multiple Levels of Abstraction

#### Volkan Esen

Vollständiger Abdruck der von der Fakultät für Elektrotechnik und Informationstechnik der Technischen Universität München zur Erlangung des akademischen Grades eines

#### **Doktor-Ingenieurs**

genehmigten Dissertation.

Vorsitzender: Univ.-Prof. Dr.-Ing. Wolfgang Utschick

Prüfer der Dissertation:

- 1. Hon.-Prof. Dr.-Ing. Wolfgang Ecker

- 2. Univ.-Prof. Dr. rer. nat. Franz J. Rammig, Universität Paderborn

Die Dissertation wurde am 14.01.2008 bei der Technischen Universität München eingereicht und durch die Fakultät für Elektrotechnik und Informationstechnik am 29.05.2008 angenommen.

#### PhD-Thesis

Institute of Electronic Design Automation Univ. Prof. Dr. -Ing. Ulf Schlichtmann Department of Electrical and Information Technology, Technische Universität München

in Cooperation with

Infineon Technologies AG Munich IFAG COM BTS MT SD Dr. -Ing. Matthias Bauer Prof. Dr. -Ing. Wolfgang Ecker

Author: Volkan Esen

## Zusammenfassung

Im Rahmen dieser Arbeit wurde eine neue Assertionsprache und Verifikationsumgebung entwickelt, welche die Spezifizierung und Validierung von temporalen Modelleigenschaften über Abstraktionsebenen hinweg ermöglicht. Die Entwicklung der Sprache ist notwendig weil existierende Assertionsprachen die Anwendung auf nicht synthetisierbare abstrakte Modelle nur eingeschränkt ermöglichen. Die formale Semantik der Sprache wurde durch die Abbildung auf ein abstraktes gefärbtes Petrinetz definiert. Die vorteilhafte Anwendbarkeit der Sprache wurde durch einen Compiler und einen speziellen Assertionkernel in mehreren Anwendungen nachgewiesen.

## Abstract

In this work, a new assertion language and verification framework has been developed. It enables the specification and validation of temporal properties accross different abstraction levels. This new language is required because existing assertion languages do only offer limited support for the verification of abstract, nonsynthesizable models. The semantics of the language is defined by a mapping onto a high-level colored petri net. The advantageous applicability of this language has been shown over several applications by using a compiler-based framework and a specific assertion kernel.

## Acknowledgment

This work was accomplished during my affiliation with Infineon Technologies AG - at the department IFAG COM BTS MT SD, headed by Dr. Matthias Bauer - in cooperation with Technische Universität München at the department Electrical Engineering and Information Technology at the institute for Electronic Design Automation, led by Professor Ulf Schlichtmann. I want to thank Professor Ulf Schlichtmann for giving me the opportunity to conduct this thesis at his institute. Also I want to thank Dr. Matthias Bauer and our team for a great collaboration.

I especially want to thank my doctoral advisor Professor Wolfgang Ecker and Infineon Technologies for making this thesis possible. Wolfgang Ecker always pushed me to go beyond my limits being a great mentor. We had many fruitful discussions and brain storming sessions which were vital to the success of this work.

Furthermore, I want to thank Professor Franz Rammig for being the co-advisor of this work.

I am also grateful to Professor Manfred Glesner and Dr. Thomas Hollstein from Technische Universität Darmstadt at the institute of Microelectronic Systems for their continued support after my graduation from university.

It takes a huge amount of patience, perseverance, and most of all support to accomplish a doctoral thesis. Therefore, I want to express my deepest gratitude to Elnura, my beloved wife. She supported me in all possible ways, bearing the many hours I had to stay away to develop the ideas introduced in this work.

I also want to thank my family. They made it possible for me to come this far. Without their great support and dedication none of this would have been possible.

Besides my family, I also want to thank my dear friend Michael Velten who joined me even through nights to write most of the publications on the topic of this work and managed to keep me calm as the deadlines came closer. Also, I want to thank all my other friends whom I had to put off for so many times in the past years.

Volkan Esen Munich, June 26, 2008

## Contents

| 1 | Intr         | oductio        | on                                                   | 1                                    |  |  |  |

|---|--------------|----------------|------------------------------------------------------|--------------------------------------|--|--|--|

|   | 1.1          | The U          | Jbiquity of Embedded Systems                         | 1                                    |  |  |  |

|   | 1.2          | Syster         | em Complexity                                        |                                      |  |  |  |

|   | 1.3          | The R          | Role of Verification                                 | 4                                    |  |  |  |

|   |              | 1.3.1          | Formal Verification                                  | 5                                    |  |  |  |

|   |              | 1.3.2          | Semi-Formal Verification                             | 5                                    |  |  |  |

|   |              | 1.3.3          | Simulation Based Methods                             | 6                                    |  |  |  |

|   |              | 1.3.4          | Emulation / Rapid Prototyping                        | 8                                    |  |  |  |

|   |              | 1.3.5          | Post-Silicon Validation                              | 8                                    |  |  |  |

|   | 1.4          | Motiv          | ation                                                | 9                                    |  |  |  |

|   | 1.5          | Outlir         | ne                                                   | 10                                   |  |  |  |

| 2 | Pro          | blem S         | tatement and Targeted Approach                       | 11                                   |  |  |  |

|   | 2.1          |                | odeling and Design                                   | 11                                   |  |  |  |

|   | 2.2          |                | odeling Impact to ABV                                | 12                                   |  |  |  |

|   |              | 2.2.1          | The Notion of Temporal Behavior                      | 13                                   |  |  |  |

|   |              | 2.2.2          | Scope of TL Assertions                               | 13                                   |  |  |  |

|   |              | 2.2.3          | Communication Patterns and Pipelining                | 14                                   |  |  |  |

|   | 2.3          | Taken          | Approach                                             | 14                                   |  |  |  |

| 2 | D.           |                |                                                      | 16                                   |  |  |  |

| 3 |              |                | ents and Objectives for Transaction Level Assertions | <b>15</b><br>15                      |  |  |  |

|   | $3.1 \\ 3.2$ | 1 1            |                                                      |                                      |  |  |  |

|   | 3.2          | 3.2.1          | acteristics of SystemC Transaction Level Modeling    | $\begin{array}{c} 17\\17\end{array}$ |  |  |  |

|   |              | 3.2.1<br>3.2.2 | Hierarchy                                            | 17                                   |  |  |  |

|   |              | 3.2.2<br>3.2.3 | Concurrency                                          | $\frac{10}{20}$                      |  |  |  |

|   |              | 3.2.3<br>3.2.4 | Synchronization                                      | $\frac{20}{20}$                      |  |  |  |

|   |              | 3.2.4<br>3.2.5 | Abstraction Levels                                   | $\frac{20}{21}$                      |  |  |  |

|   |              | 3.2.0<br>3.2.6 |                                                      | $\frac{21}{22}$                      |  |  |  |

|   | 3.3          |                | Design States                                        | $\frac{22}{22}$                      |  |  |  |

|   | J.J          | 3.3.1          | Temporal Behavior of PV Models                       | $\frac{22}{23}$                      |  |  |  |

|   |              | 3.3.1<br>3.3.2 | -                                                    | $\frac{23}{24}$                      |  |  |  |

|   |              | 3.3.2<br>3.3.3 | Temporal Behavior of PVT Models                      |                                      |  |  |  |

|   |              |                | Temporal Behavior of CA                              | 25<br>25                             |  |  |  |

|   |              | 3.3.4          | Temporal Behavior of CC / RTL Models                 | 25                                   |  |  |  |

|   | 3.4  | Sampl    | $\log \ldots 26$ |  |  |  |  |  |

|---|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|   | 3.5  | -        | Dependent Temporal Behavior                                                                                                             |  |  |  |  |  |

|   | 3.6  |          | action Detection $\ldots \ldots 27$                        |  |  |  |  |  |

|   | 3.7  |          | st/Response Communication Patterns                                                                                                      |  |  |  |  |  |

|   |      | 3.7.1    | Retransmissions of Requests                                                                                                             |  |  |  |  |  |

|   |      | 3.7.2    | Pipelined Requests                                                                                                                      |  |  |  |  |  |

|   | 3.8  | Gener    | al Aspects                                                                                                                              |  |  |  |  |  |

| 4 | Stat | te-of-th | ne-Art and Related Work 29                                                                                                              |  |  |  |  |  |

|   | 4.1  | State-   | of-the-Art $\ldots$ $\ldots$ $\ldots$ $29$                                                                                              |  |  |  |  |  |

|   |      | 4.1.1    | Library Based Approaches to RTL ABV                                                                                                     |  |  |  |  |  |

|   |      | 4.1.2    | Language Based Approaches to RTL ABV                                                                                                    |  |  |  |  |  |

|   |      | 4.1.3    | Applicability of PSL and SVA to TL Modeling                                                                                             |  |  |  |  |  |

|   |      | 4.1.4    | Transaction Level Verification                                                                                                          |  |  |  |  |  |

|   | 4.2  | Relate   | ed Work                                                                                                                                 |  |  |  |  |  |

|   |      | 4.2.1    | RTL Assertions in SystemC                                                                                                               |  |  |  |  |  |

|   |      | 4.2.2    | Transaction Level Assertion Approaches                                                                                                  |  |  |  |  |  |

| 5 | Univ | versal A | Assertion Language (UAL) 45                                                                                                             |  |  |  |  |  |

|   | 5.1  |          | iew of UAL Concepts                                                                                                                     |  |  |  |  |  |

|   | 5.2  |          | ing Layer                                                                                                                               |  |  |  |  |  |

|   |      | 5.2.1    | Ports Section                                                                                                                           |  |  |  |  |  |

|   |      | 5.2.2    | Constants Section                                                                                                                       |  |  |  |  |  |

|   |      | 5.2.3    | Sequences/Properties/Verification Sections                                                                                              |  |  |  |  |  |

|   | 5.3  | Verific  | eation Layer $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 53                                                          |  |  |  |  |  |

|   | 5.4  |          |                                                                                                                                         |  |  |  |  |  |

|   |      | 5.4.1    | Implication Properties                                                                                                                  |  |  |  |  |  |

|   |      | 5.4.2    | Single Sequence Properties                                                                                                              |  |  |  |  |  |

|   |      | 5.4.3    | Property Evaluation Modes                                                                                                               |  |  |  |  |  |

|   | 5.5  | Seque    | nce Layer                                                                                                                               |  |  |  |  |  |

|   |      | 5.5.1    | Sequence Specification                                                                                                                  |  |  |  |  |  |

|   |      | 5.5.2    | Local Variables                                                                                                                         |  |  |  |  |  |

|   |      | 5.5.3    | Sequence Evaluation Modes                                                                                                               |  |  |  |  |  |

|   | 5.6  | Event    | Layer                                                                                                                                   |  |  |  |  |  |

|   |      | 5.6.1    | Categorization of Events                                                                                                                |  |  |  |  |  |

|   |      | 5.6.2    | Operators                                                                                                                               |  |  |  |  |  |

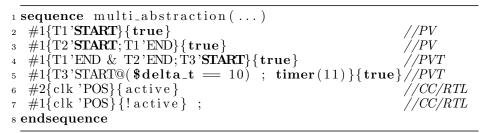

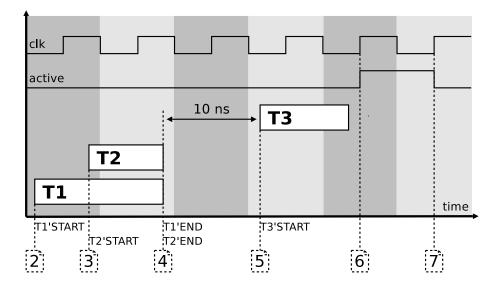

|   |      | 5.6.3    | Multi-Abstraction Example                                                                                                               |  |  |  |  |  |

|   | 5.7  | Boolea   | an Layer                                                                                                                                |  |  |  |  |  |

| 6 | Forr | nal Sei  | mantics 93                                                                                                                              |  |  |  |  |  |

|   | 6.1  | Trace    | Semantics                                                                                                                               |  |  |  |  |  |

|   |      | 6.1.1    | Traces                                                                                                                                  |  |  |  |  |  |

|   |     | 6.1.2   | UAL Trace                                | 95  |  |

|---|-----|---------|------------------------------------------|-----|--|

|   |     | 6.1.3   | UAL Semantics with Regard to PSL and SVA | 100 |  |

|   | 6.2 | Conce   | pt                                       | 102 |  |

|   | 6.3 | Globa   | l Definitions                            | 102 |  |

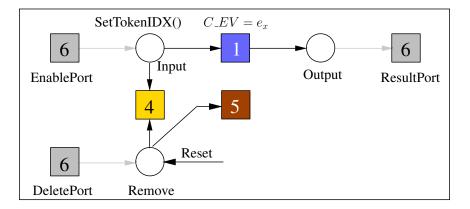

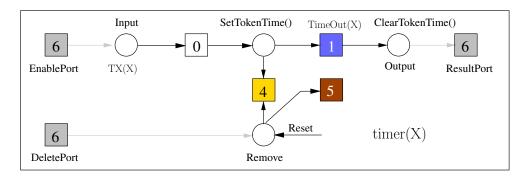

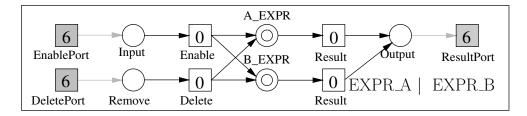

|   |     | 6.3.1   | Interfacing the Trace                    | 102 |  |

|   |     | 6.3.2   | High-Level Colored Petri-Net             | 103 |  |

|   |     | 6.3.3   | Token Structure                          | 103 |  |

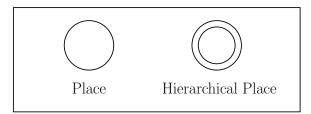

|   |     | 6.3.4   | Places                                   | 106 |  |

|   |     | 6.3.5   | Transitions                              | 107 |  |

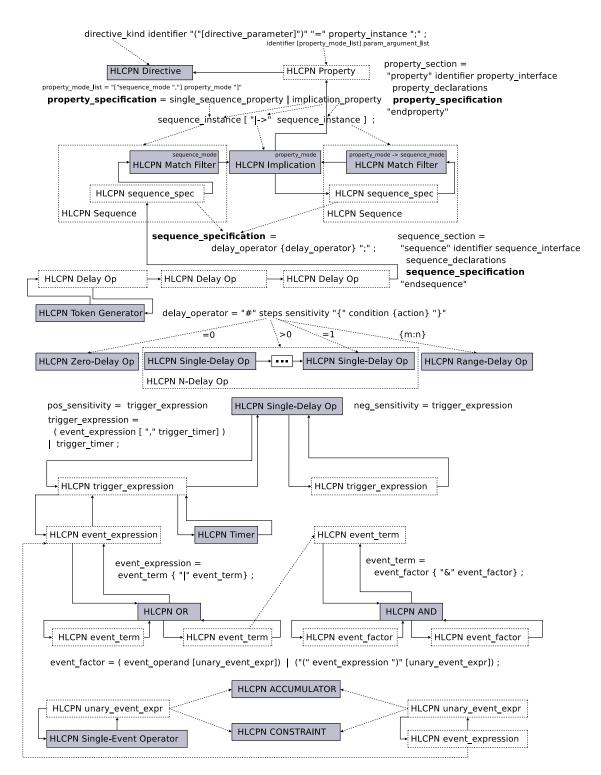

|   | 6.4 | Hierar  | chical Overview                          | 111 |  |

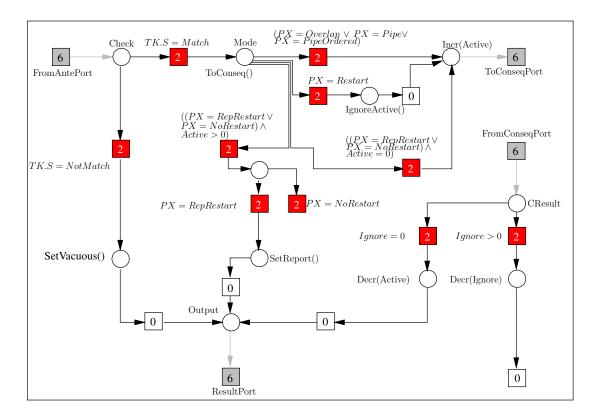

|   | 6.5 | Verific | cation Layer                             | 113 |  |

|   | 6.6 | *       |                                          |     |  |

|   | 6.7 | Seque   | nce Layer                                | 117 |  |

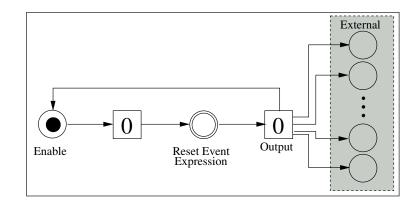

|   |     | 6.7.1   | HLCPN Token Generator                    | 119 |  |

|   |     | 6.7.2   | HLCPN Sequence Item                      | 120 |  |

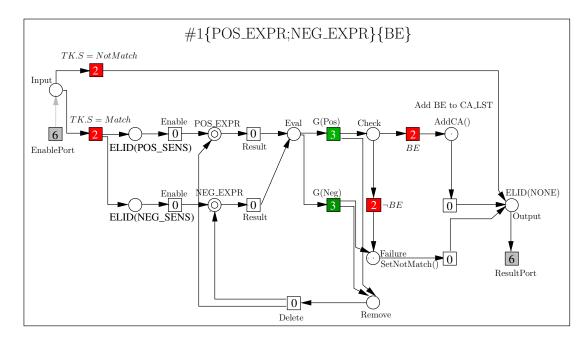

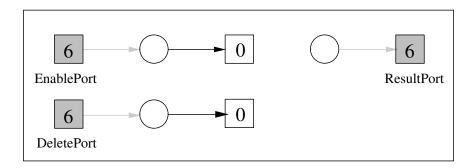

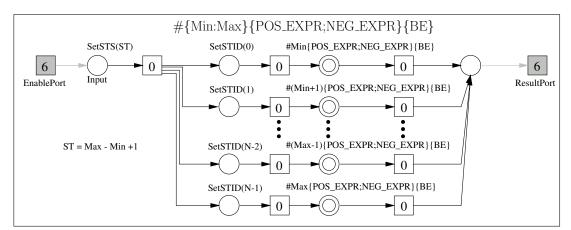

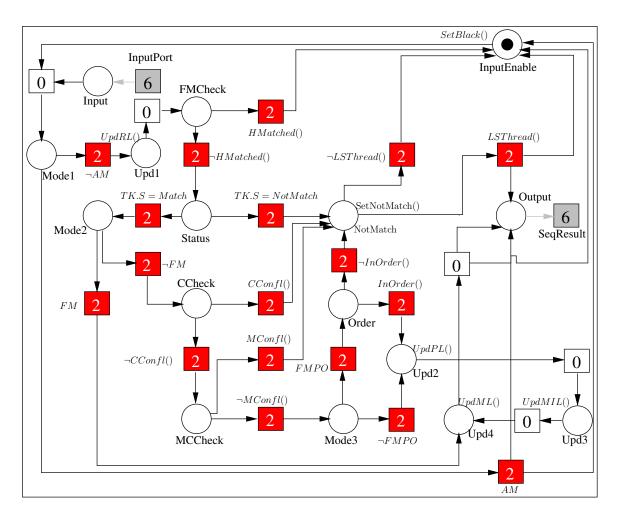

|   |     | 6.7.3   | HLCPN Match Filter                       | 125 |  |

|   | 6.8 | Event   | Layer                                    | 130 |  |

|   |     | 6.8.1   | HLCPN Single Event Operator              | 131 |  |

|   |     | 6.8.2   | HLCPN Timer                              | 132 |  |

|   |     | 6.8.3   | HLCPN OR Operator                        | 133 |  |

|   |     | 6.8.4   | HLCPN AND Operator                       | 133 |  |

|   |     | 6.8.5   | HLCPN CONSTRAINT Operator                | 135 |  |

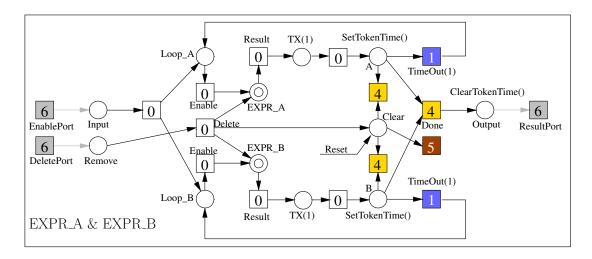

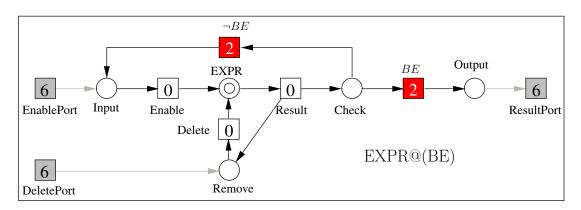

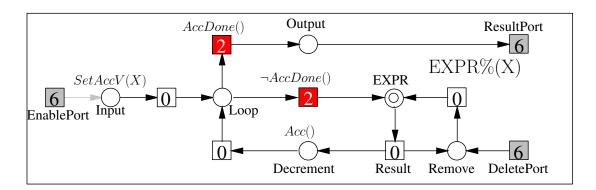

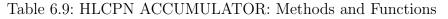

|   |     | 6.8.6   | HLCPN ACCUMULATOR Operator               | 135 |  |

| _ |     |         |                                          |     |  |

| 7 |     |         | cation Framework                         | 137 |  |

|   | 7.1 |         | iew                                      | 137 |  |

|   | 7.2 |         | ng Language                              | 138 |  |

|   |     | 7.2.1   | Targets Section                          | 139 |  |

|   |     | 7.2.2   | Mappings Section                         | 141 |  |

|   | 7.3 |         | st Language                              | 143 |  |

|   |     | 7.3.1   | Testcase Parameterization                | 144 |  |

|   |     | 7.3.2   | Stimuli Specification                    | 145 |  |

|   | 7.4 |         | Base Library                             | 146 |  |

|   |     | 7.4.1   | Token Network                            | 147 |  |

|   |     | 7.4.2   | Event Handling                           | 148 |  |

|   |     | 7.4.3   | Transaction Detection                    | 150 |  |

|   |     | 7.4.4   | Runtime API                              | 151 |  |

|   | 7.5 | Bindir  | ng                                       | 152 |  |

|   | 7.6 | UAL (   | Compiler                                 | 153 |  |

| 8                     | Арр              | lication                | I                             | 155 |  |  |  |

|-----------------------|------------------|-------------------------|-------------------------------|-----|--|--|--|

|                       | 8.1              | 1 Application Flow      |                               |     |  |  |  |

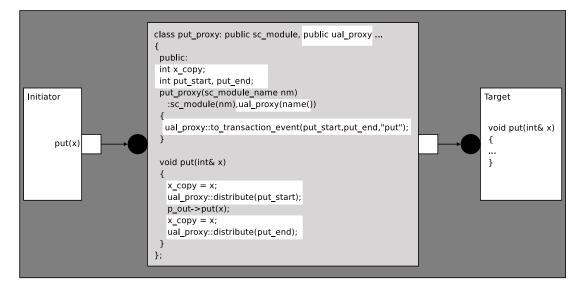

|                       | 8.2              | Proxy                   | Example                       | 156 |  |  |  |

| 8.3 CPU-Queue Example |                  |                         | Queue Example                 | 157 |  |  |  |

|                       |                  | 8.3.1                   | Assertions for the CPU Queue  | 158 |  |  |  |

|                       |                  | 8.3.2                   | Correct Node Sorting          | 159 |  |  |  |

|                       |                  | 8.3.3                   | Correct Transaction Stream    | 163 |  |  |  |

|                       | 8.4              | Transa                  | uctor                         | 165 |  |  |  |

|                       | 8.5              | IP Inte                 | egration Verification         | 167 |  |  |  |

|                       |                  | 8.5.1                   | Address Decoding              | 167 |  |  |  |

|                       |                  | 8.5.2                   | Correct Wrapping              | 169 |  |  |  |

|                       | 8.6              | Contro                  | bl and Data Flow Verification | 170 |  |  |  |

|                       |                  | 8.6.1                   | Control Flow Checking         | 170 |  |  |  |

|                       |                  | 8.6.2                   | Data Flow                     | 172 |  |  |  |

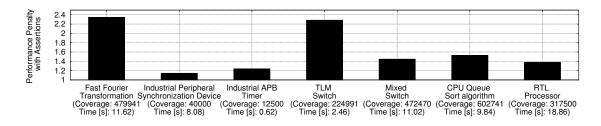

|                       | 8.7              | Perform                 | mance Analysis                | 173 |  |  |  |

|                       |                  | 8.7.1                   | Runtime Performance           | 173 |  |  |  |

|                       |                  | 8.7.2                   | Lines of Code Analysis        | 175 |  |  |  |

|                       |                  | 8.7.3                   | Compiletime Performance       | 176 |  |  |  |

|                       |                  | 8.7.4                   | Experiences                   | 176 |  |  |  |

| 9                     | Sum              | Summary and Outlook 179 |                               |     |  |  |  |

| Bil                   | Bibliography     |                         |                               |     |  |  |  |

| Ac                    | ronyı            | ms                      |                               | 189 |  |  |  |

| Glo                   | ossar            | y                       |                               | 193 |  |  |  |

| Α                     | Rea              | uireme                  | nts Summary                   | 197 |  |  |  |

|                       |                  |                         | Requirements                  | 197 |  |  |  |

|                       |                  |                         | prization                     | 201 |  |  |  |

| в                     | Language Grammar |                         |                               |     |  |  |  |

|                       | B.1              |                         | or Grammar                    | 203 |  |  |  |

|                       | B.2              | Bind (                  | Grammar                       | 207 |  |  |  |

|                       | B.3              | Testbe                  | ench Grammar                  | 208 |  |  |  |

|                       | B.4              | Comm                    | on Grammar                    | 209 |  |  |  |

# List of Tables

| 5.1 | EBNF Syntax Description                       | 48 |

|-----|-----------------------------------------------|----|

| 5.2 | Property Mode Derivation                      | 59 |

| 5.3 |                                               | 82 |

| 5.4 |                                               | 91 |

| 6.1 | Common Methods                                | 13 |

| 6.2 | HLCPN Implication Component: Internal Methods | 16 |

| 6.3 | Delay Operator Methods and Functions          | 20 |

| 6.4 | Methods for HLCPN Range-Delay Operator        | 24 |

| 6.5 | HLCPN Match Filter: Parameters                | 25 |

| 6.6 | 1                                             | 26 |

| 6.7 | HLCPN Match Filter: Conditions                | 27 |

| 6.8 | Event Layer Methods and Functions             | 31 |

| 6.9 | HLCPN ACCUMULATOR: Methods and Functions      | 36 |

| 7.1 | Runtime API Functions                         | 51 |

| 8.1 | Lines of Code Comparison                      | 75 |

| 8.2 | SystemC Compilation Time Comparison           | 76 |

| A.1 | Categorization of Requirements                | )2 |

# **List of Figures**

| $1.1 \\ 1.2 \\ 1.3$                                                                                    | Forecast of number of components over time [1]                                                                                                                                                                                                                                                                                                                       | $2 \\ 3 \\ 5$                                      |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

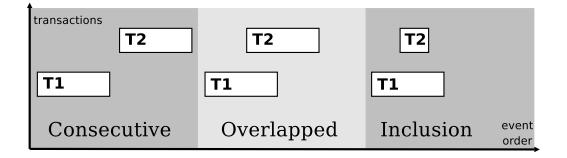

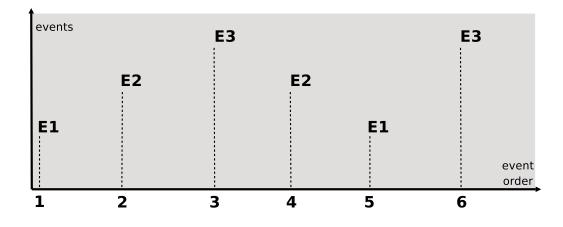

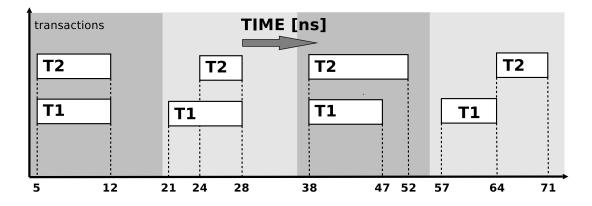

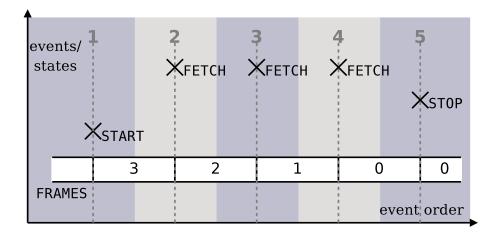

| 3.1<br>3.2<br>3.3                                                                                      | Transaction Relations on PV                                                                                                                                                                                                                                                                                                                                          | 23<br>24<br>25                                     |

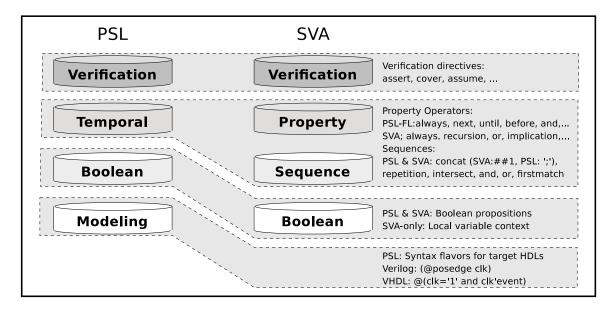

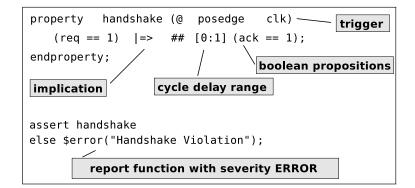

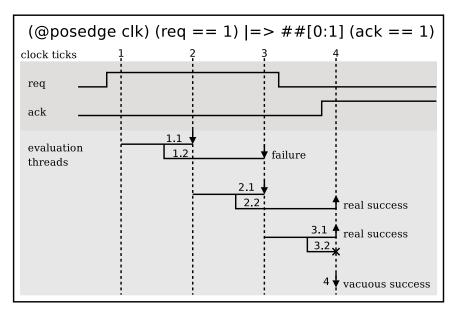

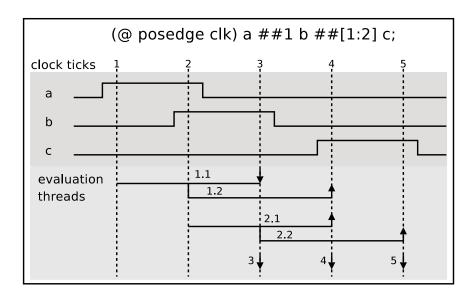

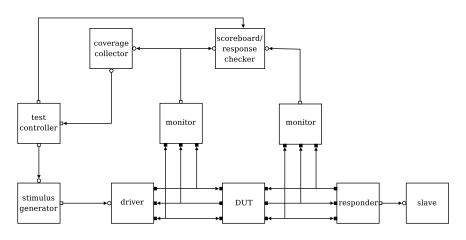

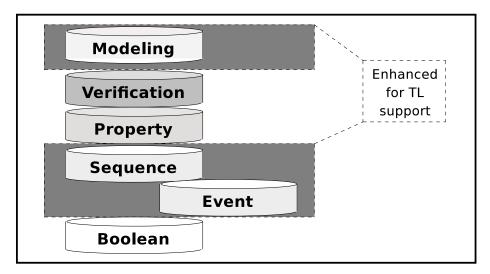

| $\begin{array}{c} 4.1 \\ 4.2 \\ 4.3 \\ 4.4 \\ 4.5 \end{array}$                                         | Layered Structure of PSL and SVA                                                                                                                                                                                                                                                                                                                                     | 30<br>31<br>32<br>34<br>37                         |

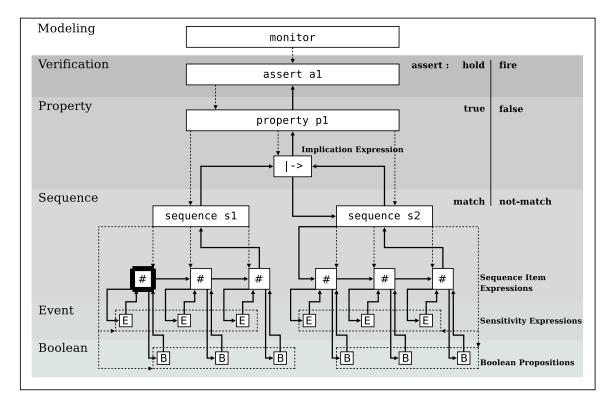

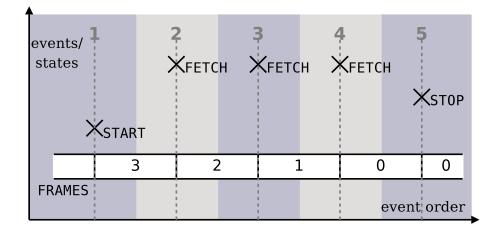

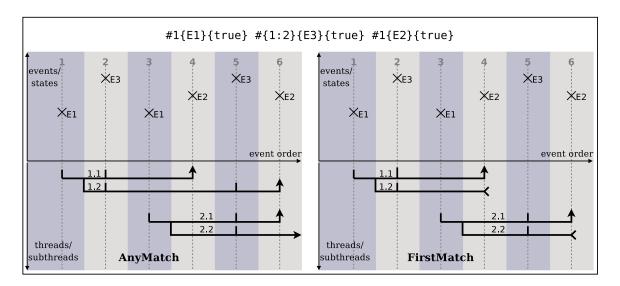

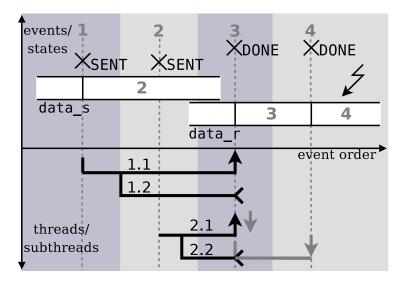

| $5.1 \\ 5.2 \\ 5.3 \\ 5.4 \\ 5.5 \\ 5.6 \\ 5.7 \\ 5.8 \\ 5.9 \\$                                       | Layered Approach of UAL -assertionsAssertion StructureAssertion StructureSynchronizer Block ExampleUAL Modes AnyMatch and FirstMatch for SequencesUAL Modes AnyMatch Mode for Pipelined BehaviorInsufficiency of FirstMatch Mode for Pipelined BehaviorIllegal Overlapping of ThreadsIn-Order / Out-Of-Order PipeliningCategorization of EventsAND Operator Examples | 45<br>46<br>67<br>71<br>73<br>75<br>78<br>79<br>84 |

| $5.10 \\ 5.11$                                                                                         |                                                                                                                                                                                                                                                                                                                                                                      | 88<br>90                                           |

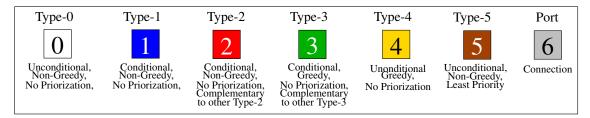

| $     \begin{array}{r}       6.1 \\       6.2 \\       6.3 \\       6.4 \\       6.5     \end{array} $ | Types of Petri Net Places                                                                                                                                                                                                                                                                                                                                            | 106<br>107<br>112<br>114<br>114                    |

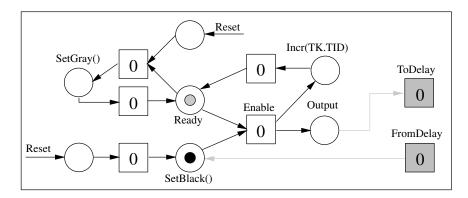

| 6.6<br>6.7<br>6.8<br>6.9                                                                               | HLCPN Implication ComponentToken GeneratorHLCPN Zero-Delay OperatorHLCPN Single-Delay Operator                                                                                                                                                                                                                                                                       | 115<br>119<br>121<br>122                           |

| 6.10 | HLCPN Empty Sensitivity            | 123 |

|------|------------------------------------|-----|

| 6.11 | HLCPN Range-Delay Operator         | 124 |

|      | HLCPN Match Filter                 |     |

| 6.13 | HLCPN Single Event Operator        | 131 |

|      |                                    | 132 |

| 6.15 | HLCPN OR Operator                  | 133 |

|      |                                    | 134 |

|      | HLCPN CONSTRAINT Operator          | 135 |

|      | HLCPN ACCUMULATOR Operator         |     |

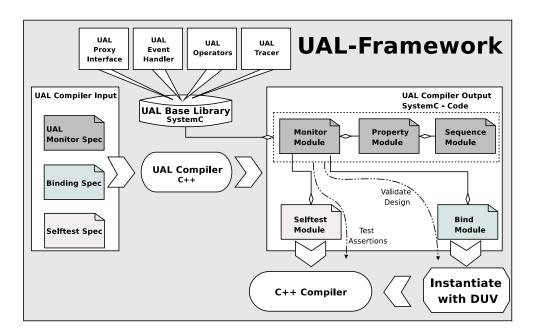

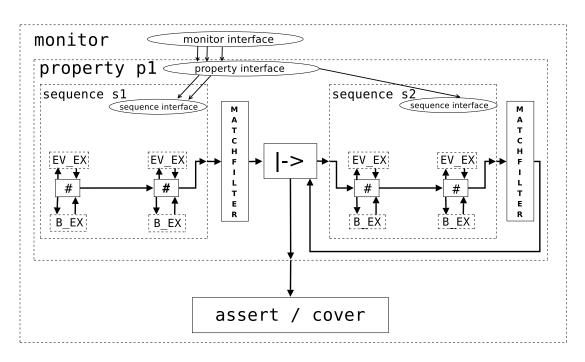

| 7.1  | UAL Application Framework Overview | 138 |

| 7.2  |                                    | 147 |

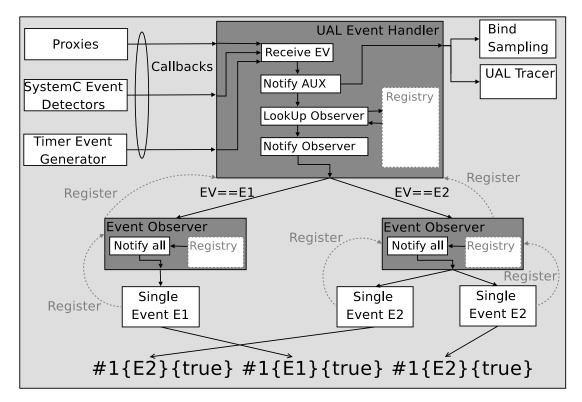

| 7.3  | Event Propagation Infrastructure   | 148 |

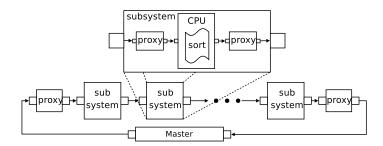

| 8.1  | Transaction Detection Proxy        | 156 |

| 8.2  | CPU Queue                          |     |

| 8.3  | Performance Results                |     |

|      |                                    |     |

# List of Listings

| 5.1  | Example: Ports Section                             |

|------|----------------------------------------------------|

| 5.2  | Example: Formal Argument Lists                     |

| 5.3  | Example: Assert Directive                          |

| 5.4  | Example: Cover Directive                           |

| 5.5  | Example: Implication Property 57                   |

| 5.6  | Example: Single Sequence Property                  |

| 5.7  | Sequence with Local Variables                      |

| 5.8  | Data Transport Sequence    73                      |

| 5.9  | Pipelined Communication Protocol Sequence          |

| 5.10 | FIFO-Pipeline                                      |

| 5.11 | Adaptive Timing in Sequences                       |

| 5.12 | Adaptive Triggering of Sequences                   |

| 5.13 | Multi-Abstraction Sequence                         |

| 7.1  | Example Target Section 141                         |

| 7.2  | Example Mappings Section                           |

| 7.3  | Example Testbench Section                          |

| 8.1  | Monitor for Checking Sort Algorithm: Interface     |

| 8.2  | Monitor for Checking Sort Algorithm: Sequences 160 |

| 8.3  | Monitor for Checking Sort Algorithm: Property      |

| 8.4  | Monitor for Checking Sort Algorithm: Directive     |

| 8.5  | Bind to Class Example                              |

| 8.6  | Stream Property 164                                |

| 8.7  | Antecedent of Stream Property 164                  |

| 8.8  | Consequent of Stream Property 165                  |

| 8.9  | TL Read-Protocol                                   |

| 8.10 | RTL Read-Protocol                                  |

| 8.11 |                                                    |

|      | IP-Address Decoding: Property 167                  |

| 8.13 | IP-Address Decoding: Antecedent                    |

|      | IP-Address Decoding:Consequent                     |

| 8.15 | Correct Wrapping: Property                         |

| 8.16 | Correct Wrapping: Antecedent                       |

|      | Correct Wrapping: Consequent                       |

| 8.18 | Control-Flow                                       |

| 8.19 | FIFO Data Flow: | Antecedent               | <br> | <br> | 172 |

|------|-----------------|--------------------------|------|------|-----|

| 8.20 | FIFO Data Flow: | $Consequent \ . \ . \ .$ | <br> | <br> | 173 |

| 8.21 | FIFO Data Flow: | Property                 | <br> | <br> | 173 |

## **1** Introduction

### 1.1 The Ubiquity of Embedded Systems

Over the past decades, embedded systems have become an integral part of our society. This is due to the fast evolution of the semi-conductor industry, which enables more and more features integrated on a single chip for continuously decreasing prices. The application of embedded systems has a large scope. The automotive industry for example shows a trend towards integrating more and more electronic systems within a car. Whole entertainment systems are being integrated. Engine control systems are developed that allow for the most efficient use of gas in order to reduce carbon-dioxide emission. Also safety critical applications of embedded systems are being developed like break by wire or inter car communication for avoiding collisions through early warning systems. The communication business is solely based on embedded systems. The fast development and evolution of cellular phones, PDAs, DSL, and so forth, shows how much embedded systems have become a part of peoples lives. In general, information technology based on embedded systems is fundamental for keeping our industry up and running.

## 1.2 System Complexity

The key driver for the immense success of embedded systems are market forces that foster the development of cheaper products based on engineering genius and walking along a learning curve with an exponential slope. The empirical observation made by Gordon E. Moore in 1965 which states that the number of transistors per chip doubles every two years<sup>1</sup> at a minimum level of costs [6] was and is still valid. This also means that the complexity of a chip in terms of transistors shows an exponential rise over time. As indicated by the International Technology Roadmap for Semiconductors (ITRS), it can be expected that the on-chip complexity will increase further measured in terms of the number of integrated components, at least until the year 2020.

<sup>&</sup>lt;sup>1</sup>In some cases an even stronger statement can be made; selected devices as for instance CPUs, double complexity within 18 months [5].

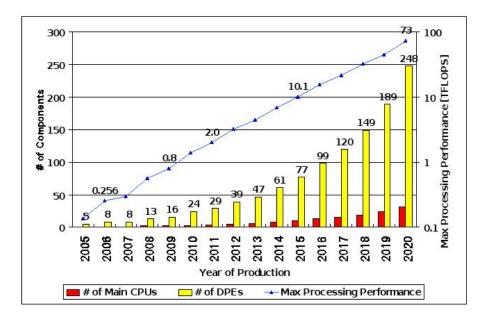

Figure 1.1: Forecast of number of components over time [1]

Figure 1.1 shows a tremendous increase of Data Processing Engine (DPE) elements over time. A DPE represents dedicated Hardware (HW) for implementing a specific task. Also the number of main Central Processing Unit (CPU) elements shows an increase, though the rate is much lower.

Given this development it can easily be seen that a company needs to put very efficient development and production processes in place in order to obtain and keep a strong competitive position in the market, because the effort involved to develop more and more complex systems keeps increasing as well.

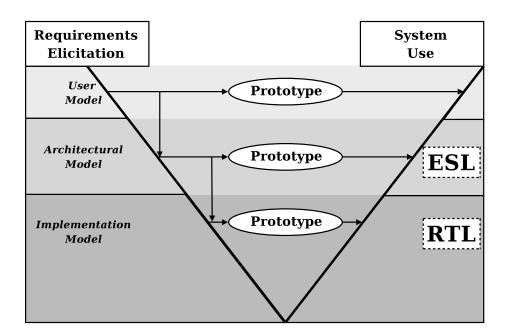

The most common approaches taken by semi-conductor companies for tackling the problem of increasing complexity are on one hand the reuse of existing matured system components and on the other hand the early exploration of different architectures based on structurally more abstract executable descriptions of the targeted system, partially with reduced functionality. These systems include both reused and newly developed system components. Figure 1.2 shows a slightly adapted version of the V-Process-Model [2] which defines a development process which ensures the quality of a HW product. In order to speed up the development of the implementation model, early effort is spent for the architectural model. While the implementation model represents a synthesizable description at the Register Transfer Level (RTL), the architectural model is described by means offered in the Electronic System Level (ESL) domain.

Figure 1.2: The Model of the Design Process: The V-Process-Model [2]

ESL describes the industry wide activities on modeling and analyzing systems at a higher than RTL abstraction, taking both HW and Software (SW) into account. While this term is newly evolving, it actually describes ongoing activities of the past years. However, it is more focused at present due to the increasing complexity of even abstract model descriptions. The progress is reflected by the ongoing standardization activities by Open SystemC Initiative (OSCI), such as the SystemC modeling language [7] and the TLM standard [8]. A quite accurate definition of ESL has been given in [9] which states that ESL is "the utilization of appropriate abstractions in order to increase comprehension about a system, and to enhance the probability of a successful implementation of functionality in a cost-effective manner, while meeting necessary constraints".

The rationale behind investing great effort in high-level models and their analysis is straight forward. During the architectural exploration phase, many decisions have to be taken with regard to HW/SW partitioning. Therefore, it is necessary to analyze the high-level model in terms of throughput and even in terms of power in order for the best decision to take. Performing such analysis steps only after having completed the implementation model (i.e., the RTL model) usually is too late and too time consuming. Also the available analysis tool set requires too much computation time on this level to perform full system analysis. Furthermore, uncovering performance and power bottlenecks after the completion of the RTL implementation would require a full redesign in the worst case. This implies that almost all steps would have to be repeated. Such a situation is undesirable and not economic.

In addition to making architectural decisions, a behavioral model is also used for enabling the development of SW at an early stage. The SW is then executed on the behavioral model of the system. This allows for the SW to mature while the implementation model is still under way.

The whole process of developing high-level models of a target system is also described as virtual prototyping and the resulting model is called Virtual Prototype (VP).

It can be observed that the rise in chip complexity drives the need for new methods in ESL both for design and verification [10]. More and more abstract components have to be developed and integrated to an abstract representation of a System-on-a-Chip (SoC) including analog, mixed signal parts as well as the conventional digital domain. Effective methods in ESL will become challenging. The importance of these methods can be compared to the new methodologies (e.g., RTL-synthesis, linting, formal verification) which have emerged when transitioning from the gate-level towards RTL.

### 1.3 The Role of Verification

The rise of complexity during the past years has also brought up the issue of verification. In contrast to pure SW, a bug in a taped out HW circuit is hard to fix. Usually it is not easily possible to work around a bug by adapting the corresponding bits in the SW which is supposed to be executed on the HW. Not only that a bug in a taped out chip might scare away customers and hence, decrease a companies revenue by orders of magnitude; the fact that an undetected bug makes it to an end product in a safety critical environment can cost lives and cause other fatal consequences. To dampen such a high risk serious effort is spent in testing a taped out prototype of an SoC and upon detecting severe bugs a full re-spin of the production cycle is required, which in turn involves high cost and a bigger risk to miss the time-to-market window. Considering the fact that most hard-to-detect bugs are still introduced during the development of the RTL implementation rather than in the production phase, it was clear that functional verification had to be emphasized in the design automation activities. The validity of Moore's Law has led to very complex products, which could not be verified efficiently anymore by simulating directed tests of a system.

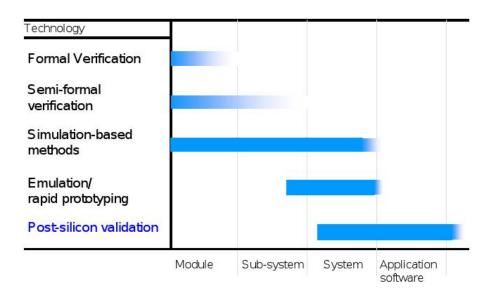

Figure 1.3 shows the verification technology landscape, which has evolved once verification became a hot topic. Each different technology is mapped onto the domains where it is applied best.

Figure 1.3: Verification Technology Landscape according to ITRS [3]

#### 1.3.1 Formal Verification

Formal verification techniques rely on the exploration of a model on a mathematical basis. Proofs can be performed to determine, whether a design under scrutiny fulfills its specification. The most successful approach here is the application of the so called Bounded Model Checking (BMC) [11],[12], which exists in different variants. Formal verification techniques are applied mostly at the block-level. Since the underlying key idea is the mathematical analysis of transition paths through the design state space, the problem of state space explosion hinders the applicability to big complex components. Since the size of the state space grows exponentially with the number of states, an exploration of its transition paths is not computable due to insufficient computing power and memory. One of the major goals in formal verification related research is the enhancement of the applied algorithms and the development of new techniques which attempt to reduce the complexity of the original implementation model by means of abstraction. These techniques differ from abstraction techniques applied in the ESL domain.

#### 1.3.2 Semi-Formal Verification

Semi-formal verification approaches bring together both dynamic verification (simulation) and formal verification techniques. Here, the Design Under Verification (DUV) is stimulated by a testbench. As soon as critical states (e.g., a counter has reached its maximum value) are reached, a formal analysis is started with usually a small bound. The difficulty here is that this methodology is critical with regard to verification management because this methodology does not allow proving the absence of bugs in the DUV in contrast to purely formal approaches. Applying a testbench always means that the results can not be generalized. Therefore, semi-formal techniques can be characterized as "bug-hunters".

### 1.3.3 Simulation Based Methods

Due to the limited power of purely formal techniques, simulation based techniques can not be replaced entirely. Dynamic verification still remains the most applicable methodology for verification. As Figure 1.3 also indicates, simulation based methods are applied at the block-level as well as at the system-level. Yet, powerful methodologies have emerged which allow to exercise a design thoroughly but still not exhaustively.

#### **Constrained Random Testbenches**

Instead of "just" simulating directed tests, techniques are applied which stimulate a DUV with randomized inputs. The randomization is constrained to provide a general direction for a simulation. In this context another technique is applied which yields measures for verification management. This technique is called "Coverage". Coverage results in general show how much a design is exercised. Different scopes for coverage exist. Coverage can be:

- Code Coverage: Yield how many times a certain part of code has been exercised.

- **State Coverage**: Yield how many times a certain state variable has taken on a certain value or a series of values.

- **Cross Coverage**: Yield how many times a certain state variable has taken on a certain value while a different state variable has taken on a different value.

- Assertion Coverage: Yield how many times a temporal behavior specified in terms of an assertion has been encountered.

Coverage results are stored in databases. The results can be used to determine when to stop a fully automated test run and furthermore, they can be used to guide the random stimulus generation such that the parts of the DUV which show less coverage are exercised more.

The effort for writing randomized testbenches is furthermore reduced by using abstraction schemes in the stimuli generation and application. Stimuli are represented in abstract data structures (e.g., an object that represents the information of a picture frame for displaying). The application of stimuli to a DUV is modeled in terms of transactions or sets of transactions. The abstract data structures are driven into a DUV by using these transactions (e.g., sending a picture frame to a display controller). This abstraction is obtained via Bus Functional Model (BFM) elements also referred to as transactors. These BFM components translate between abstraction levels and are connected between a stimulus generator and the DUV. A BFM hides the signallevel protocol details behind method calls (i.e., transactions). The responses of the DUV are again connected to BFMs in order to check them at the same abstraction as the stimuli. Such an abstraction technique also makes it possible to reuse testbenches for an RTL design with its corresponding model in the ESL domain or vice versa. However the reuse is mostly restricted to the stimuli generation part and response checking. Usually the coverage definitions need to be altered severely or even have to be written from scratch, since the corresponding implementation of a model at different abstraction levels follows different modeling paradigms (i.e., structures of lower level implementations are not available at higher levels).

#### Assertions

Another major development in RTL verification was introduced under the term "Assertion Based Verification (ABV)" [13]. ABV enables the application of SW development principles to RTL modeling and design, such as "defensive programming", "design-by-contract", etc. ABV is complementary to both formal and dynamic verification technologies. An assertion is an abstract statement that a certain behavioral property of a design must never be violated. Assertions can be validated using both formal and dynamic verification techniques. Conceptually, an assertion contains a formal description of a desired temporal behavior (i.e., property) and monitors the execution of the design model. Assertions can be used also internally in a design model. Any encountered violation of the desired behavior is reported.

ABV eases the development of testbenches, since assertions monitor internal behaviors of a model. Thus, if an error occurs within the scope of one assertion, this error is reported immediately. Tedious attempts to make sure that any error is propagated to the output of the model such that it can be detected by external checking mechanisms is no longer required. Furthermore, the immediate error notification spares the verification engineer from backtracking long simulation traces to find the origin of an error. Therefore, debug time can be reduced tremendously.

Furthermore, assertions have another advantage; when developing the RTL implementation a designer can specify assertions about the intent of the block which is currently developed. Also, the designer can specify which constraints to the environment of the block are assumed. In this case, the violation of an assertion would reflect the wrong usage of that specific block. As well, assertions might reveal misinterpretations of a given imprecise specification. As Leslie Lamport has stated: "In engineering, imprecision is an invitation to error" [14]; thus, a good ABV methodology, can reveal many bugs, especially bugs which are deeply hidden in a design model. In combination with constraint random testbench techniques, assertions can reveal how often the monitored behavior has been exercised and furthermore, randomized stimuli increase the probability that an assertion detects an error which only occurs at situations which were not anticipated in advance.

Many reports have emerged which reveal that the application of ABV has lead to a boost in verification efficiency. Therefore, an ABV methodology has become a vital part of the overall verification strategy of many companies [15], [16], [17].

#### 1.3.4 Emulation / Rapid Prototyping

A full simulation of an RTL system is too time consuming due to the high degree of details which a simulator would have to address. Therefore, emulation and rapid prototyping techniques are used to tackle this problem. These techniques refer to the utilization either of highly performing processing units to aid the verification task or of the implementation of the model on complex Field Programmable Gate Array (FPGA) boards (i.e., the model is executed rather than being simulated).

ABV is also utilized in combination with these techniques. Here, assertions are synthesized and become part of the RTL implementation. Therefore, it is possible to have assertions run checks on for instance an FPGA board [18], [19].

The use of VPs is a countermeasure, since a system at a very high-level of abstraction enables feasible simulator run-times due to the reduction of model details. Furthermore, emulation and rapid prototyping require a complete RTL implementation. Hence, SW development still would have to be started at a very late stage of implementation. Thus, it can be expected that ESL will sooner or later make emulation and rapid prototyping techniques completely redundant.

#### 1.3.5 Post-Silicon Validation

Post silicon validation refers to plugging a silicon implementation of a system onto a tester and driving test patterns in it. On-chip-debug infrastructure allows a limited access to the internal states of the system in order to be able to test the chip for production errors. ABV is used in a similar fashion as mentioned with the previous verification techniques. Development work is currently in progress in [20] which enables debuggers to interact with on-chip assertions. Assertion failures can be used to freeze the core of a system, in order to allow a close analysis of the systems state, utilizing the on-chip scan-chains and JTAG interfaces.

In a perfect world, however, no functional bugs should exist at this stage of the development.

## 1.4 Motivation

As mentioned in the previous two sections, increasing complexity impacts the efficiency both of product development and verification. On the development side, the increase of complexity is tackled by component reuse and abstract modeling. On the verification side, sophisticated approaches have been used for ensuring the quality of a product. Up to now, functional verification has been mainly focused on the RTL domain. Reuse of RTL testbenches for ESL is currently the main methodology for checking the functional compliance of an RTL implementation and its corresponding ESL implementation (i.e., the ESL model is used as a golden reference for the verification of an RTL model). Keeping in mind however, that the increase of complexity which is anticipated for the upcoming years will also make even abstract ESL models highly complex, it becomes obvious that the verification of ESL models has to be much more thorough than it is today. This requires a comparable evolution of verification technology for ESL the same way it has happened for RTL. According to ITRS the following statement has been made regarding verification at higher levels of abstraction:

As design moves to a level of abstraction above register transfer level (RTL), verification will have to keep up. The challenges will be to adapt and develop verification methods for the higher-levels of abstraction, to cope with the increased system complexity made possible by higher-level design, and to develop means to check the equivalence between the higherlevel and lower-level models. This longer-term challenge will be made much more difficult if decisions about the higher-level of abstraction are made without regard for verification (e.g., languages with ill-defined or needlessly complex semantics, or a methodology relying on simulationonly models that have no formal relationship to the RTL model) [3].

This work addresses some of the points mentioned in [3] by introducing ABV to ESL. By means of a new language, it will be shown how known RTL concepts can be adapted and extended to be applicable at ESL as well, while still allowing for a unified approach that covers RTL, too. The same benefits which ABV has introduced

to RTL verification is expected for the verification of ESL. However, this work not only focuses on the sole application on ESL. It rather supports assertion specification for multiple levels of abstraction which can be present within one model. Being able to cope with multiple levels of abstraction also enables cross abstraction checks through the use of assertions. Therefore, compliance checks between ESL and RTL models can be enhanced by adding assertions which monitor both models in a co-simulation environment.

## 1.5 Outline

This work is organized in nine chapters addressing different aspects.

Chapter 2 gives a short description of the problems which arise when attempting to use ABV as is at higher levels of abstraction and outlines some concepts for solving these.

Chapter 3 introduces the requirements to be met by an assertion language in order to be highly applicable at higher levels of abstraction.

Chapter 4 describes and discusses the state-of-the-art and related work with regard to the tasks at hand.

Chapter 5 introduces and describes all new concepts and features of the newly designed assertion language.

Chapter 6 introduces the formal foundation and semantics of the assertion language.

Chapter 7 explains the complete application framework and highlights some aspects with regard to its implementation.

Chapter 8 describes examples for different kinds of assertions specified with the newly developed language.

Chapter 9 summarizes the scientific contribution of this work and outlines further directions.

# 2 Problem Statement and Targeted Approach

This chapter addresses the problems that arise when attempting to apply existing ABV approaches at higher levels of abstraction (i.e., mainly in the ESL domain). Furthermore, possible solutions are outlined.

## 2.1 TL Modeling and Design

The key to ESL is abstraction. Abstraction means the reduction of details within a model to the necessary level of granularity which is required to provide an executable model of a given system specification. The reduction of details in turn means that executing such a model requires less computational effort and hence, reduces both tool runtime and memory consumption. Therefore, it is possible to simulate an abstract model of a system in feasible time in contrast to RTL. The modeling paradigm in ESL is best known as Transaction Level (TL) modeling and such a model is called a Transaction Level Model (TLM). A Virtual Prototype (VP) is a TLM of a whole system. The level of details which has to be modeled within a TLM is determined by the goals of the analysis which is intended to be performed on it.

The main requirements a VP has to adhere to are the following:

- Compositional view of the system: Functionality has to be partitioned into different components which communicate. The partitioning shall reflect at least on toplevel the partition of the intended design (e.g., CPUs, bus structure).

- Register Accurate: All registers which are intended to be accessible by SW need to be modeled. The register must be accessible via the CPU bus to allow SW read and write accesses.

- Full Memory Map: All resources including blocks and registers have to follow the address map defined by the specification; if the address map is not specified, it is defined for the VP and used in later design stages.

• Communication Topology: All components need to follow the same communication topology as defined by the specification.

The fulfillment of these requirements is necessary in order to enable SW development on the VP. This SW later on also runs on the RTL and silicon implementation.

The kinds of details which are usually abstracted away are the following:

- Clocked Synchronization: Every value change of a clock signal at RTL needs to be processed by a simulator in order to execute all processes sensitive to a specific clock edge. This means that also processes need to be considered which actually do not induce any state transitions. In order to reduce this effort, clocks are usually modeled differently in TLMs or are even omitted. Synchronization is only modeled when a certain causality needs to be enforced. This is achieved by having processes emit events which other processes are sensitive to. Events may be conditional clocks or transaction state changes, to give examples.

- Timing: Timing of a system is only modeled where it is relevant. For example a purely SW-centric view of the system does not require timing to be modeled at all. In case timing is required it is modeled at that level of granularity which is needed to conduct performance analysis. Timing can either be modeled using the simulation time which comes with the simulation kernel of any popular HW description language, or it can be annotated in terms of states, that means time is calculated by the model, not by the simulation kernel.

- Signals: Communication between processes is not modeled with signal-level protocol accuracy. Here, for each signal value update events are emitted which need to be processed. Instead, complete communication protocols are abstracted and reduced to abstract message passing modeled with function calls.

- State-Machines: As soon as complete paths through an RTL state-machine can be substituted by procedural operations, it is no longer necessary to model the state-machine as such, since the state is reflected by the line of code which is executed.

- HW data types: HW data types are omitted and abstract data types (e.g., classes, structs, pointers) are used on which high-level operations are defined.

## 2.2 TL Modeling Impact to ABV

The better the abstractions mentioned in Section 2.1 are with regard to simulation performance and fast development of system prototypes the more difficulties they impose when applying RTL verification techniques. Most sophisticated approaches to ABV apply some form of temporal logic specification, which expresses temporal relations of signal values in terms of clock ticks. A clock tick reflects the progression in time and usually determines when to evaluate an assertion.

#### 2.2.1 The Notion of Temporal Behavior

The first problem to be addressed for applying ABV to TLMs is the clarification of the notion of temporal behavior. The use of clocks is reduced or even avoided to increase simulation performance. In addition to that, ESL supports abstraction levels where time is not modeled at all, modeled in terms of annotations, or modeled with processes which wait for a specific time to pass prior to resuming. In connection to this issue, it also has to be taken into account that different components within a VP may be modeled at different abstractions. It is also possible that some components are completely modeled at RTL in a clock-related way. It also has to be considered when to trigger an evaluation of an assertion at all. Since assertions monitor the system behavior, it has to be solved how to keep an assertion evaluation synchronous to the monitored system. Generally, the endeavor on ESL is to reduce the number of events to be processed by a simulation kernel for the sake of performance. Therefore, using these events as a possible solution for synchronizing assertions might not suffice. Great parts of the functionality could happen in a sequential context. Hence, no interaction with the scheduling engine of a simulator is performed.

Monitoring ongoing communication within a system is also a problem. On RTL monitoring the signal-level protocol on the basis of clocks reveals the ongoing interactions of components and processes. On ESL such interactions are usually modeled with functions which are invoked by the caller and are executed in the context of the callee. This kind of function is often called a transaction. Therefore, a solution must be found that enables keeping track of ongoing transactions as well.

#### 2.2.2 Scope of TL Assertions

Additionally, the scope an assertion has on an ESL model has to be contrasted to RTL. On RTL, assertions are usually used to monitor interface contracts within a block, timed handshake protocols, or transition paths in state machines, etc. The scope of an RTL assertion is rather on the internals of a block. Monitoring communication-centric system-level properties within an RTL system would lead to a blow up in complexity of an assertion specification. Hundreds of signals and state variables would have to be considered along with their corresponding temporal relations. On ESL however, these details are not modeled. Therefore, it can be assumed that a TL assertion covers a bigger part of system functionality than RTL assertions.

#### 2.2.3 Communication Patterns and Pipelining

Especially to be able to monitor communication-centric behaviors adequately, assertions need to deal with for instance, "retransmits", pipelined bus structures, data dependent communication flows (data dependent temporal relations), and more. Pipelining as such poses a problem for RTL assertions, since the underlying formal semantics do not support real pipelining. TLMs incorporate many queue-like structures, message buffers, FIFO-based communication channels to decouple sender and receiver, and so forth. In addition to that, if components are modeled which provide pipelined services, monitoring the communication with that model would have to take the pipelining into account as well. Therefore, real pipelined evaluation semantics, at least for dynamic verification methods, must be provided by TL-assertion approaches.

It is also necessary to deal with data dependencies which have an influence on the temporal behavior.

### 2.3 Taken Approach

The approach presented in this work tackles these problems by introducing a framework which amongst others incorporates a new language which is referred to as Universal Assertion Language (UAL) in the remainder of this work and a compiler that generates an implementation of given UAL specifications. UAL follows an eventdriven synchronization approach. However, a general concept of events is introduced which goes beyond the concept of value-change events and other simulation kernel events and allows transactions and other actions to fire events as well. Furthermore, operators on these events are introduced that can handle different abstraction levels for synchronizing assertions including self-synchronization based on time annotations. UAL also supports a general sequence mechanism, which is independent of the underlying abstraction layer and allows the specification of partial orders on events. Evaluation of sequence specifications is triggered by general events. In addition to these concepts, UAL comes with a set of different execution modes, including a real pipelined mode.

# 3 Requirements and Objectives for Transaction Level Assertions

This chapter gathers and explains all specific requirements which have to be met by an assertion language applicable to TLMs. These requirements were developed in an incremental process starting from a small set of key requirements for an assertion language to support transaction level assertions. Further extensions to these requirements were derived from application needs. A summary of all requirements is given in Appendix A in Section A.1. Throughout the following sections, the requirements discussed include references to the corresponding summarized requirements in Section A.1 by referring to particular requirements. The references are given in parenthesis in the form "(R X)" with "R" indicating that the referenced item is a requirement and "X" indicating the corresponding number of the requirement in Section A.1. Section A.2 in Appendix A shows a categorization of all requirements according to whether a requirement has been addressed and its importance for enabling ABV at TL.

## 3.1 Examples for Transaction Level Properties

To give a better impression of what properties monitored by assertions could be at TL, this section provides some informal examples.

#### **Bus Infrastructure Checks**

Checking a bus infrastructure is one possible application for TL assertions. For instance a property that states that the address decoding of the bus yields the correct address map could be:

"Whenever a master module initiates a transaction with address Y, the corresponding transaction is executed on the module where Y lies in the address range of that module!"

A related check is that no other registers are illegally modified.

Another check involving timing as well could be:

"A bus response to a specific request is never issued later than 50 nanoseconds!"

Timing can also be considered more abstract:

"A request is always responded before another request is placed!"

#### **Dataflow Checks**

Dataflow properties could be checked as well:

"A write attempt to a SW visible register implies that the payload is stored into that register once the transaction has finished!"

Furthermore, tracking a data package among several stages could be monitored as well:

"If data is written to a register in an output device, it is required that this data is transported out as soon as the environment is ready!" "If data is written to a buffer, it is required that this data flows out within a maximum amount of time!"

#### Controlflow

Controlflow checks would be possible as well:

"Correct occurrence of data-dependent packet requests!" "The execution of a specific instruction implies the correct sequence of memory-fetch and IO-transactions!"

#### SW-Accesses

Monitoring protocols to indicate wrong SW-accesses to HW -registers could be checked:

"No write attempt to a read-only register occurs!" "No write / read attempt to a full / empty buffer exists!"

#### Configurations

Configurations and their effects could be checked for correctness as well:

"A firing interrupt implies that the interrupt was enabled!"

As the examples indicate, TL properties reason about sequences of transactions and Boolean propositions along these. Hence, a TL assertion approach generally needs to support the specification of transaction sequences (R 1).

# 3.2 Characteristics of SystemC Transaction Level Modeling

TL modeling plays a major role in the success of the development of VPs. It allows breaking down a system to a set of components or blocks comprised of concurrent processes. These blocks communicate with each other via so-called transactions. The following sections give a brief overview on the main characteristics of TL modeling. The explanations are based on the semantics of SystemC<sup>1</sup>, which is the most common language for modeling at TL. Strictly speaking however, SystemC is not a language but a class library built on top of C++. SystemC offers the neat bits for modeling communication, hierarchy, and especially concurrency in an easy fashion in C++.

Due to the relevance of SystemC for TL modeling, it is obvious that a TL assertion approach is required to support the evaluation of assertions on-the-fly during a SystemC simulation (R 2). It is also required to support all SystemC and C++ base types (R 3).

#### 3.2.1 Hierarchy

SystemC offers a concept of hierarchy which allows encapsulation of functional units to modules. These modules can be connected via ports to enable communication. A module can also incorporate another module, thus creating levels of hierarchy. Each module is assigned a unique hierarchical name, which allows referencing a module from anywhere in the system (backdoor access). This is useful for verification purposes. Since a TL assertion can monitor actions in several modules at once, a connection mechanism is required which utilizes a backdoor access to modules and their internals (R 4).

<sup>&</sup>lt;sup>1</sup>A complete introduction to SystemC is omitted. For more information on SystemC the reader is referred to [7]

#### 3.2.2 Concurrency

#### **Simulation Kernel**

Concurrency in SystemC is handled in a very similar fashion as in VHDL [21]. Processes are used to model concurrent actions. The simulation kernel uses a delta-cycle concept for the sequential processing of concurrent statements. It incorporates a process activation list which stores handles to processes which need to be activated in the current delta-cycle. The order of process execution within one delta-cycle is random in order to ensure that no hidden dependencies on the execution order of processes exists, thus preserving the principle of concurrency. In addition to the delta-cycle concept, the kernel supports a model of simulation time which allows the scheduling of processes to specific times. In contrast to VHDL, however, the simulation kernel does not offer postponed passive processes (i.e., processes which are only activated after all regular processes have been executed in the current delta-cycle and may only read signals).

It is imperative not to alter the semantics of the SystemC simulation kernel (R 5). Changing the simulation semantics would require to prove the functional equivalence between the altered version and the OSCI reference simulation kernel. In addition to that, each new release of SystemC would require that all alterations have to be added and checked again. This is error-prone and time-consuming. To ensure that the simulation semantics remain intact, it is therefore required that a TL assertion approach works on top of SystemC, implemented as a class library of its own (R 6).

#### **Event Concept**

By leveraging the event sensitivity of processes or wait statements in conjunction with an event notification mechanism, a user can control the scheduling of processes. Processes can be made sensitive to events either statically (sensitivity lists) or dynamically (wait-statements or next\_trigger-statements). A TL assertion approach has to deal with any kind of event offered by SystemC (R 7). This also requires the possibility to link assertions to any of these events (R 8). These events can be grouped as follows:

• Value-Change Events: These events are emitted by signals as soon as a valuechange has occurred. Using evaluate-update mechanisms, the kernel ensures that a signal value-change can only be obtained with the last assignment to a signal within a delta-cycle. • Custom Events: The user can declare events and add annotations in any procedural context to emit this event. The notification mechanism allows the scheduling of an event to a certain simulation time or the next delta-cycle.

Immediate notification is supported as well. This means, that the scheduled event will be notified in the same delta-cycle where the notification has been processed. The notification of immediate events, however, does not mean that the event is emitted at once. The event is emitted immediately in the current delta-cycle but only after the process which made the notification has either suspended or terminated. Processes which react to immediate event notifications are activated in the same delta cycle.

An event may only have one pending notification. If another scheduling request for an event is made while there is already a pending notification for this event, only the notification survives which has the earliest scheduling time. SystemC also offers event-queues which can store multiple scheduling requests. This means, that if one event is scheduled twice to the same simulation time or delta-cycle, that it will occur twice.

In general, there is no predetermined order on the events to be emitted within one delta-cycle. This means, that the order of calls to schedule two different events to the same delta-cycle has no correlation with the actual order of occurrences of these two events in that delta-cycle.

- Implicit Events: Processes can reschedule themselves by notifying implicit events. The notification of implicit events leads to an immediate suspension of the emitting process. Since these events are not visible to any other process, a TL approach requires a mechanism that allows tracking of these events as well, however, with no change of the simulation kernel (R 9, and R 5). Two different implicit events can be emitted by a process.

- Zero-Delay events: Through the notification of an implicit zero-delay event, a process reschedules itself to wake up at the next delta-cycle. Such a notification is accomplished by using timed wait statements, which take a time parameter. The value of this parameter equals 0 to enforce a delta-cycle delay (wait(0,SC\_NS)) for that process.

- Timed-Delay events: A process can also reschedule itself to a specific simulation time later than the current time. The corresponding notification is obtained through the use of timed wait statements with a non-zero time parameter (e.g., wait(10,SC\_NS)).

#### 3.2.3 Synchronization

Basically, SystemC offers two types of processes for modeling concurrent behavior:

- Suspendable: The execution of such a process can be partitioned into several parts by suspending it. When such a process suspends, it saves its whole context. Once the process wakes up, it restores its context and resumes from where it has stopped. Suspendable processes are modeled using the SC\_THREAD macro offered by SystemC. A suspendable process may be put to sleep using the wait statement offered by SystemC. It can either wait until a certain amount of simulation time (implicit timed event) has passed (e.g., wait(10,SC\_NS)) or until the next occurrence of a specific event (e.g., wait(0,SC\_NS)).

- Non-Suspendable: The execution of such a process may never be suspended. Once executed, the process runs until its last instruction. Hence, the complete execution of a non-suspendable process happens within one delta-cycle. Non-Suspendable processes are modeled using the SC\_METHOD macro offered by SystemC. In order to enable an assertion based monitoring of actions within a non-suspendable process, it is required to support a more granular time resolution than delta-cycle resolution (R 10).

Both types may have a sensitivity list where all events are specified which may invoke the process. Suspendable processes are avoided as best as possible since the induced context switching is very expensive with regard to performance.

#### 3.2.4 Communication

A transaction represents a high-level form of a communication protocol. All protocolspecific details are encapsulated within a transaction. Hence, the actual act of initiating a transaction results in a remote function call from a process (parent). A designer focuses more or less on the data that has to be transported rather than the protocol specifics.

Transactions are modeled as functions which are defined in pure virtual interface classes and implemented in corresponding child classes which inherit the interface. The implementation details of a transaction strongly depend on the targeted abstraction level. Yet two distinctions with regard to transactions can be made:

• Blocking: A blocking transaction may suspend its parent process which means that the transaction is resumed in a later delta-cycle. This kind of transaction can be invoked in suspendable processes, only (i.e., SC\_THREAD).

• Non-Blocking: A non-blocking transaction is atomic and may not suspend its parent process; the whole transaction is executed within the same delta-cycle it has been invoked. This kind of transaction can be called from within any process (i.e., SC\_THREAD and SC\_METHOD).

Invoking a transaction results in dereferencing a pointer that holds the address of the target object and in calling a member function of that object. The whole call or even several calls can happen within a single delta-cycle (e.g., with non-blocking transactions). In contrast to that, communication in RTL models is obtained via signals and hence, always consumes at least one delta-cycle due to the induced valuechanges that form the protocol. Therefore, with signal based protocols it is sufficient to monitor the values of the participating signals at a granularity of delta-cycles in order to detect ongoing transactions. Since, this does not suffice at TL, it is required that a TL assertion approach is able to detect transaction calls (R 29, and R 10) in order to enable the tracking of transaction sequences (R 1). This also requires that assertions gain access to transaction return values and arguments (R 12) and that both blocking and non-blocking transactions are supported (R 11).

In order to ensure easy IP reuse and interoperability, a TL modeling standard [8] has been developed by OSCI. This standard defines different interfaces including transaction signatures and argument types. Clearly, the support of this standard by a TL assertion approach is required as well (R 13).

#### 3.2.5 Abstraction Levels

As mentioned in the previous chapter, the key factor for the success of the ESL domain is abstraction. The objectives which determine the required abstraction level for a TLM depend on the intent of analysis: The more abstract a model is the higher the performance of a simulation becomes but the less information is available for analysis. Therefore, the chosen level of abstraction is a trade-off between performance and information. This issue has so far hindered the establishing of standards which define abstraction levels and provide guidelines on how to model at a certain abstraction. However, a common nomenclature for TL abstraction levels has been developed in conjunction with the OSCI TLM standard. Unfortunately, the definition is not exact and allows for some interpretation. The four terms that have been developed are:

- Programmer's View (PV): Access to the system does not consider timing; correct data and control flow are focused.

- Programmer's View with Timing (PVT): Additional to PV, approximate timing of system accesses is considered as well.

- Cycle Approximate (CA): System accesses are resolved in cycles.

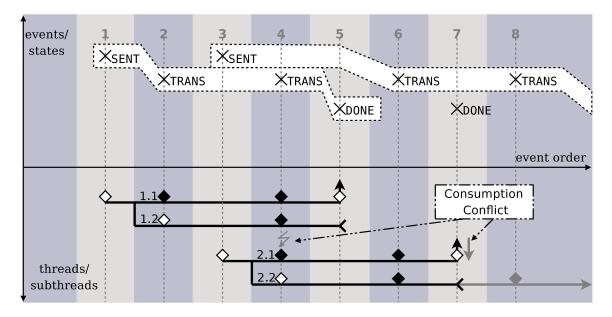

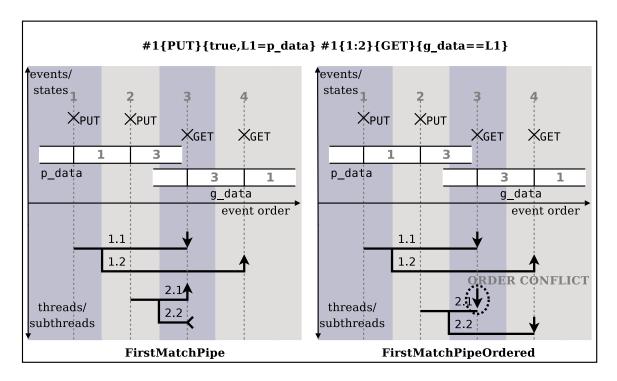

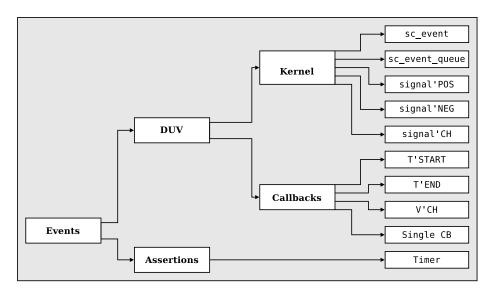

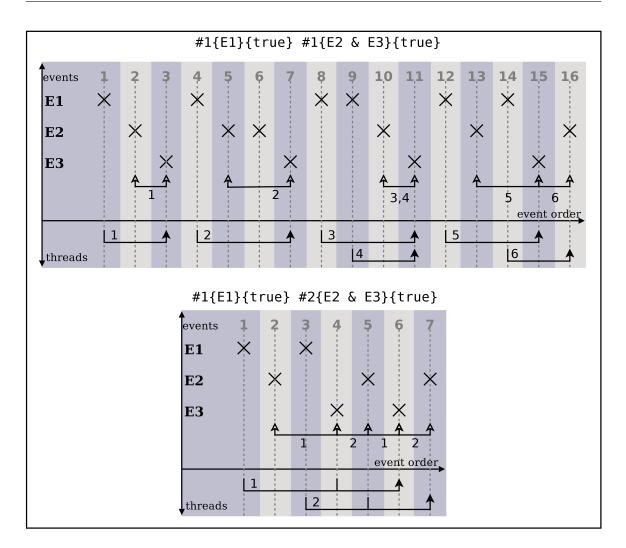

- Cycle Callable (CC): System accesses are clocked as in RTL but the communication is still modeled with transactions in contrast to signals.