# Evaluation of a Dual-T-type Converter Supplying an Open-End winding Induction Machine

A. Salem, F. De Belie, A. Darba, M. Eissa, S.M. Wasfy and J. Melkebeek

Abstract—The multilevel inverter is a promising technology compared to two-level inverters in the applications of ac-drives and smart-grid applications. In this paper, a dual-T-type threelevel inverters is used to drive an open-end winding induction machine. The Space-Vector Pulse-Width Modulation is selected as a good-performing control strategy to control the dual-inverter. A comparison between the proposed configuration and the conventional diode clamped converter is included. The proposed drive system is designed and modeled by using Matlab/Simulink. It is shown that the converter gives the same hexagon, wave forms and harmonic spectrum of the five level converter. An optimized switching state selection is used to reduce the converter losses. The advantages and drawbacks of the dual-T-type configuration are discussed. In addition, the harmonic analysis and the loss calculations of the dual-T-type converter are provided and compared to the T-type three-level converter and the conventional five-level diode-clamped-converter.

Index Terms—Multilevel converter, Diode-clamped-Converter, T-type converter

#### I. INTRODUCTION

In the last decade, the demand for high-power converters is increased. This growing demand has received the attention of most researchers in academia and in industry. The multilevel inverter is a more powerful topology compared to the two-level inverter because of lower harmonic content and higher power and voltage ratings. The conventional multilevel inverter is classified into cascaded H-bridge topology, flying-capacitor and diode-clamped inverters. These topologies have the problem of complexity in the power circuit. Within the class of multilevel converters, the diodeclamped converter (DCC) is the most used as it does not need separated power supplies for the three phases as in the case for the cascaded type. Furthermore there is no need for capacitor pre-charged as in flying-capacitor type. In [1], a new configuration for the diode-clamped inverter is introduced to reduce the blocking voltage on the semiconductor switches; however the power circuit becomes more complicated. In [2], the cascaded H-bridge converter is introduced operating as a single-phase inverter and if applied to three-phase system, it will need more separated dc-power supplies. In [3], the T-type converter is introduced as a new topology suitable for low-voltage applications and this converter is proved to be a suitable ac-drive because of lower converter losses compared to three-level neutral-point-clamped (NPC) converter. In this paper, a dual-T-type converter is used to drive an open-end-winding induction machine (OEWIM). The OEWIM is the a three-phase induction machine with stator windings opened from both coil sides for all three phases. By using Space-Vector Pulse-Width Modulation (SVPWM), 729 switching states can be chosen while the conventional five-level DCC has only 125 switching states. The higher the number of states, the higher the facility to select a switching element. The switching strategy in this paper reduces the converter losses for the T-type converter in the configuration of a dual-converter compared to conventional five-level DCC. A Matlab/Simulink tool is used for simulating the dual-T-type inverter driving an OEWIM at a full-load operation. A brief discussion for the SVPWM control strategy is included. The dual-T-type inverter is evaluated by performing harmonic analysis and by comparing these results to those of the T-type converter supplying an induction machine. Moreover, the power losses of the proposed dual-T-type converter are calculated and compared to a conventional five-level DCC and T-type converter.

# II. PROPOSED MULTILEVEL INVERTER TOPOLOGY

The five-level inverter has many topologies used in industrial work. One promising topology is the diode-clamped converter. This topology is favourable because of using common dc-links compared to an hybrid multilevel converter and did not need for pre-charging operation as flying-capacitor converter type. In [3], a T-type converter introduced and proved to be a good three-level topology for low voltage applications. In this paper, a dual-T-type converter is used as a five-level converter to drive an open-end winding induction machine. The advantages of this configuration to the conventional diode clamped converter summarised as follow:

- The same Hexagon, wave forms and harmonic spectrum is similar as five-level converter.

- The number of operating switching states increased.

- Converter losses decreased compared to DCC.

- The clamping diodes are removed from the circuit.

- More reduction in conduction losses due to clamping diode elimination and simplification of the power circuit.

These advantages give the priority to use this topology as a five-level converter for low voltage applications.

The drawback of the proposed dual-T-type converter is the higher open-circuit voltage on the upper and lower switches  $(S_1, S_3)$  of the T-type converter compared to the clamping switches [3].

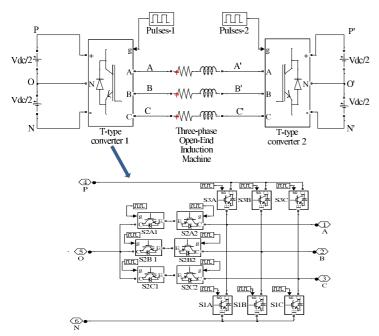

The configuration for the converter connected to OEWIM is shown in Figure 1.

The three-phase voltages are generated as the voltage difference between the T-type inverters. In Table I, the operation for phase A is summarized as follow:

# III. SVPWM TECHNIQUE USING DUAL-CONVERTER

The switching states for the m-level inverter equals to  $m^3$ . For a three-level inverter the number of switching states

1

Figure 1: Dual-inverter connected to OEWIM

$\label{eq:Table I} \textbf{Table I}$  Operation of dual-inverter operates OEWIM for Phase A

| INV1               | INV2                 | machine terminal | $V_{AA'}$            |

|--------------------|----------------------|------------------|----------------------|

| switching          | switching            | connected to DC  |                      |

| $S_{3A}$           | $S_{1A'}$            | P-N'             | $+$ $V_{dc}$         |

| $S_{3A}$           | $S_{2A1'}, S_{2A2'}$ | P-O'             | $+ V_{dc}/2$         |

| $S_{3A}$           | $S_{3A'}$            | P-P'             | zero                 |

| $S_{2A1}, S_{2A2}$ | $S_{1A'}$            | O-P'             | - V <sub>dc</sub> /2 |

| $S_{2A1}, S_{2A2}$ | $S_{1A'}$            | N-P'             | - $V_{dc}$           |

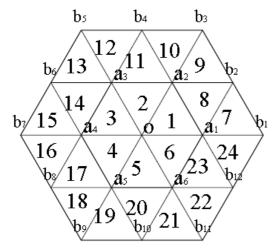

is 27 states. These switching states are summarized in the three-level hexagon shown in Figure 2.

Figure 2: Three-level inverter hexagon

The vector in the origin o represents the zero vectors, the vectors ( $a_1$  to  $a_6$ ) correspond to the two-level hexagon vectors states and the vectors ( $b_1$  to  $b_{12}$ ) correspond to the three-level hexagon vectors states. In Table II, the switching states which give the vectors o,  $a^{\circ}$  s,  $b^{\circ}$ s are given. Furthermore, the meaning of state zero, one and two in term of switching states is given. It is assumed that the zero state means that

$\label{thm:continuity} \textbf{Table II} \\ \textbf{SWITCHING STATES FOR THE THREE-LEVEL RNPC INVERTER} \\$

| vector         A         B         C         vector         A           O         0         0         0         b1         2           O         1         1         1         b2         2           O         2         2         2         b3         2           b4         1         1         a1         1         b4         1           a1         2         1         1         b6         0         a2         a1         a5         0           a2         1         1         0         b7         0         a2         a2         a2         a1         b8         0           a3         0         1         0         b9         0         a3         a1         a2         a1         b10         1         a4         0         a1         b11         a2         a4         a4         a2         b12         a2         b12         a2         a5         0         0         a6         1         a6         1 |   |   |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|--|--|--|--|

| O 1 1 1 1 b2 2 O 2 2 2 b3 2 b4 1 a1 1 0 0 b5 0 a1 2 1 1 b6 0 a2 1 1 0 b7 0 a2 2 2 1 b8 0 a3 0 1 0 b9 0 a3 1 2 1 b10 1 a4 0 1 1 b11 2 a4 1 2 2 b12 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | В | C |  |  |  |  |

| O 2 2 2 b3 2  a1 1 0 0 b5 0  a1 2 1 1 b6 0  a2 1 1 0 b7 0  a2 2 2 1 b8 0  a3 0 1 0 b9 0  a3 1 2 1 b10 1  a4 0 1 1 b11 2  a4 1 2 2 b12 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 | 0 |  |  |  |  |

| a1         1         0         0         b5         0           a1         2         1         1         b6         0           a2         1         1         0         b7         0           a2         2         2         1         b8         0           a3         0         1         0         b9         0           a3         1         2         1         b10         1           a4         0         1         1         b11         2           a4         1         2         2         b12         2                                                                                                                                                                                                                                                                                                                                                                                                           | 1 | 0 |  |  |  |  |

| a1         1         0         0         b5         0           a1         2         1         1         b6         0           a2         1         1         0         b7         0           a2         2         2         1         b8         0           a3         0         1         0         b9         0           a3         1         2         1         b10         1           a4         0         1         1         b11         2           a4         1         2         2         b12         2                                                                                                                                                                                                                                                                                                                                                                                                           | 2 | 0 |  |  |  |  |

| a1         2         1         1         b6         0           a2         1         1         0         b7         0           a2         2         2         1         b8         0           a3         0         1         0         b9         0           a3         1         2         1         b10         1           a4         0         1         1         b11         2           a4         1         2         2         b12         2                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2 | 0 |  |  |  |  |

| a2     1     1     0     b7     0       a2     2     2     1     b8     0       a3     0     1     0     b9     0       a3     1     2     1     b10     1       a4     0     1     1     b11     2       a4     1     2     2     b12     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 | 0 |  |  |  |  |

| a2     2     2     1     b8     0       a3     0     1     0     b9     0       a3     1     2     1     b10     1       a4     0     1     1     b11     2       a4     1     2     2     b12     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2 | 1 |  |  |  |  |

| a3     0     1     0     b9     0       a3     1     2     1     b10     1       a4     0     1     1     b11     2       a4     1     2     2     b12     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 | 2 |  |  |  |  |

| a3     1     2     1     b10     1       a4     0     1     1     b11     2       a4     1     2     2     b12     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 | 2 |  |  |  |  |

| a4     0     1     1     b11     2       a4     1     2     2     b12     2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 | 2 |  |  |  |  |

| a4 1 2 2 b12 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 | 2 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 | 2 |  |  |  |  |

| a5 0 0 1 a6 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 | 1 |  |  |  |  |

| a 0 0 1 a0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0 | 1 |  |  |  |  |

| a5 1 1 2 a6 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 | 2 |  |  |  |  |

| swithing states                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |   |  |  |  |  |

| state | $S_{1A}$ | $S_{2A1}$ | $S_{2A2}$ | $S_{3A}$ |  |

|-------|----------|-----------|-----------|----------|--|

| 0     | 0        | 0         | 1         | 1        |  |

| 1     | 0        | 1         | 1         | 0        |  |

| 2     | 1        | 1         | 0         | 0        |  |

the switches  $S_{3A}$  and  $S_{2A2}$  are turned on, the state one means that the intermediate switches  $S_{2A1}$  and  $S_{2A2}$  are turned on and state two means that the switches  $S_{1A}$  and  $S_{2A1}$  are turned on. In a five-level inverter, the DCC produces a hexagon of 125 switching states with 63 vectors. The vectors are one O vector, 6 vectors for a, 12 vectors for b, 18 vectors for c and 24 vectors for d. The hexagon of the five-level inverter is shown in Figure ??.

For the dual-T-type inverter topology, there are two three-level inverters represented by two identical hexagons. This results in 63 vectors to be chosen from. The number of switching states using this topology is 729. Both dual-T-type converter and five-level converter can be represented by the same 63 vectors. However the dual-T-type converter has more switching states resulting in a better facility of selecting more suitable switching sates

The strategy of selecting the proper state from a number of states is base on:

- Selecting the state for one converter to change state (from 0 to 1 or vies versa) state with a minimum number of commutation and,

- Keep the other converter without changing switching

This results in reducing converter losses, reducing the switching stress on the converter power switches and increasing the converter life time.

The combination of 729 switching states is to much to be listed here but Table III represent the beginning and the end of the switching states.

The states for each three-level inverter as seen before are 0, 1 and 2. So the switching states can take numbers from 1 to 27. For example, switching state 1 means (0 0 0) for the three phases, the switching state 15 means (1 1 2) and switching state 27 means (2 2 2). For the dual-T-type converter, 15-14' switching state means that inverter-1 has the state of 15 and inverter-2 has the state of 14.

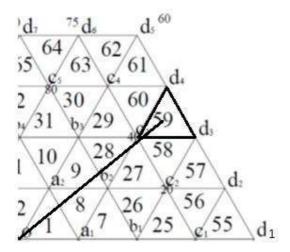

The following is an example for the switching pattern for the dual-T-type converter. Assume a vector with a modulation index of 0.85 and an angle of  $45^{\circ}$ . This vector is located in

the region number 59. The suitable switching pattern for this location is shown in Figure 3.

The basic for the time calculation for the three-level hexagon for a complete sector regions si described in [4]-[7]. For the five-level hexagon, there are 16 regions in the sector, and 96 regions for one cycle of vector revolution. The time calculations are performed by the same way as for the three-level hexagon time calculations for the 16 regions. The other sectors have the same regions equations.

After the time calculation, the switching pattern for this example generated with the base of the proposed switching strategy. The pattern for the example shown in Figure 4.

$\label{thm:converter} \begin{tabular}{ll} Table \ III \\ SWITCHING \ STATES \ FOR \ THE \ FIVE-LEVEL \ INVERTER \ USING \ DUAL-T-TYPE \\ CONVERTER \end{tabular}$

| INV1      | INV2      | five-level | space           |  |

|-----------|-----------|------------|-----------------|--|

| switching | switching | switching  | space<br>Vector |  |

| 1         | 1         | 1-1'       | 0               |  |

| 2         | 1         | 2-1'       | A5              |  |

| 1         | 1         | 1-1'       | В9              |  |

|           |           |            |                 |  |

| -         | •         |            |                 |  |

| •         |           |            |                 |  |

| 27        | 27        | 27-27'     | O               |  |

Figure 3: Vector location with 0.85 Modulation index and 45°

### IV. SIMULATIONS

The SVPWM stearing the dual-T-type converter to drive an OEWIM is simulated using Matlab/Simulink program. The machine rating is 50 hP and the parameters are included in Appendix 1. The simulation of the proposed system presents the machine operation and studies the converter performance by harmonic analysis evaluation. A comparison between the proposed drive system and the T-type converter supplying an induction machine based on the harmonic spectra is included. In another section of the simulation, a power losses comparison between the proposed dual-T-type converter, conventional five-level DCC and the T-type converter is included.

|            |       | T0/2 | T1 | T2 | T0/2 | T0/2 | T1 | T2 | T0/2 |

|------------|-------|------|----|----|------|------|----|----|------|

|            | INV-1 | 10   | 19 | 22 | 23   | 23   | 22 | 19 | 10   |

|            | INV-2 | 3    | 3  | 3  | 3    | 3    | 3  | 3  | 3    |

|            |       |      |    |    |      |      |    |    |      |

|            |       | 1    | 2  | 2  | 2    | 2    | 2  | 2  | 1    |

|            | Α     |      |    |    |      |      |    | l  |      |

|            |       |      |    |    |      |      |    |    |      |

| Inverter-1 | _     | 0    | 0  | 1  | 1    | 1    | 1  | 0  | 0    |

| Ħ          | В     |      |    |    |      |      |    |    |      |

| M          |       |      |    |    |      |      |    |    |      |

| Z          | С     | 0    | 0  | 0  | 1    | 1    | 0  | 0  | 0    |

|            |       | _    | _  | _  |      |      |    | _  | _    |

|            |       |      |    |    |      |      |    |    |      |

|            |       |      |    |    |      |      |    |    |      |

|            | _     | 0    | 0  | 0  | 0    | 0    | 0  | 0  | 0    |

| INVERTER-2 | A'    | •    | •  | ū  | •    | Ū    | •  | •  | •    |

|            |       |      |    |    |      |      |    |    |      |

|            |       | 0    | 0  | 0  | 0    | 0    | 0  | 0  | 0    |

|            | B'    | •    | •  | -  | •    | •    | -  | -  | -    |

|            |       |      |    |    |      |      |    |    |      |

| _          |       | 2    | 2  | 2  | 2    | 2    | 2  | 2  | 2    |

|            | C'    | -    | -  | _  | -    | _    | -  | -  | _    |

|            |       |      |    |    |      |      |    |    |      |

Figure 4: Switching pattern for region 59

# A. SIMULATION of OEWIM WITH DUAL-T-TYPE CONVERTER USING MATLAB/SIMULINK

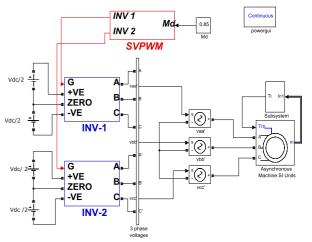

The block diagram for the OEWIM driven by dual-T-type converter using Matlab/Simulink is shown in Figure 5.

Figure 5: Proposed system Matlab/Simulink block diagram

The system simulates SVPWM with a modulation index of 0.85 and a switching frequency of 4.8 kHz. The simulation results are summarized as follow:

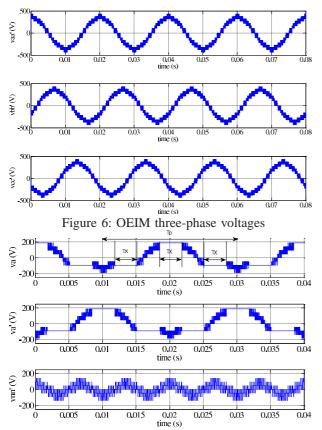

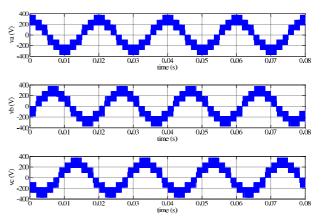

- Figure 6 shows the three-phase voltages of the OEWIM.

- Figure 7 shows the terminal voltage for phase A for both T-type converters and the voltage between the negative points(N, N' Figure 1) of both converters. The voltages  $V_a$  and  $V_{a'}$  have a period  $T_p$ . Each converter switching state is fixed during time intervals  $T_p$ . Each interval of  $T_x$  corresponds to  $60^o$  of the period  $T_p$ . So the dual converters are without switching for half of the power period  $T_p$ .

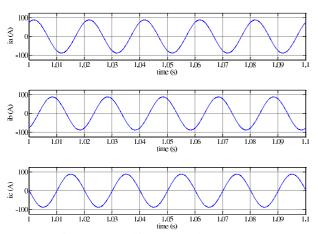

- Figure 8 shows the three-phase currents for the machine at steady state. The wave form of the current appears as harmonic free, this is due to the machine impedance which damps the harmonic contents in the current.

Figure 7: Dual-converter terminal voltages and voltage between negative points

Figure 8: machine three-phase currents

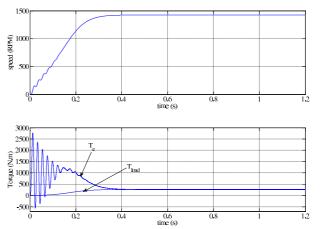

- By using the three-phase voltage generated by SVPWM shown in Figure 6, the machine speed and the machine electrical torque  $T_e$  compared to a fan load torque  $T_{load}$  for full load operation are shown in Figure 9.

- Figure ?? shows the machine torque speed characteristics with a rated fan load torque.

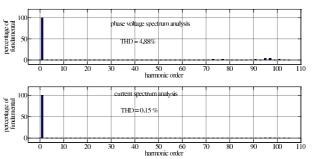

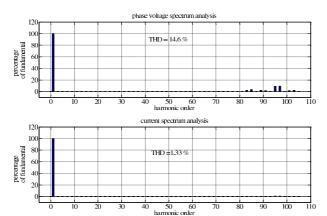

- Figure 10 shows the spectrum diagram resulting from the harmonic analysis for the phase voltage and current.

The spectrum shoe the harmonic orders for voltage and current up to 115 harmonic order.

The  $V_{NN'}$  is the triple harmonic content of the generated phase voltage. If the point N and N' are connected together, the output phase voltage will include the third harmonic

Figure 9: Machine speed and electrical with load torque

Figure 10: Spectrum analysis for the machine phase voltage and current

component. So these points must be isolated or using a power filter to prevent third harmonic current flow. For renewable energy sources such as Photo-Voltaic and Fuel-Cell applications, the dc-sources are isolated. Also for electric vehicles, the batteries can be isolated. So this converter is promising for the renewable energy and smart grid applications.

There is a solution for the triple harmonic elimination without using filters or isolated dc-power supply. This solution is to use common dc-sources for the converter as in [8] however another four bidirectional switches are needed.

A Matlab/Simulink model is built for the T-type converter supplying an induction machine. Figure 11 shows the three-phase voltages of the induction machine. The spectrum of the T-type converter voltage and current are shown in figure 12.

Figure 11: Three-phase voltage of the induction machine supplied by T-type converter

Figure 12: Spectrum analysis for the machine phase voltage and current supplied by T-type converter

#### B. POWER-LOSSES CALCULATIONS

The losses of the power-electronics devices are calculated with different strategies. In [9]- [13], the power losses for the two-level inverter and other dc-to-dc converters are analysed for different modulation strategies assuming a fixed switching frequency. For the losses in multilevel converters, assuming a fixed switching frequency is not correct. In [14] the loss equations for a five-level diode clamped and flying capacitor converter are derived but in a complex way.

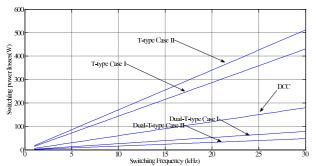

In this section, the power losses are calculated for proposed dual-T-type converter, T-type converter and conventional five-level DCC. The T-type converter losses are calculated using the switching technique listed in table II.

The power losses classified to switching losses and conduction losses. The switching-loss calculations are based on the following steps:

- Obtain the IGBT parameters from the data-sheet.

- For each switch, calculate the number of turn-on and turnoff per power cycle using Matlab/Simulink.

- Use the following equations for switching power losses

[15]:

$$P_{son} = \frac{1}{8} V_{dc} t_{rn} f_s \frac{I_{cm}^2}{I_{cn}} \tag{1}$$

$$P_{soff} = V_{dc}I_{cm}t_{fn}f_{s}(\frac{1}{3\pi} + \frac{1}{24\pi}\frac{I_{cm}}{I_{cn}})$$

(2)

$$P_{sw} = P_{son} + P_{soff} \tag{3}$$

Where  $P_{son}$  is the turn-on switching loss,  $P_{soff}$  is the turn-off switching loss,  $P_{sw}$  is the total switching losses,  $V_{dc}$  is the open-circuit voltage on the switch,  $t_{rn}$  is the rated rising time,  $t_{fn}$  is the rated falling time,  $f_s$  is the switching frequency,  $I_{cm}$  is the maximum collector current and  $I_{cn}$  is the rated collector current.

The conduction losses for dual-T-type converter and five level DCC are calculated using the following equation [16]:

$$P_{con} = V_o I_{av} + I_{rms}^2 R_o \tag{4}$$

where  $P_{con}$  is the conduction power loss,  $I_{av}$  is the average value for the collector current,  $I_{rms}$  is the root-mean-square value of the collector current,  $V_o$  is the collector-to-emitter voltage during conduction period and  $R_o$  is the

resistance of the semiconductor during conduction. The conduction losses for diode is calculated by the same way as IGBTs.

In the simulation, the losses are calculated with the machine operation at full load. The switching and conduction losses are calculated for each switch. The IGBT parameters are obtained from the data sheet for 100A collector current and collector-toemitter voltage of 600V and 1200 Voltage. The switches code numbers are GT100DA60U and GT100DA120U from Vishay Semiconductors company. The loss calculation is based on using the 600V IGBT for all switches of the conventional DCC, using 600V IGBT for clamping switches only and 1200V for the upper and lower switches of T-type converter. For the machine rating of 460V line voltage, the value of the dc-link voltage for each separated supply is 162V. So the 600V IGBT is sufficient for the upper and lower switches of the Ttype converter switches. For this reason the loss calculation for the dual-converter configuration is performed in the following cases:

- Case I: The upper and lower switches with 1200V IGBT's and the clamping switches with 600V IGBT's.

- Case II: Using the 600V IGBT for all the converter switches.

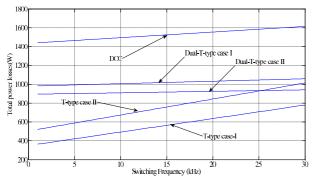

Table IV shows the switching and conduction losses for dual-T-type converter, five-level DCC and T-type converters.

Converter switching conduction total converter case losses (W losses (W) losses (W) efficiency Dual-T-type. INV-1 24.3 489.6 513.9 case I INV-2 24.3 489.6 513.9 1027.8 97.61 % total Dual-T-type. INV-1 446.6 11.9 458.5 case II INV-2 11.9 446.6 458.5 total 917 97.86 % 21.25 1434.6 IGBT's 1455.85 conventional DCC Diodes 144.91 converter Total 1600.76 96.33 % 95.64 347 98.96 % T-type. 442.64

Table IV

POWER LOSSES SUMMARY

It is clear from the table that the switching losses for the dual-converter in case-I is approximately twice the value of the DCC switching losses. For case-II the switching losses are approximately the same. For the conduction losses, these losses are for both cases much lower than the conduction losses of the conventional DCC. This reduction in conduction power losses has not only resulted from removing the clamping diodes, but from the switching strategy used with the dual-converter configuration as well.

Figure 13 and 14 show respectively the switching and total power losses as a function of the switching frequency for a wide range band (from 1 kHz to 40 kHz). It is clear that the proposed configuration in this paper reduces the power losses for the converter. For the T-type converter, for a switching frequency lower than 31 kHz, the T-type converter loss is lower than the dual-T-type converter loss. If the switching frequency increased, the T-type converter loss is increased over the dual-T-type converter case II. The T-type converter loss is the smallest but the harmonic spectra is the highest compared to dual T-type converter.

Figure 13: Switching losses for the dual-T-type converter compared to five-level DCC and T-type converter

Figure 14: Total power losses for the dual-T-type converter compared to five-level DCC and T-type converter

### V. CONCLUSIONS

An OEWIM drive, including an induction machine supplied by a dual-T-type converter from both ends, results in more possible switching states. This increase in switching states, makes it possible to decrease the converter losses by selecting a proper switching pattern. The total conduction loss calculation indicates that removing the clamping diodes is a minor factor in decreasing the losses. The T-type converter has the lowest total losses but with more harmonic contents compared to the dual-T-type converter. The dual-T-type converter dc-power supply is isolated to prevent third harmonic flow. This isolation led to make the converter more suitable for renewable energy (as Photo-Voltaic and Fuel-Cell), electric vehicles, and smart grid applications.

### REFERENCES

- X. Yuan and I. Barbi, "Fundamentals of a New Diode Clamping Multilevel Inverter, *IEEE Trans. of Power Electronics*, Vol. 15, No. 4, July 2000.

- [2] G. Murugesan, "A New Multilevel Inverter Topology Using Less Number Of Switches," *International Journal of Engineering Science and Technology (IJEST).*, Vol. 3, No. 2, pp. 1500-1510, Feb. 2011.

- [3] M. Schweizer, J. W. Kolar, "Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications," *IEEE Trans. Power Electron.*, Vol. 28, No. 2, pp. 875-888, Feb. 2013.

- [4] B. K. Bose, "Modern power electronics and AC drives," Book, USA: Prentice Hall PTR, 2002..

- [5] S. Ahmed, G. Sowilam, M. Abdelkader, "Comparison study between three phase three level inverter techniques," *The tenth international Middle East power system conference*, pp. 353-362, Dec. 2005.

- [6] S. Ahmed, G. Sowilam, M. Abdelkader, "microcontroller based control unit of space vector PWM inverter fed induction motor drive," *The tenth* international Middle East power system conference, pp. 363-370, Dec. 2005.

- [7] J. Rodriguez, J. S. Lai, F. Z. Peng, "Multilevel Inverters: Survey of Topologies, Controls, and Applications," *IEEE Trans. on Industry Applications*, Vol. 49, No. 4, pp. 724-738, Aug. 2002.

- [8] K. Mohapatra, K. Gopakumar, V. T. Somasekhar, L. Umanand, "A Harmonic Elimination and Suppression Scheme for an Open-End Winding Induction Motor Drive," *IEEE Trans. on Industry Electronics*, Vol. 50, No. 6, pp. 1187-1198, Dec. 2003.

- [9] M. H. Bierhoff, "Semiconductor Losses In Voltage Source and Current Source IGBT Converters Based on Analytical Derivation," *The 35th Annual PESC*, Vol. 4, pp. 2836-1198, 2004

[10] Johann W. Kolar, "In Influence of the Modulation Method on the

- [10] Johann W. Kolar, "In Influence of the Modulation Method on the Conduction and Switching Losses of a PWM Converter System," *IEEE transaction on industry application*, Vol. 27, No. 6, Nov. 1991.

- [11] A. Trzynadlowski, S. Legowski, "Minimum-Loss Vector PWM Strategy for Three-phase Inverters," *IEEE Trans. an Power Elect.*, vol. 9, No. 1, pp. 26-34, Jan. 1994.

- [12] O. Hegazy, J. Mierlo, P. Lataire, "Analysis, Modelling, and Implementation of a Multi-device Interleaved DC/DC Converter for Fuel Cell Hybrid Electric Vehicles," *IEEE Transaction on Power electronics*, vol. 27, no. 11, Nov. 2012.

- [13] L. Meslha, P. Evans, "Analysis of On-State Losses in PWM Inverters," *IEE Proceedings*, vol. 136, Pt. E, No. 4, July 1989.

[14] F. Gebhardt, H. Vach, F. Fuchs, "Analysis, Analytical Derivation of

- [14] F. Gebhardt, H. Vach, F. Fuchs, "Analysis, Analytical Derivation of Power Semiconductor Losses in MOSFET Multilevel Inverters," EPE-PEMC ECCE Europe, Novi Sad, Serbia.2012.

- [15] F. Cmanellm, "Losses in PWM inverters using IGBTs," IEE Proc.-Electr. Power Appl., vol. 141, No. 5, pp. 235-239, Sept. 1994.

- [16] D. Graovac, M. Purschel, "IGBT Power losses Calculation Using Datasheet Parameters," Application Note - INFINEON com., vol. 1.1, Sept. 2009

#### APPENDIX 1:

50 hP, 460V, 50Hz, four poles Induction machine.  $r_s$  = 0.087  $\Omega,~r_r$  = 0.228  $\Omega,~L_{ls}$  = $L_{lr}$ = 0.0355 H  $L_m$  = 0.0347 H, J = 1.662  $kg.m^2$