Linköping Studies in Science and Technology

Thesis No. 919

# A Petri Net based Modeling and Verification Technique for Real-Time Embedded Systems

by

Luis Alejandro Cortés

Submitted to the School of Engineering at Linköping University in partial fulfillment of the requirements for the degree of Licentiate of Engineering

Department of Computer and Information Science Linköpings universitet SE-581 83 Linköping, Sweden

Linköping 2001

# A Petri Net based Modeling and Verification Technique for Real-Time Embedded Systems

by

Luis Alejandro Cortés

December 2001 ISBN 91-7373-228-1 Linköping Studies in Science and Technology Thesis No. 919 ISSN 0280-7971 LiU-Tek-Lic-2001:56

#### ABSTRACT

Embedded systems are used in a wide spectrum of applications ranging from home appliances and mobile devices to medical equipment and vehicle controllers. They are typically characterized by their real-time behavior and many of them must fulfill strict requirements on reliability and correctness.

In this thesis, we concentrate on aspects related to modeling and formal verification of realtime embedded systems.

First, we define a formal model of computation for real-time embedded systems based on Petri nets. Our model can capture important features of such systems and allows their representations at different levels of granularity. Our modeling formalism has a welldefined semantics so that it supports a precise representation of the system, the use of formal methods to verify its correctness, and the automation of different tasks along the design process.

Second, we propose an approach to the problem of formal verification of real-time embedded systems represented in our modeling formalism. We make use of model checking to prove whether certain properties, expressed as temporal logic formulas, hold with respect to the system model. We introduce a systematic procedure to translate our model into timed automata so that it is possible to use available model checking tools. Various examples, including a realistic industrial case, demonstrate the feasibility of our approach on practical applications.

This work has been supported by the Swedish Agency for Innovation Systems—VINNOVA (formerly Swedish National Board for Industrial and Technical Development—NUTEK).

Department of Computer and Information Science Linköpings universitet SE-581 83 Linköping, Sweden

# A Petri Net based Modeling and Verification Technique for Real-Time Embedded Systems

Luis Alejandro Cortés

INSTITUTE OF TECHNOLOGY

ISBN 91-7373-228-1 ISSN 0280-7971 PRINTED IN LINKÖPING, SWEDEN BY LINKÖPING UNIVERSITY COPYRIGHT © 2001 LUIS ALEJANDRO CORTÉS

To my Family

# Abstract

EMBEDDED SYSTEMS are used in a wide spectrum of applications ranging from home appliances and mobile devices to medical equipment and vehicle controllers. They are typically characterized by their real-time behavior and many of them must fulfill strict requirements on reliability and correctness.

In this thesis, we concentrate on aspects related to modeling and formal verification of real-time embedded systems.

First, we define a formal model of computation for real-time embedded systems based on Petri nets. Our model can capture important features of such systems and allows their representations at different levels of granularity. Our modeling formalism has a well-defined semantics so that it supports a precise representation of the system, the use of formal methods to verify its correctness, and the automation of different tasks along the design process.

Second, we propose an approach to the problem of formal verification of real-time embedded systems represented in our modeling formalism. We make use of model checking to prove whether certain properties, expressed as temporal logic formulas, hold with respect to the system model. We introduce a systematic procedure to translate our model into timed automata so that it is possible to use available model checking tools. Various examples, including a realistic industrial case, demonstrate the feasibility of our approach on practical applications.

# Acknowledgements

I WOULD LIKE TO EXPRESS my sincere gratitude towards Professor Zebo Peng and Professor Petru Eles for their invaluable guidance and constant support throughout my graduate studies.

I have enjoyed the time I have spent at IDA. I am very grateful to those people who, in a way or another, have contributed to making this thesis possible. My colleagues at the Embedded Systems Laboratory (ESLAB) have created a friendly working environment. Thank you all.

Many thanks to Peter Lind at Saab Bofors Dynamics AB for providing the necessary insight about the industrial case studied in this thesis.

Thanks, Dad and Mom, for being my great teachers. Finally, I would like to thank my wife, Lina María, for her love, patience, and encouragement.

Luis Alejandro Cortés Linköping, December 2001

# Contents

| 1. | Introduction                          | 1         |

|----|---------------------------------------|-----------|

|    | 1.1.Motivation                        | 1         |

|    | 1.2. Problem Formulation              | 3         |

|    | 1.3. Contributions                    | 3         |

|    | 1.4. Thesis Overview                  | 5         |

| 2. | Design Flow for Embedded Systems      | 7         |

|    | 2.1.A Generic Design Flow             | 7         |

|    | 2.2. Contributions to the Design Flow | 10        |

| 3. | Related Work                          | 13        |

|    | 3.1.Modeling                          | 13        |

|    | 3.1.1. Finite State Machines          | 14        |

|    | 3.1.2. Dataflow Graphs                | 15        |

|    | 3.1.3. Communicating Processes        | 16        |

|    | 3.1.4. Discrete-Event                 | 17        |

|    | 3.1.5. Petri Nets                     | 17        |

|    | 3.2. Formal Verification              | 19        |

|    | 3.3.Our Approach                      | 20        |

|    | 3.3.1. Modeling                       | 20        |

|    | 3.3.2. Formal Verification            | 21        |

| 4. | The Design Representation             | <b>23</b> |

|    | 4.1.Basic Definitions                 | 23        |

|    | 4.2. Description of Functionality     | 26        |

|    | 4.3. Dynamic Behavior                           | 27  |

|----|-------------------------------------------------|-----|

|    | 4.4. Summary                                    | 29  |

| 5. | Notions of Equivalence and                      |     |

|    | Hierarchy for PRES+                             | 33  |

|    | 5.1. Notions of Equivalence                     | 33  |

|    | 5.2. Hierarchical PRES+ Model                   | 39  |

|    | 5.2.1. Hierarchical Modeling of a GMDF $\alpha$ | 46  |

| 6. | Formal Verification of Embedded Systems         | 49  |

|    | 6.1. Preliminaries                              | 50  |

|    | 6.1.1. Formal Methods                           | 50  |

|    | 6.1.2. Temporal Logics                          | 51  |

|    | 6.1.3. Timed Automata                           | 53  |

|    | 6.2. Verification of PRES+ Models               | 55  |

|    | 6.2.1. Our Approach to Formal Verification      | 56  |

|    | 6.2.2. Translating PRES+ into Timed Automata    | 58  |

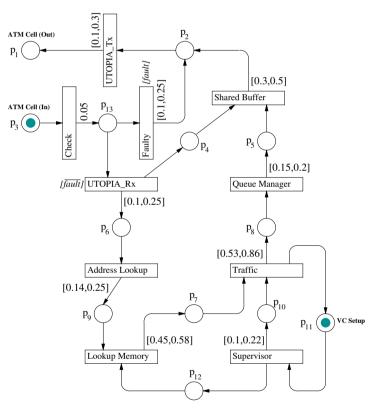

|    | 6.3. Verification of an ATM Server              | 63  |

| 7. | <b>Reduction of Verification Complexity</b>     |     |

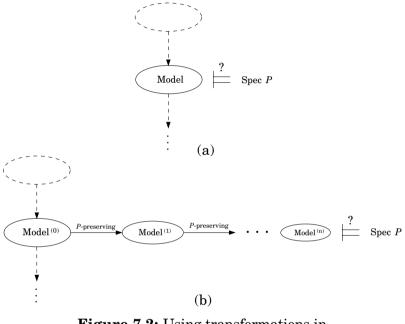

|    | by using Transformations                        | 67  |

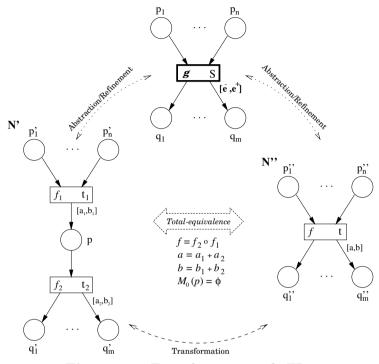

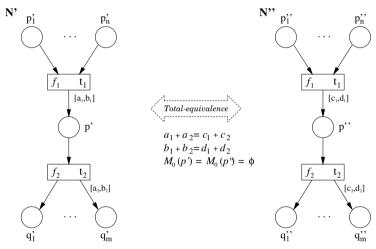

|    | 7.1. Transformations                            | 68  |

|    | 7.2. Verification of the GMDF $\alpha$          | 74  |

| 8. | <b>Reduction of Verification Time</b>           |     |

|    | by Clustering Transitions                       | 79  |

|    | 8.1. Clustering                                 | 80  |

|    | 8.2. Improved Translation Procedure             | 84  |

|    | 8.3. Revisiting the GMDF $\alpha$               | 88  |

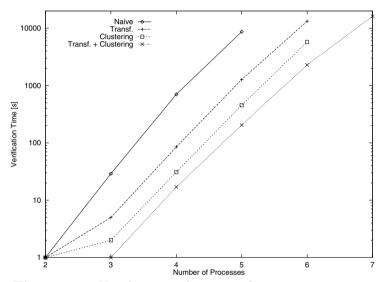

| 9. | Experimental Results                            | 91  |

|    | 9.1. Ring-Configuration Processes               | 91  |

|    | 9.2. Fischer's Mutual Exclusion Protocol        | 94  |

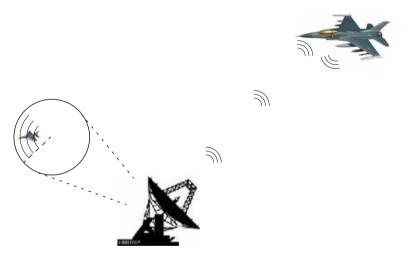

|    | 9.3. Radar Jammer                               | 96  |

| 10 | Conclusions and Future Work                     | 105 |

|    | 10.1.Conclusions                                | 105 |

|    | 10.2.Future Work                                | 107 |

|    | References                                      | 109 |

# Chapter 1 Introduction

THIS THESIS CONCENTRATES on aspects related to the modeling and formal verification of real-time embedded systems.

We propose a modeling formalism that can capture relevant characteristics of real-time embedded systems at different levels of granularity.

We also introduce an approach to the problem of formal verification of real-time embedded systems represented in our modeling formalism.

This introductory chapter presents the motivation behind our research activities, followed by the formulation of the problem we are dealing with. A summary of the main contributions of our work as well as an overview of the structure of the thesis are also presented.

## 1.1 Motivation

Embedded systems are becoming pervasive in our everyday life. These systems have many applications including automotive and aircraft controllers, cellular phones, network switches, household appliances, medical devices, and consumer electron-

#### CHAPTER 1

ics. The microprocessor market, for instance, clearly shows the situation: less than 1% of the microprocessors shipped all over the world in 1999 were used in general purpose computers [Tur99]. The rest of the share went to the embedded market.

Embedded systems are part of larger systems and typically interact continuously with their environment. Embedded systems generally include both software and hardware elements, that is, programmable processors and hardware components like application specific integrated circuits (ASICs) and field programmable gate arrays (FPGAs). Besides their heterogeneity, embedded systems are characterized by their dedicated function, real-time behavior, and high requirements on reliability and correctness [Cam96].

Designing systems with such characteristics is a difficult task. Moreover, the ever increasing complexity of embedded systems combined with small time-to-market windows poses interesting challenges for the designers.

An essential issue of any systematic methodology aiming at designing embedded systems is the underlying model of computation. The design process must be based on a model with precise mathematical meaning so that the different tasks from specification to implementation can be carried out systematically [Edw97]. A sound representation allows capturing unambiguously the functionality of the system, verifying its correctness with respect to certain desired properties, reasoning formally about the refinement and steps during the synthesis process, and using CAD tools in order to assist the designer [Sgr00]. Therefore, the use of a formal representation in embedded systems design is a must.

Correctness plays a key role in many embedded applications. As we become more dependent on computer systems, the cost of a failure can be extremely high, in terms of loss of both human lives and money. In safety-critical systems, for instance, reliability and safety are the most important criteria. Traditional validation techniques, like simulation and testing, are neither

#### INTRODUCTION

sufficient nor viable to verify the correctness of such systems. Formal verification is becoming a practical way to ensure the correctness of designs by complementing simulation and testing.

Formal methods are analytical and mathematical techniques intended to prove formally that the implementation of a system conforms its specification. Formal methods have extensively been used in software development [Gan94] as well as in hardware verification [Ker99]. However, formal verification techniques are not yet commonly used in embedded systems design.

## 1.2 Problem Formulation

The previous section has presented the motivation for our research and pointed out the relevance of the topics addressed in this thesis.

The model of computation is the backbone of a design flow. One of our goals is to define a formal representation capable of capturing important characteristics of real-time embedded systems, like timing and dedicated function. It must have a welldefined semantics so that the advantages of a sound modeling formalism can be exploited along the design process. It must be, at the same time, intuitive enough so that the designer can understand and handle it.

Since correctness is becoming increasingly important for embedded systems, we also aim at developing a framework for the verification of such systems by using formal methods. It must allow reasoning about design properties including timing requirements of systems.

## 1.3 Contributions

The main contributions of this thesis are as follows:

• Definition of a model of computation for real-time embedded systems design. PRES+, short for Petri Net based Represen-

### CHAPTER 1

tation for Embedded Systems, is an extension to the classical Petri nets model that captures explicitly timing information, allows systems to be represented at different levels of granularity, and improves expressiveness by allowing tokens to carry information. Furthermore, PRES+ supports the concept of hierarchy.

- An approach to the formal verification of real-time embedded systems. We present in this thesis an approach that allows reasoning formally about embedded systems represented in PRES+. Model checking is used to automatically determine whether the system model satisfies its required properties expressed in temporal logics. A systematic procedure to translate PRES+ models into timed automata is proposed so that it is possible to make use of existing model checking tools.

- Definition of notions of equivalence for systems represented in PRES+. Such notions establish a formal framework to compare PRES+ models, for instance, in a transformational approach. The concept of hierarchy for PRES+ models introduced in this thesis is closely related to these notions of equivalence.

- Strategies to improve the efficiency of verification. On one hand, correctness-preserving transformations are applied to the system model in order to obtain a simpler, yet semantically equivalent, one. Thus the verification effort can be reduced. On the other hand, by exploiting the structure of the system model and, in particular, extracting its sequential behavior, the translation of PRES+ into timed automata can be improved and, therefore, the complexity of the verification process can considerably be reduced.

Part of the work reported in this thesis has been presented in a number of publications [Cor99], [Cor00a], [Cor00b], [Cor00c], [Cor01b].

# 1.4 Thesis Overview

The rest of this thesis is structured as follows:

- Chapter 2 depicts a generic design flow for embedded systems and indicates those design steps that are mainly considered in this thesis.

- Chapter 3 addresses related work in the areas of modeling and formal verification.

- Chapter 4 presents the formal definition of the model of computation that we use to represent real-time embedded systems and describes its main features.

- Chapter 5 formally defines four notions of equivalence for systems represented in PRES+ and introduces the concept of hierarchical PRES+ model.

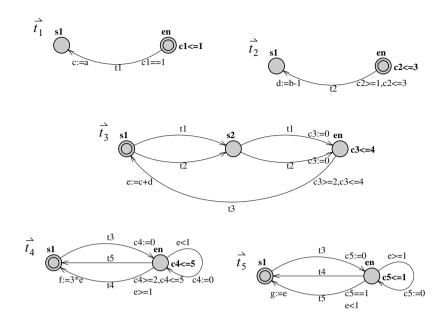

- Chapter 6 describes our approach to formal verification of embedded systems. It discusses how we make use of model checking to prove design properties with respect to a PRES+ model. A translation procedure from PRES+ into timed automata is also presented so that existing model checkers can be used in our approach.

- Chapter 7 introduces a transformational approach aimed at reducing the complexity of the verification process. A number of transformations to be used in order to simplify the system model are also presented.

- Chapter 8 discusses how further improvements of the verification approach can be achieved by exploiting the structure of the system model. An algorithm that extracts the sequential behavior of the system is proposed in this chapter.

- Chapter 9 demonstrates the feasibility of our approach on practical applications by studying different examples, includ-

ing a real-life system.

• Chapter 10 concludes this thesis and discusses possible directions in our future work.

# Chapter 2 Design Flow for Embedded Systems

THIS CHAPTER PRESENTS a generic design flow for embedded systems. We emphasize the parts of such a flow that are directly addressed in this thesis in order to show how our work contributes to the design of embedded systems.

## 2.1 A Generic Design Flow

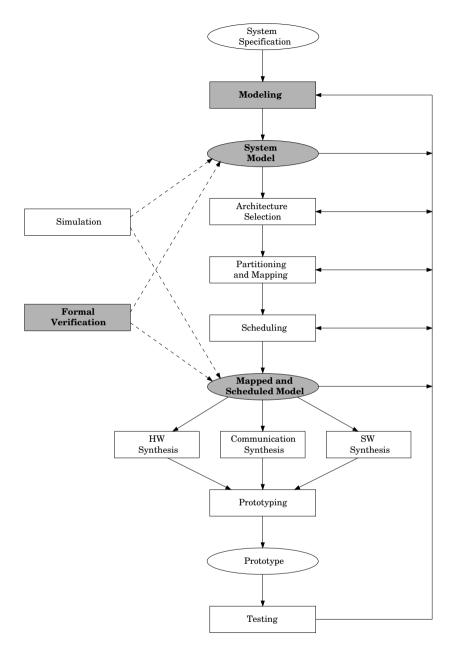

A generic design flow for embedded systems is shown in Figure 2.1. The process starts with a *system specification* which describes the functionality of the system as well as performance, cost, power, and other constraints of the intended design. Such a specification states the functionality without giving implementation details, that is, it specifies *what* the system must do without making assumptions about *how* it must be implemented.

The designer must come up with a *system model* that captures aspects from the functional part of the specification as well as non-functional attributes. Such a system model is usually presented at process or task level. The importance of a sound model

Figure 2.1: A generic design flow for embedded systems

of computation in the design flow becomes evident in the later phases.

Then, the designer must decide the underlying architecture of the system, that is, select the type and number of components as well as the way to interconnect them. This stage is known as *architecture selection*. The components may include processors, memories, and custom modules.

After the architecture selection phase comes *partitioning and mapping*, where the tasks or processes of the system model are grouped and mapped onto the selected components. Once it has been determined what parts are to be implemented on which components, certain decisions concerning the execution order of tasks or processes have to be taken. This design step is called *scheduling*.

At this point, the model must include the information about the decisions taken in the stages of architecture selection, partitioning, and scheduling (*mapped and scheduled model*). A formal representation allows systems to be refined incrementally so that new design decisions are included in the system model. This is possible because a model of computation with a welldefined semantics permits to formally reason about each refinement step during the design process.

The process further continues with *SW synthesis*, *HW synthesis*, and *communication synthesis*, and later with *prototyping*. The design flow includes iterations, where it is sometimes necessary to go back to previous steps because some of the design goals cannot be fulfilled.

Once the *prototype* has been produced, it must be thoroughly checked during the *testing* phase in order to find out whether it functions correctly.

Simulation can be used to validate the design at different stages of the process and, therefore, can be done at different levels of accuracy. *Formal verification* can also be performed at different points of the design flow, for example, on the initial system model or on the mapped and scheduled model.

## 2.2 Contributions to the Design Flow

Our work contributes to various steps of the flow presented above. The main contributions of this thesis are highlighted in Figure 2.1 as shaded boxes/ovals. The model of computation to be used in the design process is an important contribution of our research. As will be discussed in Chapter 4, PRES+ is a sound modeling formalism and supports a flow like the one presented above, in which the system model is refined to progressively include design decisions. Though we do not deal in this thesis with the problems of architecture selection, partitioning, and scheduling, our model is capable of capturing the design information resulted from these stages.

Formal verification requires a sound model. We propose an approach to formal verification of embedded systems represented in PRES+. This is another major contribution of our work to the design flow. In principle our verification approach can be applied to any level of abstraction, but in practice it is limited by the complexity of the system representation. Therefore, it is mainly useful at higher levels of abstraction.

Though we concentrate on the formal verification part of the validation/verification process, it is worth mentioning that we have developed a simulator for PRES+ models. Simulation is fundamental in the design flow and formal methods are not meant to replace it. Rather, simulation and formal verification must go hand in hand to successfully verify the correctness of designs.

Much of the research presented in this thesis has been performed within the frame of the SAVE project [SAV]. The SAVE project aims at the development of a formal approach to specification, implementation, and verification of heterogeneous electronic systems. The objective of the project is to devise improved solutions and methods for high level electronic system specification, verification, and refinement by use of formal methods. In the frame of SAVE, the design flow starts with a functional specification written in Haskell [Has]. The Haskell description employs higher-order functions, called *skeletons*, used to model elementary processes [San99]. Our research group has developed a tool which compiles Haskell descriptions based on skeletons into PRES+ models. The PRES+ model is then used as the basis for formal verification and as a design representation for the subsequent steps in the design process, as depicted in Figure 2.1. Though the SAVE design flow is a particular case of the flow described above, in which the functional specification is given in Haskell, it does illustrate that our model can indeed be used as a part of a realistic design flow for embedded systems.

# Chapter 3 Related Work

MODELING IS AN IMPORTANT ISSUE of any design methodology. Many models of computation have been proposed in the literature to represent digital systems. These models encompass a broad range of styles, characteristics, and application domains. Particularly in embedded systems design, a variety of models have been developed and used as system representation.

In the field of formal verification, many approaches have also been presented. There are a lot of theoretical results that have been put into practice. However, approaches targeted especially to embedded systems are not so common.

This chapter presents related work in the areas of modeling and verification of embedded systems.

## 3.1 Modeling

Many models have been proposed to represent embedded systems [Lav99], [Edw97], including extensions to finite state machines, data flow graphs, communicating processes, and Petri nets, among others. Some of them give a rigorous mathematical treatment to the formalism. This section presents various models of computation for embedded systems reported in the literature.

### 3.1.1 FINITE STATE MACHINES

The classical Finite State Machine (FSM) representation is probably the most well-known model used for describing control systems. One of the disadvantages of FSMs is the exponential growth of the number of states as the system complexity rises. A number of extensions to the classical FSM model have been suggested.

**Codesign Finite State Machines**. A Codesign Finite State Machine (CFSM) is an extended FSM including a control part and a data computation part [Chi93]. Each CFSM behaves synchronously from its own perspective. A system is composed of a number of CFSMs that communicate among themselves asynchronously through signals, which carry information in the form of events. Such a semantics provides a GALS model: Globally Asynchronous (at the system level) and Locally Synchronous (at the CFSM level). CFSMs are intended for control-oriented systems and are the underlying model of the POLIS design environment [Bal97].

**Finite State Machine with Datapath**. In order to make it more suitable for data-oriented systems, the FSM model has been extended by introducing a set of internal variables, thus leading to the concept of FSM with Datapath (FSMD) [Gaj94]. The transition relation depends not only on the present state and input signals but also on a set of internal variables. Though the introduction of variables in the FSMD model helps to reduce the number of states, the lack of explicit support for concurrency and hierarchy is a drawback because the state explosion problem is still present.

**FunState**. The FunState model consists of a network and a finite state machine [Str01]. The so-called network corresponds

to the data intensive part of the system. The network is composed of storage units, functions, and arcs that relate storage units and functions. Data is represented by valued tokens in the storage units. The activation of functions in the network is controlled by the state machine. In the FunState model, an arbitrary number of components (network and FSM) can be arranged in a hierarchical structure.

**Statecharts**. Statecharts extends FSMs by allowing hierarchical composition and concurrency [Har87]. A particular state can be composed of substates which means that being in the higherlevel state is interpreted as being in one of the substates. In this way, Statecharts avoids the potential for state explosion by permitting condensed representations. Furthermore, timing is specified by using linear inequalities in the form of time-outs. The problem with Statecharts is that the model falls short when representing data-oriented systems.

### 3.1.2 DATAFLOW GRAPHS

Dataflow graphs are quite popular in modeling data-dominated systems. Computationally intensive systems might be conveniently represented by a directed graph where the nodes describe computations and the arcs represent the order in which the computations are performed. The computations are executed only when the required operands are available and the operations behave as functions without side effects. However, the conventional dataflow graph model is inadequate for representing the control unit of systems.

**Dataflow Process Networks**. This model is mainly used in signal processing systems [Lee95]. Programs are specified by directed graphs where nodes (actors) represent computations and arcs (streams) represent sequences of data. Processing is done in series of iterated firings in which an actor transforms input data into output ones. Dataflow actors have firing rules to determine when they must be enabled and then execute a spe-

### CHAPTER 3

cific operation. The model also allows hierarchical representations of the graphs. A special case of dataflow process networks is Synchronous Data Flow (SDF) where the actors consume and produce a fixed number of data tokens in each firing because of their static rules.

**Conditional Process Graph**. A Conditional Process Graph (CPG) is a directed, acyclic, and polar graph, consisting of nodes, and simple and conditional edges [Ele98]. Each node represents a process which can be assigned to one of the processing elements. The graph has two special nodes (source and sink) used to represent the first and last task. The model allows each process to be characterized by an execution time and a guard which is the condition necessary to activate the tasks of that process. In this way, it is possible to capture control information in a dataflow graph.

### 3.1.3 COMMUNICATING PROCESSES

Several models have been derived from Hoare's Communicating Sequential Processes (CSP) [Hoa85]. In CSP, systems are composed of processes that communicate with each other through unidirectional channels using a synchronizing protocol.

**SOLAR**. SOLAR is based on CSP, where each process corresponds to an extended FSM, similar to Statecharts, and communication is performed by dedicated units [Jer95]. Thus communication is separated from the rest of the design so that it can be optimized and reused. By focusing on efficient implementation and refinement of the communication units, SOLAR is best suited for communication-driven design processes. SOLAR is the underlying model of the COSMOS design environment [Ism94].

**Interacting Processes**. This model consists of independent interacting sequential processes derived from CSP [Tho93]. The communication is performed through channels but, unlike CSP,

there exist additional primitives that permit unbuffered transfer and synchronization without data.

### 3.1.4 DISCRETE-EVENT

A Discrete-Event (DE) system can be defined as a discrete-state event-driven system. In other words, its state evolution depends entirely on the occurrence of asynchronous discrete events over time [Cas93]. An event is an instantaneous action that causes transitions from one discrete state to another. The interaction between computational tasks is accomplished by signals. In the discrete-event model, a signal is a set of atomic events that occur in some instant of physical time. Thus, each event has a value and is marked with a time stamp. The events are sorted by time label and they are analyzed in chronological order. Since time is an essential part of a discrete-event model, it could be used to represent real-time embedded systems. However, the principal disadvantage of discrete-event modeling is its cost: it is computationally expensive because it is necessary to globally sort all the events according to their time of occurrence.

## 3.1.5 Petri Nets

Modeling of systems using Petri Nets (PN) has been applied widely in many fields of science [Pet81], [Mur89]. The mathematical formalism developed over the years, which defines its structure and firing rules, has made Petri nets a well-understood and powerful model. A large body of theoretical results and practical tools have been developed around Petri nets. Several drawbacks, however, have been pointed out, especially when it comes to modeling embedded systems: a) Petri nets tend to become large even for relatively small systems. The lack of hierarchical composition makes it difficult to specify and understand complex systems using the conventional model; b) The classical PN model lacks the notion of time. However in many embedded applications time is a critical factor; c) Uninterpreted

#### CHAPTER 3

Petri nets lack expressiveness for formulating computations as long as tokens are considered as "black dots". Several formalisms have been proposed in different contexts in order to overcome the problems cited above [Dit95], [Mer76], [Jen91].

**Colored Petri Nets**. In Colored Petri Nets (CPN), tokens may have "colors", that is, data attached to them [Jen92]. The arcs between transitions/places have expressions that describe the behavior of the net. Thus transitions describe actions and tokens carry values. The CPN model permits hierarchical constructions and a strong mathematical theory has been built up around it. The problem of CPN is that timing is not explicitly defined in the model. It is possible to treat time as any other value attached to tokens but, since there is no semantics given for the order of firing along the time horizon, timing inconsistencies can happen.

**PURE**. Petri net based Unified REpresentation (PURE) is a model with data and control notation [Sto95]. It consists of two different, but closely related, parts: a control unit and a computational/data part. Timed Petri nets with restricted transition rules are used to represent the control flow. Hardware and software operations are represented by datapaths and instruction dependence graphs respectively. Hierarchy is not supported by this model.

**DTPN**. Dual Transitions Petri Nets (DTPN) is a model where control and data flow are tightly linked [Var01a]. There are two types of transitions (control and data transitions) as well as two types of arcs (control and data flow arcs). Tokens may have values which are affected by the firing of data transitions. Control transitions may have guards that depend on token values so that guards constitute the link between the control and data domains. The disadvantage of DTPN is that it lacks an explicit notion of time. Nor does it support hierarchical constructions.

Several other models extending Petri nets have been used in the design of embedded systems [Mac99], [Sgr99], [Ess98], [Ben92].

# 3.2 Formal Verification

Though formal methods are not commonplace in embedded systems design, several verification approaches have been proposed recently. Some of them are presented in this section. We focus on the more automatic approaches like model checking since these are closely related to our work. However, it is worth mentioning that theorem proving [Fit96], [Gal87] is a well-established approach in the area of formal methods, though not extensively used for the particular case of embedded systems.

Language Containment based on CFSMs. In this approach, CFSMs are translated into traditional state automata in order to make use of automata theory techniques [Bal96]. The verification task is to check whether all possible sequences of inputs and outputs of the system satisfy the desired properties (specification). The sequences that meet the requirements constitute the language of another automaton. The problem is then reduced to checking language containment between two automata. Verification requires showing that the language of the system automaton is contained in the language of the specification automaton. The drawback of the approach is that it is not possible to check explicit timing properties, only order of events.

**Model Checking based on Timed Automata**. Most of the research on continuous-time model checking is based on the timed automata model [Alu99]. Different algorithms have been proposed to verify systems represented as timed automata and tools, e.g. [Upp], [Kro], have successfully been developed and tested on realistic examples. However, timed automata is a fairly low-level representation.

Model Checking based on Hybrid Automata. This approach models the system as a collection of linear hybrid automata

### CHAPTER 3

[Hsi99]. Arguing different times scales for the hardware and software parts of the system, clocks with different rates are used to keep track of the time. While the linear hybrid automata model is more expressive than timed automata, the problem of model checking of hybrid automata is harder than the one based on timed automata. The approach deals with timing properties although the method is only feasible for low complexity systems.

**Model Checking based on FunState**. Properties of a Fun-State model can be formally verified by using model checking [Str01]. The proposed verification strategy is based on an auxiliary representation, very much alike a FSM, into which the Fun-State model is transformed. The set of required properties are expressed as Computation Tree Logic (CTL) formulas. However, no quantitative timing behavior can be reasoned based on CTL.

**Model Checking based on DTPN**. This approach uses DTPN as underlying model of computation [Var01b]. The DTPN model is transformed in a Kripke structure and then BDD-based symbolic model checking is used to determine the truth of Linear Temporal Logic (LTL) and CTL formulas. Since there is no explicit notion of time in DTPN, timing requirements can not be verified.

# 3.3 Our Approach

In this section we highlight several points that make our approach different in relation to work reported in the literature.

## 3.3.1 MODELING

The following are aspects of our work that differ from other modeling formalisms in the area:

- Our model includes an explicit notion of time.

- Our model supports hierarchical composition.

- We can capture both data and control aspects of the system.

Several models address separately the points mentioned above. They key difference is that our modeling formalism combines such aspects.

## 3.3.2 FORMAL VERIFICATION

Aspects of our approach that differ from the related work presented in Section 3.2 are:

- We deal with quantitative timing properties in our verification approach.

- The underlying model of computation allows representations at different levels of granularity so that formal verification is possible at several abstraction levels.

# Chapter 4 The Design Representation

IN ORDER TO DEVISE EMBEDDED SYSTEMS the design process must be based upon a sound model of computation that captures important features of such systems. The notation we use to model real-time embedded systems is an extension to Petri nets, called PRES+ (Petri Net based Representation for Embedded Systems). This chapter presents the formal definition of PRES+.

## 4.1 Basic Definitions

**Definition 4.1.** A *PRES*+ model is a five-tuple  $N=(P, T, I, O, M_0)$  where

$P = \{p_1, p_2, ..., p_m\}$  is a finite non-empty set of *places*;

$T = \{t_1, t_2, ..., t_n\}$  is a finite non-empty set of *transitions*;

$I \subseteq P \times T$  is a finite non-empty set of *input arcs* which define the flow relation between places and transitions;

$O \subseteq T \times P$  is a finite non-empty set of *output arcs* which define the flow relation between transitions and places;

$M_0$  is the initial *marking* of the net (see Definition 4.4).

#### Chapter 4

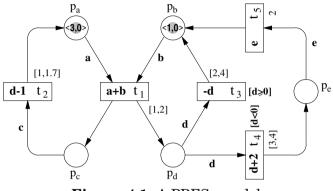

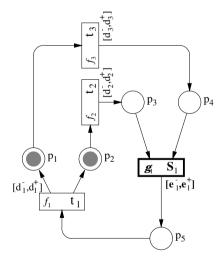

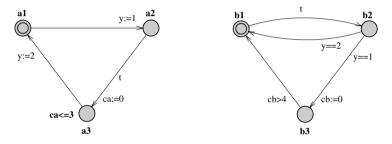

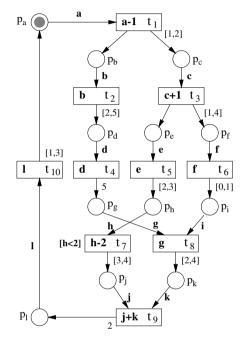

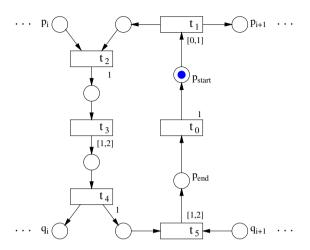

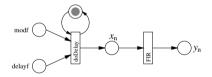

We use the example of Figure 4.1 in order to illustrate the definitions of the model presented in this chapter. Like in classical Petri nets, places are graphically represented by circles, transitions by boxes, and arcs by arrows. For this example,  $P=\{p_a, p_b, p_c, p_d, p_e\}$  and  $T=\{t_1, t_2, t_3, t_4, t_5\}$ .

Figure 4.1: A PRES+ model

**Definition 4.2**. A *token* is a pair  $k = \langle v, r \rangle$  where

*v* is the *token value*. The type of this value is referred to as *token type*;

*r* is the *token time*, a non-negative real number representing the time stamp of the token.

The set *K* denotes the set of all possible token types for a given system.  $\blacksquare$

A token value may be of any type, e.g. boolean, integer, etc., or user-defined type of any complexity (for instance a structure, a set, or a record). A token type is defined by the set of possible values that the token may take. Thus K is a set of sets.

For the initial marking of the net shown in Figure 4.1, for instance, in place  $p_a$  there is a token  $k_a$  with token value  $v_a=3$  and token time  $r_a=0$ .

**Definition 4.3.** The *type function*  $\tau : P \to K$  associates every place  $p \in P$  with a token type.  $\tau(p)$  denotes the set of possible

values that tokens may bear in *p*. The set of possible tokens in place *p* is given by  $E_p = \{ \langle v, r \rangle | v \in \tau(p) \land r \in \mathbb{R}^+_0 \}$ .  $E = \bigcup_{p \in P} E_p$  denotes the set of all tokens.

It is worth pointing out that the token type related to a certain place is fixed, that is, it is an intrinsic property of that place and will not change during the dynamic behavior of the net. For the example given in Figure 4.1,  $\tau(p)=\mathbb{Z}$  for all  $p \in P$ , i.e. all places have token type *integer*. Thus the set of all possible tokens in the system is  $E = \{ \langle v, r \rangle | v \in \mathbb{Z} \land r \in \mathbb{R}_0^+ \}$ .

**Definition 4.4.** A marking M is an assignment of tokens to places of the net. The marking of a place  $p \in P$ , denoted M(p), can be represented as a multi-set<sup>1</sup> over  $E_p$ . For a particular marking M, a place p is said to be marked iff  $M(p) \neq \emptyset$ .

The initial marking  $M_0$  in the net of Figure 4.1 shows  $p_a$  and  $p_b$  as the only places initially marked:  $M_0(p_a) = \{\langle 3, 0 \rangle\}$  and  $M_0(p_b) = \{\langle 1, 0 \rangle\}$ , whereas  $M_0(p_c) = M_0(p_d) = M_0(p_e) = \emptyset$ .

**Definition 4.5.** The *pre-set*  $\circ t = \{p \in P | (p, t) \in I\}$  of a transition  $t \in T$  is the set of *input places* of *t*. Similarly, the *post-set*  $t^\circ = \{p \in P | (t, p) \in O\}$  of a transition  $t \in T$  is the set of *output places* of *t*. The *pre-set*  $\circ p$  and the *post-set*  $p^\circ$  of a place  $p \in P$  are given by  $\circ p = \{t \in T | (t, p) \in O\}$  and  $p^\circ = \{t \in T | (p, t) \in I\}$  respectively.

**Definition 4.6**. All output places of a given transition have the same token type, that is,  $p, q \in t^{\circ} \Rightarrow \tau(p) = \tau(q)$

This definition is motivated by the fact that there is one transition function associated to a transition (as formally stated in Definition 4.7), so that when it fires all its output places get tokens with the same value and therefore such places must have the very same token type.

<sup>1.</sup> A *multi-set* or *bag* is a collection of elements over some domain in which, unlike a set, multiple occurrences of the same element are allowed. For example,  $\{a, b, b, b\}$  is a multi-set over  $\{a, b, c\}$ .

## 4.2 Description of Functionality

**Definition 4.7.** For every transition  $t \in T$ , there exists a *transition function f* associated to *t*. Formally, for all  $t \in T$  there exists  $f : \tau(p_1) \times \tau(p_2) \times \ldots \times \tau(p_a) \rightarrow \tau(q)$  where  ${}^{\circ}t = \{p_1, p_2, \ldots, p_a\}$  and  $q \in t^{\circ}$ .

Transition functions are very important when describing the functionality of the system to be modeled. They allow systems to be modeled at different levels of granularity with transitions representing simple arithmetic operations or complex algorithms. In Figure 4.1 we inscribe transition functions inside transition boxes: the transition function associated to  $t_1$ , for example, is given by  $f_1(a, b)=a+b$ . We use inscriptions on the input arcs of a transition in order to denote the arguments of its transition function.

**Definition 4.8.** For every transition  $t \in T$ , there exist a *minimum transition delay*  $d^-$  and a *maximum transition delay*  $d^+$ , which are non-negative real numbers and represent, respectively, the lower and upper limits for the execution time (delay) of the function associated to the transition. Formally, for all  $t \in T$  there exist  $d^-$ ,  $d^+ \in \mathbb{R}^+_0$  such that  $d^- \leq d^+$ .

Referring again to Figure 4.1, the minimum transition delay of  $t_2$  is  $d_2^{-}=1$ , and its maximum transition delay is  $d_2^{+}=1.7$  time units. Note that when  $d^{-}=d^{+}=d$ , we just inscribe the value d close to the respective transition, like in the case of the transition delay  $d_5=2$ .

**Definition 4.9.** A transition  $t \in T$  may have a *guard* G associated to it. The guard of a transition t is a predicate  $G: \tau(p_1) \times \tau(p_2) \times \ldots \times \tau(p_a) \rightarrow \{0, 1\}$  where  ${}^{\circ}t=\{p_1, p_2, \ldots, p_a\}$ .

Note that the guard of a transition t is a function of the token values in places of its pre-set  $\circ t$ . For instance, in Figure 4.1, d < 0 represents the guard  $G_4$ .

# 4.3 Dynamic Behavior

**Definition 4.10**. A transition  $t \in T$  is *bound*, for a given marking M, iff all its input places are marked. A *binding* b of a bound transition t, with pre-set  ${}^{\circ}t=\{p_1, p_2, ..., p_a\}$ , is an ordered tuple of tokens  $b=(k_1, k_2, ..., k_a)$  where  $k_i \in M(p_i)$  for all  $p_i \in {}^{\circ}t$ .

Observe that, for a particular marking M, a transition may have different bindings. This is the case when there are several tokens in at least one of the input places of the transition. The existence of a binding is a necessary condition for the enabling of a transition. For the initial marking of the net shown in Figure 4.1,  $t_1$  has a binding  $b=(\langle 3, 0 \rangle, \langle 1, 0 \rangle)$ . Since  $t_1$  has no guard, it is enabled for the initial marking (as formally stated in Definition 4.11).

We introduce the following notation which will be useful for the coming definitions. Given the binding  $b=(k_1, k_2, ..., k_a)$ , the token value of the token  $k_i$  is denoted  $v_i$ , and the token time of  $k_i$  is denoted  $r_i$ .

**Definition 4.11.** A bound transition  $t \in T$  with guard G is *enabled*, for a binding  $b=(k_1, k_2, ..., k_a)$ , iff  $G(v_1, v_2, ..., v_a)=1$ . A transition  $t \in T$  with no guard is *enabled* if t is bound.

**Definition 4.12**. The *enabling time et* of an enabled transition  $t \in T$ , for a binding  $b=(k_1, k_2, ..., k_a)$ , is the time instant at which *t* becomes enabled. *et* is given by the maximum token time of the tokens in the binding *b*, that is,  $et=max(r_1, r_2, ..., r_a)$ .

**Definition 4.13.** The *earliest trigger time*  $tt^{-}=et + d^{-}$  and the *lat*est trigger time  $tt^{+}=et + d^{+}$  of an enabled transition  $t \in T$ , for a binding  $b=(k_1, k_2, ..., k_a)$ , are the lower and upper time limits for the firing of t. An enabled transition  $t \in T$  may not fire before its earliest trigger time  $tt^{-}$  and must fire before or at its latest trigger time  $tt^{+}$ , unless t becomes disabled by the firing of another transition. •

#### Chapter 4

**Definition 4.14**. The *firing* of an enabled transition  $t \in T$ , for a binding  $b=(k_1, k_2, ..., k_a)$ , changes a marking M into a new marking  $M^+$ . As a result of firing the transition t, the following occurs:

(i) Tokens from its pre-set  $\circ t$  are removed, that is,  $M^+(p_i)=M(p_i)-\{k_i\}$  for all  $p_i \in \circ t$ ;

(ii) One new token  $k = \langle v, r \rangle$  is added to each place of its post-set  $t^{\circ}$ , that is,  $M^{+}(p) = M(p) + \{k\}^{2}$  for all  $p \in t^{\circ}$ . The token value of k is calculated by evaluating the transition function f with token values of tokens in the binding b as arguments, that is,  $v = f(v_1, v_2, ..., v_a)$ . The token time of k is the instant at which the transition t fires, that is,  $r = tt^*$  where  $tt^* \in [tt^-, tt^+]$ ;

(iii) The marking of places different from input and output places of *t* remain unchanged, that is,  $M^+(p)=M(p)$  for all  $p \in P - {}^{\circ}t - t^{\circ}$ .

The execution time of the function associated to a transition is considered in the time stamp of the new tokens. Note that, when a transition fires, all the tokens in its output places get the same token value and token time. The token time of a token represents the instant at which it was "created". If there is a situation in which there are several tokens with the same time stamp in an input place of a transition, the token to be removed when the transition fires is selected arbitrarily.

In Figure 4.1, transition  $t_1$  is the only one initially enabled (binding  $(\langle 3, 0 \rangle, \langle 1, 0 \rangle)$ ) so that its enabling time is 0. Therefore,  $t_1$  may not fire before 1 time units and must fire before or at 2 time units. Let us assume that  $t_1$  fires at 1 time units: tokens  $\langle 3, 0 \rangle$  and  $\langle 1, 0 \rangle$  are removed from  $p_a$  and  $p_b$  respectively, and a new token  $\langle 4, 1 \rangle$  is added to both  $p_c$  and  $p_d$ . At this moment, only  $t_2$  and  $t_3$  are enabled ( $t_4$  is bound but not enabled because its guard is not satisfied for the binding ( $\langle 4, 1 \rangle$ ). Note that tran-

<sup>2.</sup> Observe that the multi-set sum + is different from the multi-set union  $\cup$ . For instance, given  $A = \{a, c, c\}$  and  $B = \{c\}$ ,  $A + B = \{a, c, c, c\}$  while  $A \cup B = \{a, c, c\}$ . An example of multi-set difference – is  $A - B = \{a, c\}$ .

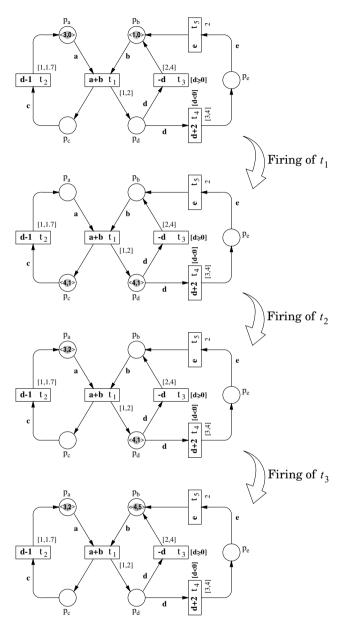

sition  $t_2$  has to fire strictly before  $t_3$ : according to the firing rules,  $t_2$  must fire no earlier than 2 and no later than 2.7 time units, while  $t_3$  is restricted to fire in the interval [3, 5]. Figure 4.2 illustrates a possible behavior of the PRES+ model.

# 4.4 Summary

To sum up, when used to model embedded systems, PRES+ has several interesting features to be highlighted, some of them inherited from the classical Petri net model:

- PRES+ allows representations at different levels of granularity.

- Since tokens carry information in our model, PRES+ overcomes the lack of expressiveness of classical Petri nets, where tokens are considered as "black dots".

- Time is a critical factor in many embedded applications. Our model captures timing aspects by associating lower and upper limits to the duration of activities related to transitions and keeping time information in token stamps.

- Non-determinism may be naturally represented by PRES+. Non-determinism can be used as a powerful mechanism to express succinctly the behavior of certain systems and thus reduce the complexity of the model.

- Sequential as well as concurrent activities may be easily expressed in terms of Petri nets. Recall that concurrency is present in most embedded systems.

- Both control and data information might be captured by a unified design representation.

- PRES+ has been also extended by introducing the concept of hierarchy (see Chapter 5).

- Furthermore, the model is simple, intuitive, and can be easily handled by the designer.

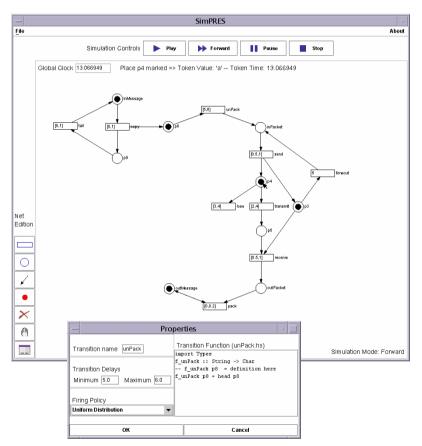

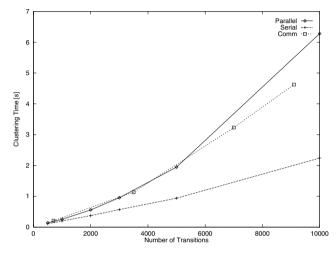

We have developed a software tool, called SimPRES, that allows PRES+ models to be simulated. It has a graphical interChapter 4

Figure 4.2: Illustration of the dynamic behavior of a PRES+ model

face that lets the designer construct, modify, and simulate systems represented in PRES+. A screen shot of the SimPRES tool is shown in Figure 4.3. Such a tool is of great help for the designer because it allows visualizing the model of the system under design and running it, so that an animation of the dynamic behavior of the net is possible. SimPRES supports full graphical editing of the model of the system and provides methods to store/recover the net in/from a file.

Figure 4.3: SimPRES: a simulator for PRES+ models

# Chapter 5 Notions of Equivalence and Hierarchy for PRES+

SEVERAL NOTIONS OF EQUIVALENCE for embedded systems represented in PRES+ are defined in this chapter. Such notions constitute the foundations of a framework to compare PRES+ models.

In this chapter we also extend PRES+ by introducing the concept of hierarchy. Hierarchy is a convenient way to structure the system so modeling can be done in a comprehensible form. Without hierarchical composition it is difficult to specify and understand large systems.

## 5.1 Notions of Equivalence

The synthesis process requires a number of refinement steps starting from the initial system model until a more detailed representation is achieved. Such steps correspond to transformations in the system model so that design decisions are included in the representation.

The validity of a transformation depends on the concept of

equivalence in which it is contrived. When we claim that two systems are equivalent, it is very important to understand the meaning of equivalence. Two equivalent systems are not necessarily the same but have properties that are common to both of them. Thus a clear notion of equivalence allows comparing systems and pointing out the properties in terms of which the systems are equivalent.

The following three definitions introduce basic concepts to be used when defining the four notions of equivalence for systems modeled in PRES+.

**Definition 5.1.** A marking  $M^+$  is *immediately reachable* from M if there exists a transition  $t \in T$  whose firing changes M into  $M^+$ .

**Definition 5.2**. The *reachability set* R(N) of a net N is the set of all markings reachable from  $M_0$  and is defined by:

(i)  $M_0 \in R(N)$ ;

(ii) If  $M \in R(N)$  and  $M^+$  is immediately reachable from M, then  $M^+ \in R(N)$ .

**Definition 5.3.** A place  $p \in P$  is said to be an *in-port* iff  $(t, p) \notin O$  for all  $t \in T$ , that is, there is no transition *t* for which *p* is output place. Similarly, a place  $p \in P$  is said to be an *outport* iff  $(p, t) \notin I$  for all  $t \in T$ , that is, there is no transition *t* for which *p* is input place.

The set of in-ports is denoted inP while the set of out-ports is denoted outP.

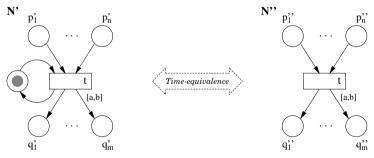

Before formally presenting the notions of equivalence, we first give an intuitive idea of them. Such notions rely on the concepts of in-ports and out-ports: the initial condition to establish an equivalence relation between two nets  $N_1$  and  $N_2$  is that both have the same number of in-ports as well as out-ports. In this way, it is possible to define a one-to-one correspondence between in-ports and out-ports of the nets. Thus we can assume the same initial marking in corresponding in-ports and then check the tokens obtained in the out-ports after some transition firings in the nets. It is like an external observer putting in the same data in both nets and obtaining output information. If such an external observer can not distinguish between  $N_1$  and  $N_2$ , based on the output data he gets, then  $N_1$  and  $N_2$  are "equivalent". As defined later, such a concept is called *total-equivalence*. We also define weaker concepts of equivalence in which the external observer may actually distinguish between  $N_1$  and  $N_2$ , but still there is some commonality in the data obtained in corresponding out-ports, namely number of tokens, token values, or token times.

We introduce the following notation to be used in the coming definitions: for a given marking M, m(p) denotes the number of tokens in place p, i.e. m(p)=|M(p)|.

**Definition 5.4**. Two nets  $N_1$  and  $N_2$  are *cardinality-equivalent* or *N*-equivalent iff:

(i) There exist such bijections  $f_{in}: inP_1 \rightarrow inP_2$  and  $f_{out}: outP_1 \rightarrow outP_2$  that define one-to-one correspondences between in(out)-ports of  $N_1$  and  $N_2$ ;

(ii) The initial markings  $M_{1,0}$  and  $M_{2,0}$  satisfy  $M_{1,0}(p)=M_{2,0}(f_{in}(p)) \neq \emptyset$  for all  $p \in inP_1$ ,  $M_{1,0}(q)=M_{2,0}(f_{out}(q))=\emptyset$  for all  $q \in outP_1$ ; (iii) For every  $M_1 \in R(N_1)$  such that  $m_1(p)=0$  for all  $p \in inP_1$ ,  $m_1(s)=m_{1,0}(s)$  for all  $s \in P_1 - inP_1 - outP_1$ there exists  $M_2 \in R(N_2)$  such that  $m_2(p)=0$  for all  $p \in inP_2$ ,  $m_2(s)=m_{2,0}(s)$  for all  $s \in P_2 - inP_2 - outP_2$ ,  $m_2(f_{out}(q))=m_1(q)$  for all  $q \in outP_1$ and vice versa.

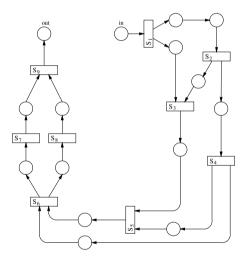

The above definition expresses that if the same tokens are put in corresponding places of two N-equivalent nets, then the same number of tokens will be obtained in corresponding out-ports. Let us consider the nets  $N_1$  and  $N_2$  shown in Figures 5.1(a) and

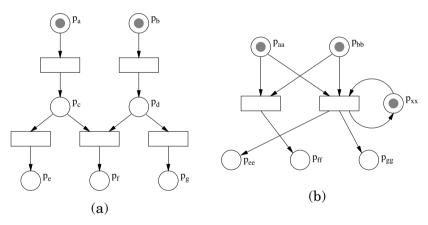

5.1(b) respectively, in which we have abstracted away information not relevant for the current discussion like transition delays and token values. For such nets  $inP_1 = \{p_a, p_b\}$ ,  $outP_1 = \{p_e, p_f, p_g\}$ ,  $inP_2 = \{p_{aa}, p_{bb}\}$ ,  $outP_2 = \{p_{ee}, p_{ff}, p_{gg}\}$ , and  $f_{in}$  and  $f_{out}$  are defined by  $f_{in}(p_a) = p_{aa}$ ,  $f_{in}(p_b) = p_{bb}$ ,  $f_{out}(p_e) = p_{ee}$ ,  $f_{out}(p_f) = p_{ff}$ , and  $f_{out}(p_g) = p_{gg}$ . Let us assume that  $M_{1,0}$  and  $M_{2,0}$  satisfy condition (ii) in Definition 5.4. A simple reachability analysis shows that there exist two cases  $m_1^i$  and  $m_1^{ii}$  in which the first part of condition (iii) in Definition 5.4. is satisfied: a)  $m_1^i(p)=1$  if  $p \in \{p_f\}$ , and  $m_1^i(p)=0$  for all other places; b)  $m_1^{ii}(p)=1$  if  $p \in \{p_e, p_g\}$ , and  $m_1^{ii}(p)=0$  for all other places. For each of these cases there exist a marking satisfying the second part of condition (iii) in Definition 5.4, respectively: a)  $m_2^i(p)=1$  if  $p \in \{p_{ff}, p_{xx}\}$ , and  $m_2^i(p)=0$  for all other places; b)  $m_2^{ii}(p)=1$  if  $p \in \{p_{ee}, p_{gg}, p_{xx}\}$ , and  $m_2^{ii}(p)=0$  for all other places. Hence  $N_1$  and  $N_2$  are N-equivalent.

Figure 5.1: N-equivalent nets

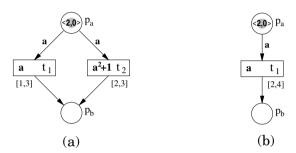

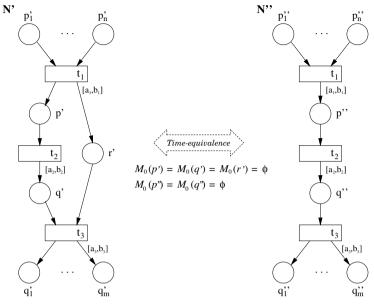

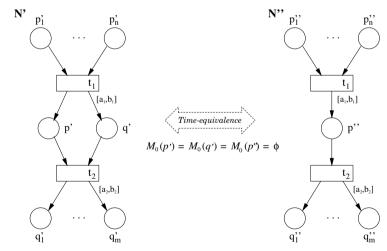

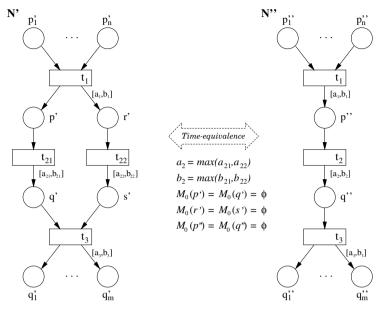

Before defining the concepts of *function-equivalence* and *time-equivalence*, let us study the simple nets  $N_1$  and  $N_2$  shown in Figures 5.2(a) and 5.2(b) respectively. It is straightforward to see that  $N_1$  and  $N_2$  fulfill the conditions established in Definition

5.4 and therefore are N-equivalent. However, note that  $N_1$  may produce tokens with different values in its output: when  $t_1$  fires, the token in  $p_b$  will be  $k_b = \langle 2, r_b^i \rangle$  with  $r_b^i \in [1,3]$ , but when  $t_2$ fires the token in  $p_b$  will be  $k_b = \langle 5, r_b^{ii} \rangle$  with  $r_b^{ii} \in [2,3]$ . The reason for this behavior is the non-determinism of  $N_1$ . On the other hand, when the only out-port of  $N_2$  is marked, the corresponding token value will always be  $v_b=2$ .

Figure 5.2: N-equivalent nets with different behavior

As shown in the example of Figure 5.2, even if two nets are Nequivalent the tokens in their outputs may be different, although their initial marking is identical. For instance, there is no marking  $M_2 \in R(N_2)$  in which the out-port has a token with value  $v_b=5$ , whereas it does exist a marking  $M_1 \in R(N_1)$  in which the out-port is marked and  $v_b=5$ . Thus the external observer could distinguish between  $N_1$  and  $N_2$  because of different token values—moreover different token times—in their outports when marked.

**Definition 5.5.** Two nets  $N_1$  and  $N_2$  are function-equivalent or *F*-equivalent iff:

(i)  $N_1$  and  $N_2$  are N-equivalent;

(ii) Let  $M_1$  and  $M_2$  be markings satisfying condition (iii) in Definition 5.4. For every  $\langle v_1, r_1 \rangle \in M_1(q)$ , where  $q \in outP_1$ , there exists  $\langle v_2, r_2 \rangle \in M_2(f_{out}(q))$  such that  $v_1 = v_2$ , and vice versa.

**Definition 5.6.** Two nets  $N_1$  and  $N_2$  are *time-equivalent* or *T*-

equivalent iff:

(i)  $N_1$  and  $N_2$  are N-equivalent;

(ii) Let  $M_1$  and  $M_2$  be markings satisfying condition (iii) in Definition 5.4. For every  $\langle v_1, r_1 \rangle \in M_1(q)$ , where  $q \in outP_1$ , there exists  $\langle v_2, r_2 \rangle \in M_2(f_{out}(q))$  such that  $r_1=r_2$ , and vice versa.

Two nets are F-equivalent if, besides being N-equivalent, the tokens obtained in corresponding out-ports have the same token value. Similarly, if tokens obtained in corresponding out-ports have the same token time, the nets are T-equivalent.

**Definition 5.7**. Two nets  $N_1$  and  $N_2$  are *total-equivalent* or *§*-equivalent iff:

(i)  $N_1$  and  $N_2$  are F-equivalent;

(ii)  $N_1$  and  $N_2$  are T-equivalent.

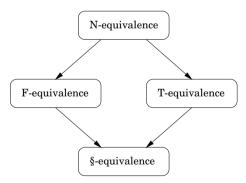

Figure 5.3 shows the relation between the different concepts of equivalence introduced above. The graph captures the dependence between the notions of equivalence. Thus, for instance, Nequivalence is necessary for T-equivalence and also for F-equivalence. Similarly, §-equivalence implies all other equivalences. §-equivalence is the strongest notion of equivalence defined in this work. Note that two §-equivalent nets must not necessarily be identical (see Figure 5.4).

Figure 5.3: Relation between the notions of equivalence

Figure 5.4: §-equivalent nets

# 5.2 Hierarchical PRES+ Model

Embedded systems require sound models along their design cycle. PRES+ supports systems modeled at different levels of granularity with transitions representing simple arithmetic operations or complex algorithms. However, in order to handle efficiently the modeling of large systems, a mechanism of hierarchical composition is needed so that the model may be constructed in a structured manner, composing simple units fully understandable by the designer. Hierarchy can conveniently be used as a form to handle complexity and also to analyze systems at different abstraction levels.

Hierarchical modeling can be applied along the design process of embedded systems. Sometimes the specification or requirements may not be complete or thoroughly understood. In a topdown approach, a designer may define the interface to each component and then gradually refine those components. On the other hand, a system may be constructed reusing existing elements such as IP blocks in a bottom-up approach. A hierarchical

PRES+ model can be devised bottom-up, top-down, or by mixing both approaches.

A flat representation of a real-life embedded system can be too big and complex to handle and understand. The concept of hierarchy allows systems to be modeled in a structured way. Thus the system may be broken down into a set of comprehensible nets structured in a hierarchy. Each one of these nets may represent a sub-block of the current design. Such a sub-block can be a pre-designed IP component as well as a design alternative corresponding to a subsystem of the system under design.

In this section we formalize the concept of hierarchy for PRES+ models. Some trivial examples are used in order to illustrate the definitions.

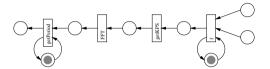

**Definition 5.8.** A transition  $t \in T$  is an *in-transition* of  $N = (P, T, I, O, M_0)$  iff  $\bigcup_{p \in inP} p^\circ = \{t\}$ . In a similar manner, a transition  $t \in T$  is an *out-transition* of N iff  $\bigcup_{p \in outP} \circ p = \{t\}$ .

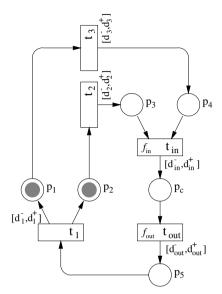

Note that the existence of non-empty sets *inP* and *outP* is a necessary condition for the existence of in- and out-transitions. For the net  $N_1$  shown in Figure 5.5,  $inP_1 = \{p_a, p_b\}$ ,  $outP_1 = \{p_d\}$ , and  $t_{in}$  and  $t_{out}$  are in-transition and out-transition respectively.

**Figure 5.5:** A simple subnet  $N_1$

**Definition 5.9.** An *abstract PRES*+ model is a six-tuple  $H=(P, T, \Lambda, I, O, M_0)$  where  $P=\{p_1, p_2, ..., p_m\}$  is a finite non-empty set of places;  $T=\{t_1, t_2, ..., t_n\}$  is a finite set of transitions;  $\Lambda=\{S_1, S_2, ..., S_l\}$  is a finite set of *super-transitions*;  $I \subseteq P \times (\Lambda \cup T)$  is a finite set of input arcs;  $O \subseteq (\Lambda \cup T) \times P$  is a finite set of output arcs;  $M_0$  is the initial marking.

Observe that a (non-abstract) PRES+ net is a particular case of an abstract PRES+ net with  $\Lambda=\emptyset$ . Figure 5.6 illustrates an abstract PRES+ net. Super-transitions are represented by thick-line boxes.

**Definition 5.10**. The *pre-set*  $^{\circ}S$  and *post-set*  $S^{\circ}$  of a super-transition  $S \in \Lambda$  are given by  $^{\circ}S = \{p \in P | (p, S) \in I\}$  and  $S^{\circ} = \{p \in P | (S, p) \in O\}$  respectively.

Similar to transitions, the pre(post)-set of a super-transition  $S \in \Lambda$  is the set of input(output) places of S.

Figure 5.6: An abstract PRES+ model

**Definition 5.11.** For every super-transition  $S \in \Lambda$  there exists a *high-level function*  $g: \tau(p_1) \times \tau(p_2) \times ... \times \tau(p_a) \rightarrow \tau(q)$  associated to S, where  ${}^{\circ}S = \{p_1, p_2, ..., p_a\}$  and  $q \in S^{\circ}$ .

Recall that  $\tau(p)$  denotes the *type* associated with the place  $p \in P$ , i.e. the type of value that a token may bear in that place. Observe the usefulness of high-level functions associated to super-transitions in, for instance, a top-down approach: for a certain component of the system, the designer may define its interface and a high-level description of its functionality through a super-transition, and in a later design phase refine the component. In current design methodologies it is also very common to reuse predefined elements such as IP blocks. In such cases, the internal structure of the component is unknown to the designer and therefore the block is best modeled by a super-transition and its high-level function.

**Definition 5.12.** For every super-transition  $S \in \Lambda$  there exist a *minimum estimated delay*  $e^{-}$  and a *maximum estimated delay*  $e^{+}$ , where  $e^{-} \leq e^{+}$  are non-negative real numbers that represent the estimated lower and upper limits for the execution time of the high-level function associated to S.

**Definition 5.13**. A super-transition may not be in *conflict* with other transitions or super-transitions, that is:

(i)  ${}^{\circ}S_1 \cap {}^{\circ}S_2 = \emptyset$  and  $S_1^{\circ} \cap S_2^{\circ} = \emptyset$  for all  $S_1, S_2 \in \Lambda$  such that  $S_1 \neq S_2$ ;

(ii)  $^{\circ}S \cap ^{\circ}t = \emptyset$  and  $S^{\circ} \cap t^{\circ} = \emptyset$  for all  $S \in \Lambda$ ,  $t \in T$ .

In other words, a super-transition may not "share" input places with other transitions/super-transitions, nor output places. In what follows, the input and output places of a supertransition will be called *surrounding* places.

**Definition 5.14.** A super-transition  $S_i \in \Lambda$  together with its surrounding places in the net  $H=(P, T, \Lambda, I, O, M_0)$  is a *semi-abstraction* of the subnet  $N_i=(P_i, T_i, \Lambda_i, I_i, O_i, M_{i,0})$  (or conversely,  $N_i$  is a *semi-refinement* of  $S_i$  and its surrounding

places) iff:

(i) There exists a unique in-transition  $t_{in} \in T_i$ ;

(ii) There exists a unique out-transition  $t_{out} \in T_i$ ;

(iii) There exists a bijection  $h_{in}$ :  ${}^{\circ}S_i \rightarrow inP_i$  that maps the input places of  $S_i$  onto the in-ports of  $N_i$ ;

(iv) There exists a bijection  $h_{out}: S_i^o \rightarrow outP_i$  that maps the output places of  $S_i$  onto the out-ports of  $N_i$ ;

(v)  $M_0(p) = M_{i,0}(h_{in}(p))$  and  $\tau(p) = \tau(h_{in}(p))$  for all  $p \in {}^\circ S_i$ ;

(vi)  $M_0(p) = M_{i,0}(h_{out}(p))$  and  $\tau(p) = \tau(h_{out}(p))$  for all  $p \in S_i^o$ ;

(vii) *t* is disabled in the initial marking  $M_{i,0}$  for all  $t \in (T_i - t_{in})$ .

A subnet may, in turn, contain super-transitions. It is straightforward to prove that the net  $N_1$  of Figure 5.5 is indeed a semi-refinement of  $S_1$  in the net of Figure 5.6.

If a net  $N_i$  is the semi-refinement of some super-transition  $S_i$ , it is possible to *characterize*  $N_i$  in terms of both function and time by putting tokens in its in-ports and then observing the value and time stamp of tokens in its out-ports after a certain firing sequence. If the time stamp of all tokens deposited in the in-ports of  $N_i$  is zero, the token time of tokens obtained in the out-ports is called the *execution time* of  $N_i$ . For example, the net  $N_1$  shown in Figure 5.5 can be characterized by putting tokens  $k_a = \langle v_a, 0 \rangle$  and  $k_b = \langle v_b, 0 \rangle$  in its in-ports and observing the token  $k_d = \langle v_d, r_d \rangle$  after firing  $t_{in}$  and  $t_{out}$ . Thus the execution time of  $N_1$  is equal to the token time  $r_d$ , bounded in this case by  $d_{in}^- + d_{out}^- \leq r_d \leq d_{in}^+ + d_{out}^+$ . Note the token value  $v_d$  is given by  $v_d = f_{out}(f_{in}(v_a, v_b))$ , where  $f_{in}$  and  $f_{out}$  are the transition functions of  $t_{in}$  and  $t_{out}$  respectively.

The definition of semi-abstraction/refinement is just "syntactic sugar" that allows a complex design to be constructed in a structured way by composing simpler entities. We have not defined, so far, a semantic relation between the functionality of super-transitions and their refinements. Below we define the concepts of *strong* and *weak refinement* of a super-transition.

**Definition 5.15.** A subnet  $N_i = (P_i, T_i, \Lambda_i, I_i, O_i, M_{i,0})$  is a strong

refinement of the super-transition  $S_i \in \Lambda$  together with its surrounding places in the net  $H=(P, T, \Lambda, I, O, M_0)$  (or  $S_i$  and its surrounding places is a *strong abstraction* of  $N_i$ ) iff:

(i)  $N_i$  is a semi-refinement of  $S_i$ ;

(ii)  $N_i$  "implements"  $S_i$ , that is,  $N_i$  is function-equivalent to  $S_i$  and its surrounding places;

(iii) The minimum estimated delay  $e_i^{-}$  of  $S_i$  is equal to the lower bound of the execution time of  $N_i$ ;

(iv) The maximum estimated delay  $e_i^+$  of  $S_i$  is equal to the upper bound of the execution time of  $N_i$ .

The subnet  $N_1$  shown in Figure 5.5 is a semi-refinement of  $S_1$  in the net of Figure 5.6.  $N_1$  is a strong refinement of the supertransition  $S_1$  if, in addition: (a)  $g_1 = f_{out} \circ f_{in}$ ; (b)  $e_i = d_{in} + d_{out}$ ; (c)  $e_i^+ = d_{in}^+ + d_{out}^+$  (Definitions 5.15(ii), 5.15(iii), and 5.15(iv) respectively).

Observe that the concept of strong refinement requires the super-transition and its strong refinement to have the very same time limits. Such a concept could have limited practical use, from the point of view of a design environment, since the highlevel description and the implementation perform the same function but typically have different timings and therefore their bounds for the execution time do not coincide. Nonetheless, the notion of strong refinement can be very useful for abstraction purposes. We relax the requirement of exact correspondence of lower and upper bounds on time; this yields to a weaker notion of refinement.

**Definition 5.16.** A subnet  $N_i = (P_i, T_i, \Lambda_i, I_i, O_i, M_{i,0})$  is a *weak* refinement of the super-transition  $S_i \in \Lambda$  together with its surrounding places in the net  $H = (P, T, \Lambda, I, O, M_0)$  (or  $S_i$  and its surrounding places is a *weak abstraction* of  $N_i$ ) iff:

(i)  $N_i$  is a semi-refinement of  $S_i$ ;

(ii)  $N_i$  "implements"  $S_i$ , that is,  $N_i$  is function-equivalent to  $S_i$  and its surrounding places;

(iii) The minimum estimated delay  $e_i$  of  $S_i$  is less than or equal

to the lower bound of the execution time of  $N_i$ ;

(iv) The maximum estimated delay  $e_i^+$  of  $S_i$  is greater than or equal to the upper bound of the execution time of  $N_i$ .

In the sequel whenever we refer to *refinement* it will mean *weak refinement*.

Given a hierarchical PRES+ net  $H=(P, T, \Lambda, I, O, M_0)$  and refinements of its super-transitions, it is possible to construct an equivalent non-hierarchical net. For the sake of clarity, in the following discussion we will consider nets with a single supertransition, nonetheless these concepts can be easily extended to the general case.

**Definition 5.17.** Let us consider the net  $H=(P, T, \Lambda, I, O, M_0)$ where  $\Lambda=\{S_1\}$ , and let the subnet  $N_1=(P_1, T_1, \Lambda_1, I_1, O_1, M_{1,0})$ be a refinement of  $S_1$  and its surrounding places. Let  $t_{in}$ ,  $t_{out} \in T_1$  be unique in-transition and out-transition respectively. Let  $inP_1$  and  $outP_1$  be respectively the sets of in-ports and outports of  $N_1$ . The equivalent net  $H'=(P', T', \Lambda', I', O', M_0')$ , one level lower, is defined as follows:

(i)  $\Lambda' = \Lambda_1$ ; (ii)  $P' = P \cup (P_1 - inP_1 - outP_1)$ ; (iii)  $T' = T \cup T_1$ ; (iv)  $(p, S) \in I'$  if  $(p, S) \in I_1$ ;  $(p, t) \in I'$  if  $(p, t) \in I$ , or  $(p, t) \in I_1$  and  $p \notin inP_1$ ;  $(p, t_{in}) \in I'$  if  $(p, S_1) \in I$ ; (v)  $(S, p) \in O'$  if  $(S, p) \in O_1$ ;  $(t, p) \in O'$  if  $(t, p) \in O$ , or  $(t, p) \in O_1$  and  $p \notin outP_1$ ;  $(t_{out}, p) \in O'$  if  $(S_1, p) \in O$ ; (vi)  $M_0'(p) = M_0(p)$  for all  $p \in P$ ;  $M_0'(p) = M_{1,0}(p)$  for all  $p \in P_1 - inP_1 - outP_1$ .

We can make use of Definition 5.17 in order to flatten a hierarchical PRES+ model. Given the net of Figure 5.6 and being  $N_1$ (Figure 5.5) a refinement of  $S_1$ , we can construct the equivalent non-hierarchical net as illustrated in Figure 5.7.

Figure 5.7: A non-hierarchical PRES+ model

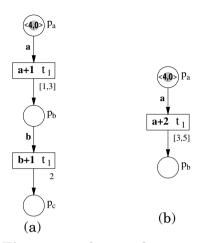

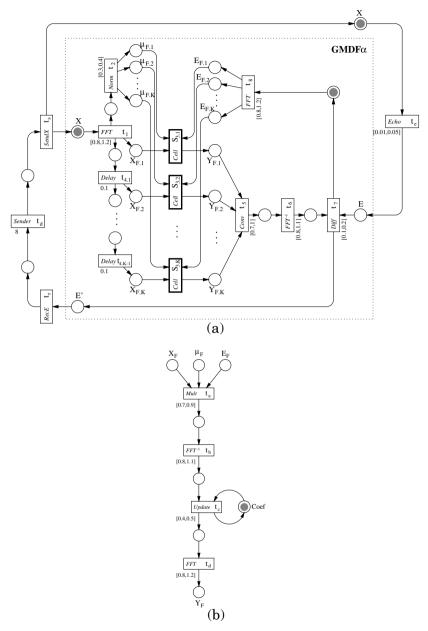

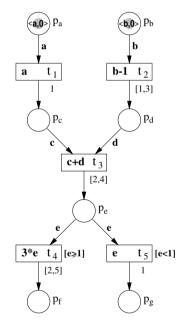

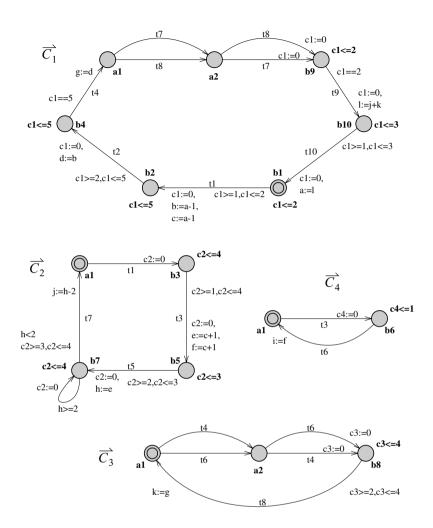

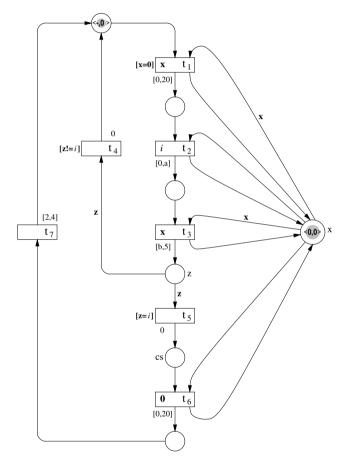

### 5.2.1 Hierarchical Modeling of a GMDF $\alpha$

In this section we model a GMDF $\alpha$  (Generalized Multi-Delay frequency-domain Filter) [Fre97] using PRES+. GMDF $\alpha$  has been used in acoustic echo cancellation for improving the quality of hand-free phone and teleconference applications. The GMDF $\alpha$  algorithm is a frequency-domain block adaptive algorithm: a block of input data is processed at one time, producing a block of output data. The impulse response of length *L* is segmented into *K* smaller blocks of size *N* (*K*=*L*/*N*), thus leading to better performance. *R* new samples are processed at each iteration and the filter is adapted  $\alpha$  times per block (*R*=*N*/ $\alpha$ ).

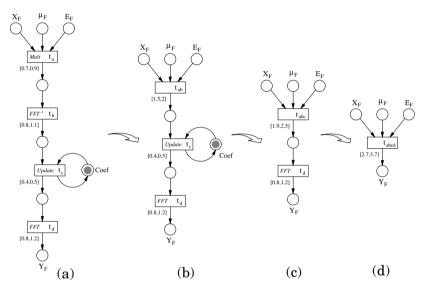

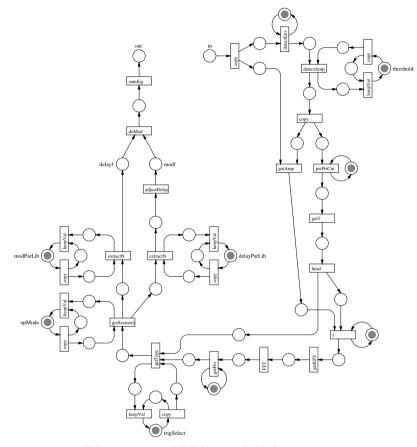

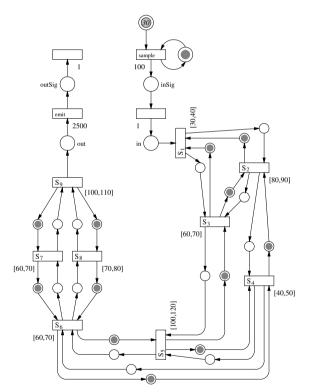

The filter inputs are the signal X and its echo E, and the output is the reduced or cancelled echo E'. In Figure 5.8 we show the hierarchical PRES+ model of a GMDF $\alpha$ . The transition  $t_1$  transforms the input signal X into the frequency domain by a

Figure 5.8: GMDFα modeled using PRES+

FFT (Fast Fourier Transform).  $t_2$  corresponds to the normalization block. In each one of the basic cells  $S_{3,i}$  the filter coefficients are updated. Transitions  $t_{4,i}$  serve as delay blocks.  $t_5$  computes the estimated echo in the frequency domain by a convolution product and then it is converted into the time domain by  $t_6$ . The difference between the estimated echo and the actual one (signal E) is calculated by  $t_7$  and output as E'. Such a cancelled echo is also transformed into the frequency domain by  $t_8$  to be used in the next iteration when updating the filter coefficients. InFigure 5.8 we also model the environment with which the GMDF $\alpha$  interacts:  $t_e$  models the echoing of signal X,  $t_s$  and  $t_r$ represent, respectively, the sending of the signal and the reception of the cancelled echo, and  $t_d$  is the entity that emits X.

The refinement of the basic cells  $S_{3,i}$  is shown in Figure 5.8(b) where the filter coefficients are computed and thus the filter is adapted by using FFT<sup>1</sup> and FFT operations. Transition delays in Figure 5.8 are given in milliseconds.

This example shows how hierarchy allows systems be structured in an understandable way. It is worth noticing that instances of the same subnet (Figure 5.8(b)) are used as refinements of the different cells  $S_{3,i}$ . Thus, in cases like this one, the regularity of the system can be exploited in order to obtain a more succinct model.

Later, in Section 7.2, we show how the verification of this filter is performed and the advantages of modeling it in this way.

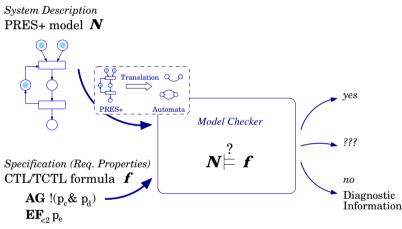

# Chapter 6 Formal Verification of Embedded Systems

AS THE COMPLEXITY of electronic systems increases, the likelihood of subtle errors becomes much greater. A way to cope, to a certain extent, with the issue of correctness is the use of mathematically-based techniques, known as *formal methods*.

Correctness plays a key role in embedded systems. For the levels of complexity typical to modern electronic systems, traditional validation techniques like simulation and testing are not enough to verify the correctness of such systems. First, these methods may cover just a small fraction of the system behavior. Second, bugs found late in prototyping phases have a negative impact on time-to-market. Third, as more applications become dependent on computer systems, a failure may lead to catastrophic situations, e.g. in safety-critical systems like transportation, defense, and medical applications.

In this chapter we introduce our approach to formal verification of real-time embedded systems represented in PRES+. First, we present some preliminaries in order to make clearer the presentation of our ideas. Then, we explain our technique

and propose a translation procedure from PRES+ into the input formalism of existing verification tools. Finally, we illustrate our approach through the verification of a realistic system.

# 6.1 Preliminaries

The purpose of this section is to present preliminary concepts that will be needed for the later discussion.

### 6.1.1 FORMAL METHODS

The weaknesses of traditional validation techniques have stimulated research towards solutions that attempt to prove a system correct. Formal methods are analytical and mathematical techniques intended to prove formally that the implementation of a system conforms its specification. The two well-established approaches to formal verification are *theorem proving* and *model checking* [Cla96].

In theorem proving [Fit96], the idea is to prove a system correct by using axioms and inference rules, in the same sense that a mathematical theorem is proved correct. Both the system and its desired properties are typically expressed as formulas in some mathematical logic. Then, a proof of a given property must be found from axioms and rules of the system. Since theorem proving requires interaction with the user, it is a relatively slow and error-prone process.

On the other hand, model checking [Cla99] is an automatic approach to formal verification used to determine whether the model of a system satisfies a set of required properties. In principle, a model checker exhaustively searches the state space, which must be finite. Model checking is fully automatic and can produce counterexamples for diagnostic purposes. The main disadvantage of model checking is the state- explosion problem. Thus key challenges are the algorithms and data structures that allow handling large search spaces. Formal methods are becoming a practical alternative to ensure the correctness of designs. They might overcome some of the limitations of traditional validation methods. At the same time, formal verification can give a better understanding of the system behavior, help to uncover ambiguities, and reveal new insights of the system. However, formal methods do have limitations and are not the universal solution to achieve correct systems. Formal verification is to complement, rather than replace, simulation and testing methods.

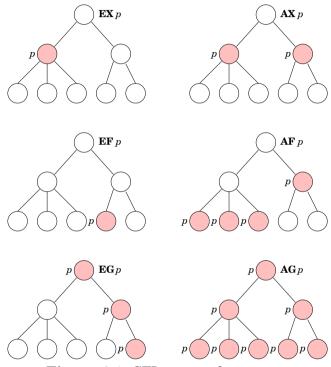

#### 6.1.2 TEMPORAL LOGICS