# UCLA UCLA Electronic Theses and Dissertations

**Title** Optimizing Flash-Based Storage Systems

Permalink https://escholarship.org/uc/item/4h29w76b

**Author** Wang, Haobo

Publication Date

Peer reviewed|Thesis/dissertation

#### UNIVERSITY OF CALIFORNIA

Los Angeles

Optimizing Flash-Based Storage Systems

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Haobo Wang

2018

© Copyright by Haobo Wang

2018

#### ABSTRACT OF THE DISSERTATION

Optimizing Flash-Based Storage Systems

by

Haobo Wang

Doctor of Philosophy in Electrical and Computer Engineering University of California, Los Angeles, 2018 Professor Richard D. Wesel, Chair

This dissertation proposes mathematical algorithms for improving Flash-based storage system's four key performance metrics: lifetime, reliability, latency and throughput.

The first part of the dissertation presents the novel concept of dynamically voltage allocation (DVA) for Flash memory. Flash memory suffers reduced reliability as the number of program/erase (P/E) cycles increases, thus has a limited lifetime. DVA scales the write threshold voltages of Flash memory adaptively, using lower voltages at the beginning of the lifetime, and gradually increases the scaling to combat the effect of accumulated wear-out from P/E cycling. The proposed algorithm significantly increases the lifetime of the device.

The second part of the dissertation introduces the novel design of error correction using incremental redundancy without feedback. Modern storage systems often require high throughput, high reliability and low latency. Traditional variable-length (VL) codes with feedback have demonstrated to provide high throughput and reliability. The new design reinterprets the results for VL codes with feedback using ergodicity, by encoding the incremental redundancy of multiple VL codewords to a common pool of redundancy. The removal of feedback allows storage systems to benefit from the performance of a feedback scheme with a feedforward design. The decoder of the new design exploits the low complexity of shortblocklength decoders and the parallelization structure to reduce latency. The proposed error correction scheme approaches the throughput of corresponding VL codes with feedback. Relying on information theory and coding theory, the proposed algorithms provide new approaches to optimize the Flash-based storage systems.

The dissertation of Haobo Wang is approved.

Adnan Youssef Darwiche

Babak Daneshrad

Lieven Vandenberghe

Richard D. Wesel, Committee Chair

University of California, Los Angeles

2018

To my parents.

# TABLE OF CONTENTS

| 1                                                                    | Ove  | rview     |                                                                    | 1        |

|----------------------------------------------------------------------|------|-----------|--------------------------------------------------------------------|----------|

| 2 Using Dynamic Allocation of Write Voltage to Extend Flash Memory I |      |           |                                                                    |          |

|                                                                      | time | 9         |                                                                    | <b>5</b> |

|                                                                      | 2.1  | Introduct | ion                                                                | 5        |

|                                                                      | 2.2  | Modeling  | Channel Parameters & Degradation                                   | 9        |

|                                                                      |      | 2.2.1 C   | hannel Model with Additive Components                              | 10       |

|                                                                      |      | 2.2.2 C   | hannel Parameter Degradation Model                                 | 15       |

|                                                                      |      | 2.2.3 M   | odels Used in This Chapter                                         | 18       |

|                                                                      | 2.3  | Dynamic   | Voltage Allocation with Ideal Channel Information                  | 19       |

|                                                                      | 2.4  | Channel   | Parameter Estimation                                               | 26       |

|                                                                      |      | 2.4.1 C   | hannel Parameter Estimation Problem Formation                      | 27       |

|                                                                      |      | 2.4.2 Le  | east Squares Algorithms                                            | 28       |

|                                                                      |      | 2.4.3 Bi  | inning Strategy                                                    | 31       |

|                                                                      | 2.5  | Dynamic   | Voltage Allocation with Model/Channel Mismatch                     | 36       |

|                                                                      |      | 2.5.1 M   | odel 1                                                             | 37       |

|                                                                      |      | 2.5.2 M   | odel 2                                                             | 39       |

|                                                                      | 2.6  | Comparis  | son of Dynamic Voltage Allocation and Dynamic Threshold Assignment | 40       |

|                                                                      | 2.7  | Dynamic   | Voltage Allocation when Voltage Placements are Quantized           | 42       |

|                                                                      | 2.8  | Complexi  | ty Analysis                                                        | 44       |

|                                                                      | 2.9  | Conclusio | m                                                                  | 47       |

|    | 2.10            | Chanr   | nel Parameters Used in This Chapter                        | 48 |

|----|-----------------|---------|------------------------------------------------------------|----|

|    | 2.11            | Ackno   | wledgment                                                  | 48 |

| 3  | Cod             | ling wi | ith Shared Incremental Redundancy                          | 49 |

|    | 3.1             | Introd  | luction                                                    | 49 |

|    | 3.2             | Archit  | Secture                                                    | 51 |

|    | 3.3             | Gener   | alized Peeling Decoder Analysis                            | 54 |

|    |                 | 3.3.1   | Generalized Peeling Decoder (GPD)                          | 55 |

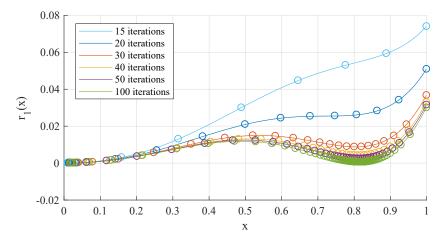

|    |                 | 3.3.2   | Computation of $r_1(t)$ a.k.a. $r_1(x)$                    | 56 |

|    |                 | 3.3.3   | Computing Probability of Left Node Failure $\epsilon_{FF}$ | 60 |

|    |                 | 3.3.4   | Throughput of Feedback and Feedback-Free Systems           | 61 |

|    |                 | 3.3.5   | Throughput Loss in the Feedback-Free System                | 62 |

|    | 3.4             | Design  | n Methods                                                  | 64 |

|    |                 | 3.4.1   | VL Code Design                                             | 64 |

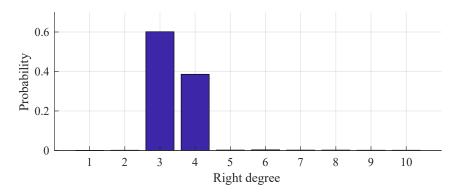

|    |                 | 3.4.2   | Design the Inter-Frame Degree Distribution                 | 72 |

|    |                 | 3.4.3   | Bipartite Graph Design                                     | 75 |

|    | 3.5             | Result  | 55                                                         | 76 |

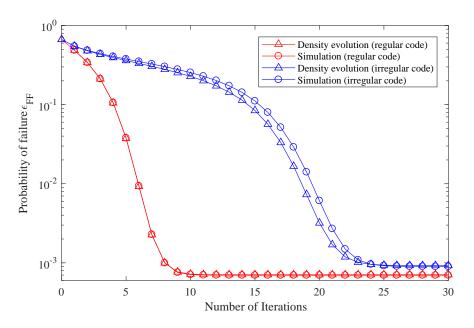

|    |                 | 3.5.1   | Convolutional VL Code Based System                         | 76 |

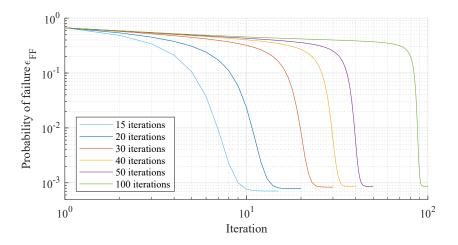

|    |                 | 3.5.2   | NB-LDPC VL Code based System                               | 80 |

|    | 3.6             | Conclu  | usion                                                      | 85 |

|    | 3.7             |         | wledgment                                                  | 86 |

| Re | e <b>fere</b> i | nces .  |                                                            | 87 |

# LIST OF FIGURES

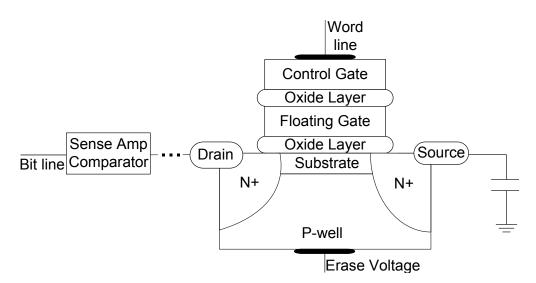

| 1.1 | Common structure of a P-well Flash memory cell                                   | 2  |

|-----|----------------------------------------------------------------------------------|----|

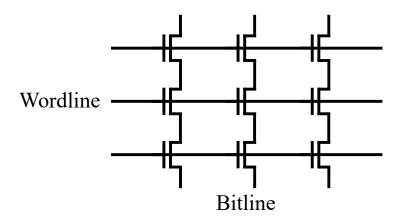

| 1.2 | NAND Flash memory cell grid.                                                     | 3  |

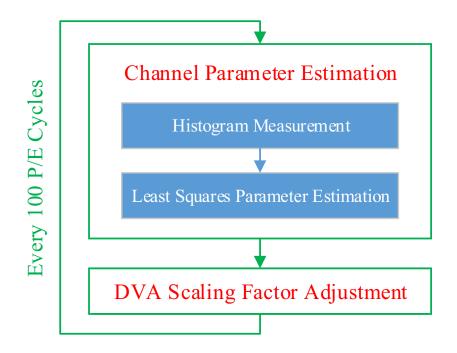

| 2.1 | Estimation-based DVA framework.                                                  | 7  |

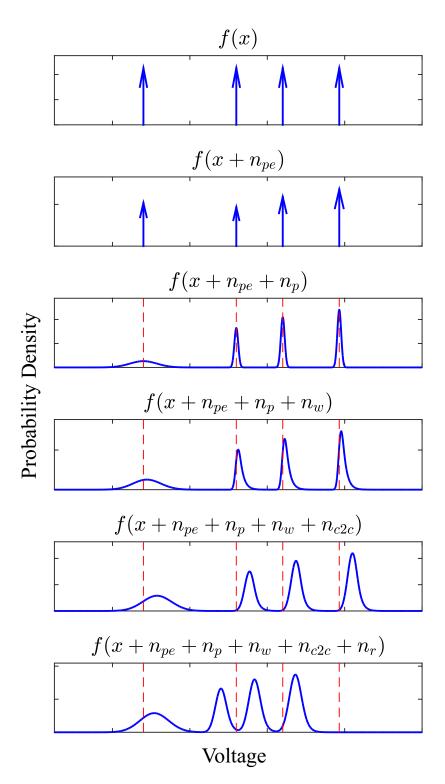

| 2.2 | Flash read channel PDFs illustrating how the probability density of voltage      |    |

|     | thresholds is affected by various noise components.                              | 11 |

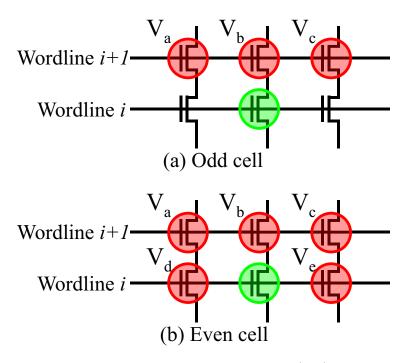

| 2.3 | Spacial relationship between the interfering cells (red) and interfered cells    |    |

|     | (green). Flash memory is written wordline by wordline, i.e., wordline $i + 1$ is |    |

|     | written after wordline $i$ . For the interference shown above, within a wordline |    |

|     | even cells are written before odd cells.                                         | 13 |

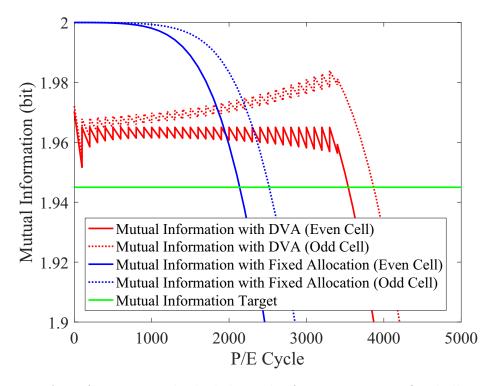

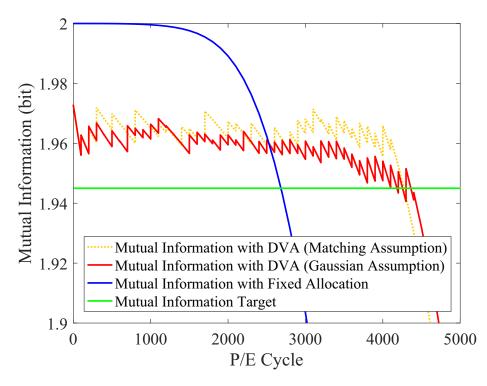

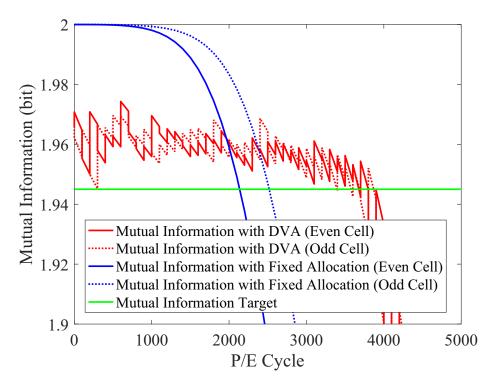

| 2.4 | DVA performance with ideal channel information versus fixed allocation's per-    |    |

|     | formance. (Ground truth channel is Model 2. DVA targets even channel.            |    |

|     | Channel parameters are listed in the Sec. 2.10.)                                 | 23 |

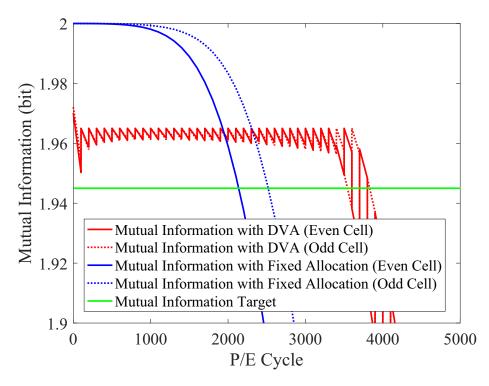

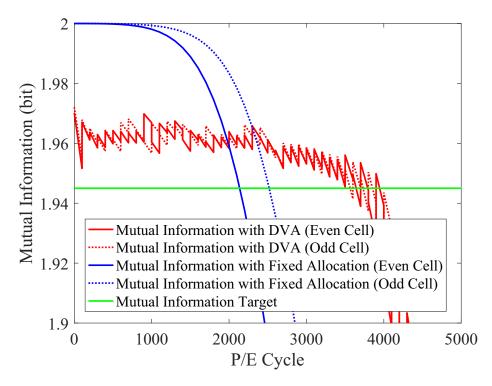

| 2.5 | DVA performance with ideal channel information and the performance of the        |    |

|     | fixed allocation. (The ground truth channel is Model 2. The writing order        |    |

|     | of pages is switched every 100 P/E cycles. Joint DVA is use to adjust both       |    |

|     | scaling factors for even and odd cells. Channel parameters are listed in Sec.    |    |

|     | 2.10.)                                                                           | 24 |

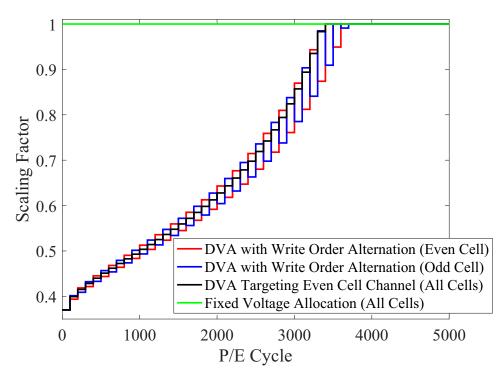

| 2.6 | Scaling factors generated by DVA with ideal channel information. (Result         |    |

|     | corresponds to Fig. 2.4 and 2.5. Ground truth model is Model 2. Channel          |    |

|     | parameters are listed in Sec. 2.10. The starting value of $\alpha$ is 0.37.)     | 25 |

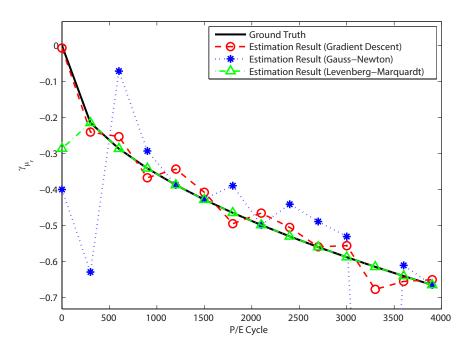

| 2.7  | Estimation result versus ground truth for $\gamma_{\mu_r}$ using 10-bin equal-probability        |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | histogram.                                                                                       | 30 |

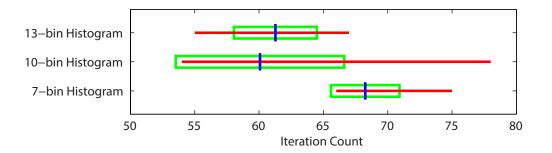

| 2.8  | Iteration count statistics using Levenberg-Marquardt algorithm                                   | 32 |

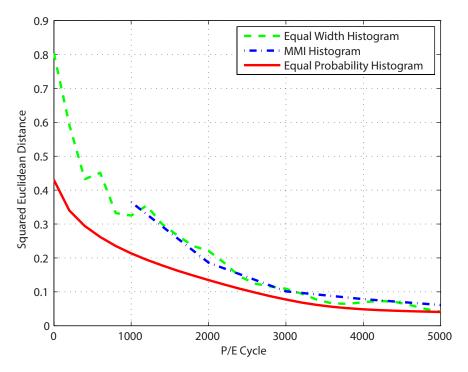

| 2.9  | Squared Euclidean distance between the channel distributions and correspond-                     |    |

|      | ing histograms (10 bins)                                                                         | 34 |

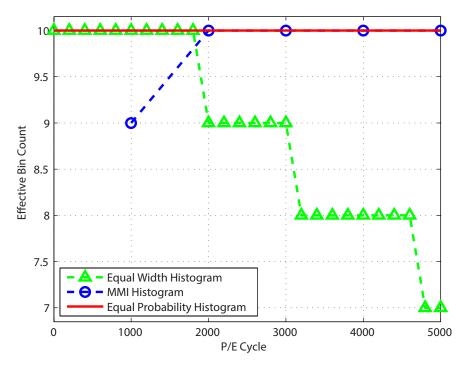

| 2.10 | Effective resolution of different histograms (10 bins).                                          | 35 |

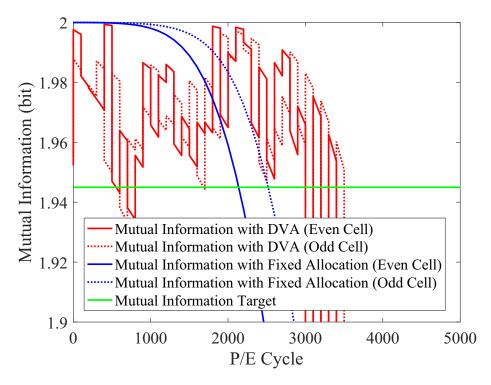

| 2.11 | DVA's performance with multi-modal Gaussian model. (Ground truth model                           |    |

|      | is Model 1. Channel parameters are listed in Sec. 2.10.)                                         | 37 |

| 2.12 | DVA performance with multi-modal Gaussian model. (The Ground truth                               |    |

|      | model is Model 2. Channel parameters are listed in Sec. 2.10. The lifetime                       |    |

|      | of even cells is extended by 70.5% from 2136 P/E cycles to 3642 P/E cycles.                      |    |

|      | The lifetime of odd cells is extended by $41.6\%$ from 2517 P/E cycles to 3564                   |    |

|      | $\mathrm{P/E}$ cycles. The overall lifetime is extended by 66.9% from 2136 $\mathrm{P/E}$ cycles |    |

|      | to 3564 P/E cycles.) $\ldots$                                                                    | 38 |

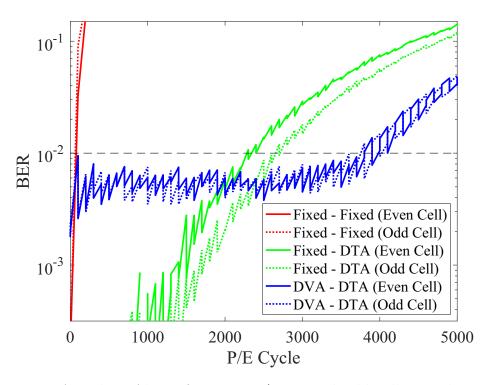

| 2.13 | DTA and DVA's performance. (Even and odd cells switch positions when                             |    |

|      | using DVA. The legend follows the format write voltage allocation algorithm                      |    |

|      | - read voltage allocation algorithm. Comparing the result from DVA - DTA                         |    |

|      | with Fixed - DTA, The lifetime of even cells is extended by $66.5\%$ from $2282$                 |    |

|      | $\mathrm{P/E}$ cycles to 3800 P/E cycles. The lifetime of odd cells is extended by $41.4\%$      |    |

|      | from 2654 P/E cycles to 3754 P/E cycles. The overall lifetime is extended by                     |    |

|      | $64.5\%$ from 2282 P/E cycles to 3754 P/E cycles.) $\hdots$                                      | 41 |

| 2.14 | DVA performance with quantized placements. (Quantization provides 64 pos-                        |    |

|      | sible locations. Ground truth model is Model 2. Channel parameters are listed                    |    |

|      | in Sec. 2.10.)                                                                                   | 42 |

| 2.15 | DVA's performance with quantized placements. (Quantization provides 128                                                         |    |

|------|---------------------------------------------------------------------------------------------------------------------------------|----|

|      | possible locations. Ground truth model is Model 2. Channel parameters are                                                       |    |

|      | listed in Sec. 2.10. The lifetime of even cells is extended by $72.1\%$ from $2136$                                             |    |

|      | $\rm P/E$ cycles to 3676 $\rm P/E$ cycles. The lifetime of odd cells is extended by 34.8%                                       |    |

|      | from 2517 P/E cycles to 3393 P/E cycles. The overall lifetime is extended by                                                    |    |

|      | 58.8% from 2136 P/E cycles to 3393 P/E cycles.) $\ldots \ldots \ldots \ldots \ldots$                                            | 43 |

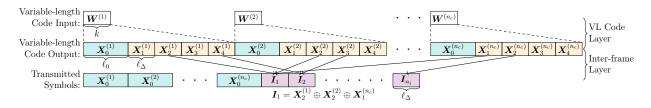

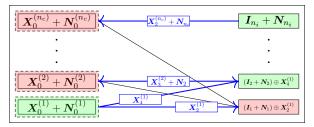

| 3.1  | Inter-frame encoder structure. $\boldsymbol{W}_i$ is a k-bit message, $\boldsymbol{X}_0^{(i)}$ is a length- $\ell_0$            |    |

|      | vector, and $\{\boldsymbol{X}_1^{(i)},\ldots,\boldsymbol{X}_4^{(i)}\}$ and $\boldsymbol{I}_j$ are length- $\ell_\Delta$ vectors | 52 |

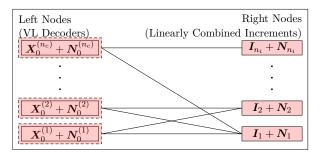

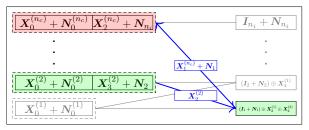

| 3.2  | Decoding process of an inter-frame coding system with the inter-frame layer                                                     |    |

|      | represented as a bipartite graph                                                                                                | 53 |

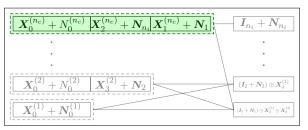

| 3.3  | Example $r_1(x)$ from density evolution and equation (3.8) for $\lambda(x) = x^3$ and                                           |    |

|      | the irregular $\rho_{PEG}(x)$ in Section 3.5.2. The VL code characterization PMF                                                |    |

|      | $\boldsymbol{\delta} = [0.30909, 0.464, 0.1939, 0.02934, 0.00318, 0.00049].$                                                    | 60 |

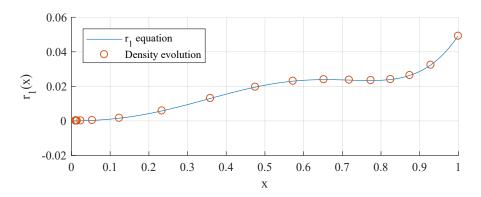

| 3.4  | Probability of failure mechanisms of right nodes for the irregular $\rho_{PEG}(x)$ in                                           |    |

|      | Section 3.5.2                                                                                                                   | 63 |

| 3.5  | Example right degree distribution $\rho_{DE}(x)$ from differential evolution as de-                                             |    |

|      | scribed in Sec. 3.5.2.                                                                                                          | 74 |

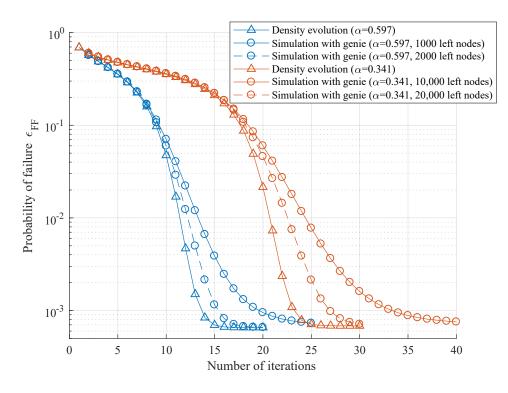

| 3.6  | Probability of failure versus the number of iterations of the convolutional VL                                                  |    |

|      | Code based feedback-free system.                                                                                                | 78 |

| 3.7  | $r_1(x)$ versus x for Table 3.5. The curves are generated using equation (3.8).                                                 |    |

|      | Circles indicate iteration points determined through density evolution                                                          | 79 |

| 3.8  | Probability of failure versus iterations for $\rho_{QR}(x)$ distributions in Table 3.5.                                         |    |

|      | The curves are generated using density evolution                                                                                | 79 |

| 3.9  | Probability of failure versus the number of iterations for the designs in Table                                                 |    |

|      | 3.7 from density evolution and genie-aided simulations                                                                          | 83 |

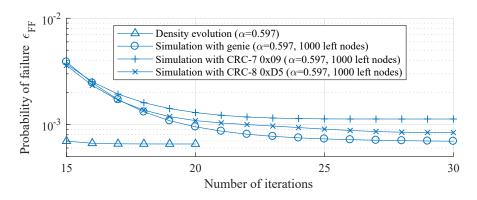

| 3.10 | Probability of failure versus the number of iterations for the $\alpha = 0.597$ 1000- |    |

|------|---------------------------------------------------------------------------------------|----|

|      | left-node design in Table 3.8 from density evolution, simulations with a genie-       |    |

|      | aided decoder and decoders using CRCs                                                 | 84 |

# LIST OF TABLES

| 2.1 | Converge counts of least square algorithms (over 14 cases)                                   | 31 |

|-----|----------------------------------------------------------------------------------------------|----|

| 2.2 | Computational complexity of read threshold voltage allocation                                | 45 |

| 2.3 | Computational complexity of Levenberg-Marquardt algorithm                                    | 45 |

| 2.4 | Computational complexity of scaling factor adjustment                                        | 46 |

| 2.5 | Channel parameters used in this chapter                                                      | 48 |

| 3.1 | Performance comparison between the $k = 64$ 1024-state TBCC VL code's VI                     |    |

|     | and CI designs. (2 dB BI-AWGN, $m = 5$ , target $\epsilon_{FB} = 10^{-3}$ for the first two  |    |

|     | rows, target $\epsilon_{FB} = 5 \times 10^{-4}$ for the third row)                           | 67 |

| 3.2 | The first 5 combinations for the first symbol of the rate 0.75 NB-LDPC code.                 | 71 |

| 3.3 | Performance comparison between the $K = 24$ NB-LDPC VL code with ACK/NA                      | CK |

|     | feedback's VI and CI designs. (2dB BI-AWGN, $m = 5$ , target $\epsilon_{FB} = 10^{-3}$ for   |    |

|     | the first two rows, target $\epsilon_{FB} = 5 \times 10^{-4}$ for the third row)             | 71 |

| 3.4 | Performance of the convolutional VL code based feedback-free systems                         | 77 |

| 3.5 | Density evolution performance characteristics of quasi-regular $\rho_{QR}(x) = \alpha x^2 +$ |    |

|     | $(1-\alpha)x^3$ for the convolutional VL code based feedback-free system. $\lambda(x)=x^3$   |    |

|     | in all cases.                                                                                | 79 |

| 3.6 | Density evolution performance characteristics of the highest $R_t^{(FF)}$ (lowest-           |    |

|     | $\beta_{FF}$ ) quasi-regular right degree distributions for the convolutional VL code        |    |

|     | based feedback-free system. $\lambda(x) = x^3$ in all cases                                  | 80 |

| 3.7 | Density evolution performance characterization of quasi-regular $\rho_{QR}(x)$ =    |    |

|-----|-------------------------------------------------------------------------------------|----|

|     | $\alpha x^2 + (1 - \alpha)x^3$ for the NB-LDPC VL code based feedback-free system.  |    |

|     | $\lambda(x) = x^3$ in all cases                                                     | 82 |

| 3.8 | Right degree distributions of the PEG generated inter-frame bipartite graphs        |    |

|     | in Fig. 3.9                                                                         | 82 |

| 3.9 | Probability of failure of 1000-left-node $\alpha = 0.597$ code from Table 3.8 simu- |    |

|     | lated with CRCs                                                                     | 84 |

#### ACKNOWLEDGMENTS

This dissertation summarizes my multi-year research effort as a graduate student at University of California, Los Angeles (UCLA). This long march would not have been possible without the support and guidance from my family, friends, colleagues and advisors.

I would like to express my deepest gratitude to my advisor and chairman of my doctoral committee Prof. Richard D. Wesel. I first met Prof. Wesel as a student attending his channel coding course. It is through his deep insights and excellent teaching that I discovered the importance of information theory and coding theory in today's information technology landscape. Through his encouragement, I joined his research group to work on important theoretical challenges that have many practical manifestations. His deep knowledge on a vast amount of subjects and tireless guidance enabled my transition from a student to a researcher. From resolving simple logistics issues in the research group, to honing my writing and presenting skills, to teaching me creative ways to identify and solving theoretical problems, his efforts made my doctoral tenure not only productive, but also fun. His deep connections in the industry provided me with opportunities to gain first-hand experience in solving real engineering problems, which also contributed to my research efforts. As a researcher, as a teacher, and as a friend, Prof. Wesel demonstrated what an exceptional advisor should be. I am honored to have the chance to work with him.

I would also like to thank Prof. Dariush Divsalar. I benefited greatly from his immense experience and insights in both theory and engineering. I am greatly thankful to the rest of my committee members: Prof. Adnan Youssef Darwiche, Prof. Babak Deneshrad and Prof. Lieven Vandenberghe, for their contribution in this dissertation and my doctoral tenure.

As a member of UCLA Communications Systems Laboratory (CSL), I learned greatly from my colleagues in the research group that have worked with me: Dr. Kasra Vakilinia, Dr. Sudarsan V.S. Ranganathan, Nathan Wong, Alexander M. Baldauf, Christopher K. Bachelor, Adam Belhouchat, and Ethan Liang. As the senior student in the group for the majority of my doctoral tenure, Kasra helped me gain a foothold, and showed to me how to be an exceptional doctoral student. Working with Nathan has always been productive and fun. Alexander, Christopher, Adam and Ethan amazed me how much they can achieve through research as undergraduate students. Especially, I want to thank Sudarsan. Sudarsan and I joined the group at around the same time. I deeply cherish my discussions and arguments with him ranging from research problems to politics. His hardworking attitude and passion towards both research and life will always inspire me in my future endeavors. I also want to thank my colleagues that I did not get a chance to work with: Dr. Adam Williamson, Dr. Chung-Yu Lou, Tong Mu, Chris Miller, Gourav Khadge, Will Chuang, Hengjie Wang and Linfang Wang.

Outside of UCLA, I want to thank Mr. Aldo Cometti at Western Digital. I gained valuable engineering-problem-solving skills through my internship under the guidance of Mr. Cometti. I am grateful for all the time and effort he put into my internship.

Most importantly, I want to dedicate this dissertation to my parents. It is your love, support and great sacrifice that have lifted my life trajectory to this day. I would not have achieved so much without you.

Finally, I want to thank UCLA for providing the institutional support for my doctoral tenure. I express great appreciation to UCLA and National Science Foundation for their financial support.

#### Vita

- 2014 Master of Science, Electrical Engineering University of California, Los Angeles

- 2015 PhD Candidate, Electrical Engineering University of California, Los Angeles

#### Selected Publications

**H. Wang**, T. Chen, and R. D. Wesel, "Histogram-based Flash channel estimation", in *Proceedings of 2015 IEEE International Conference on Communications (ICC)*, London, UK, June 2015, pp. 283–288.

**H. Wang**, N. Wong, and R. D. Wesel, "Dynamic voltage allocation with quantized voltage levels and simplified channel modeling", in *Proceedings of 2015 49th Asilomar Conference on Signals, Systems and Computers*, Pacific Grove, CA, November 2015, pp. 834–838.

**H. Wang**, N. Wong, T. Chen, and R. D. Wesel, "Using dynamic allocation of write voltage to extend Flash memory lifetime", *IEEE Transactions on Communications*, vol. 64, no. 11, pp. 4474–4486, November 2016.

H. Wang, N. Wong, A. M. Baldauf, C. K. Bachelor, S. V. S. Ranganathan, D. Divsalar and R. D. Wesel, "An information density approach to analyzing and optimizing incremental redundancy with feedback", in *Proceedings of 2017 IEEE International Symposium on Information Theory (ISIT)*, Aachen, Germany, June 2017, pp. 261–265.

**H. Wang**, S. V. S. Ranganathan and R. D. Wesel, "Approaching capacity using incremental redundancy without feedback", in *Proceedings of 2017 IEEE International Symposium on Information Theory (ISIT)*, Aachen, Germany, June 2017, pp. 161–165.

**H. Wang** and R. D. Wesel, "Channel code analysis and design using multiple variablelength in parallel without feedback", in *Proceedings of 2018 IEEE Global Communications Conference (GLOBECOM)*, Abu Dhabi, UAE, December 2018, to be published. **H. Wang** and R. D. Wesel, "Coding with shared incremental redundancy: design methods and a non-binary LDPC example", *IEEE Transactions on Communications*, September 2018, submitted for publication.

### CHAPTER 1

### **Overview**

A data storage system usually consists of two components: the storage media and its controller. The storage media is the physical device that stores data, such as optical disks, magnetic disks, and Flash memory cells. The controller is usually the software and hardware implementation of logics that manages the data storage and retrieval process on the storage media, and provides an interface to store and retrieve data to other systems. This dissertation proposes two types of algorithms for the controller which improves the performance of Flash-based storage systems.

The performance of a storage system is usually measured with four metrics: lifetime, reliability, latency and throughput. Lifetime is measured as the amount of time from the point that data is initially stored to the point that the stored data is not be recoverable. Reliability is measured as the probability that data retrieved from the system is not the same as the originally stored data. Latency is measured as the amount of time the system takes from issuing the data retrieval/storage command to the completion of the action. Throughput is measured as the average amount of data the system can store and retrieve in an unit amount of time. An ideal storage system should have a long lifetime, a high reliability, a low latency and a high throughput. However, the fundamental physical characteristics of the storage media dictates the baseline performance metrics of the storage system. Also, physical limitations constrain the ability to improve all four metrics simultaneously. So the controller of practical storage systems need to balance the four metrics, and depending on

Figure 1.1: Common structure of a P-well Flash memory cell.

application, strengthen certain performance metrics at a cost of others.

For a Flash-memory-based storage system, the storage media, i.e. the Flash memory cells, have unique physical characteristics [1, 2, 3, 4]. Fig. 1.1 shows the basic physical structure of a P-well Flash memory cell. The threshold voltage of a Flash cell is largely determined by the amount of charge in the floating gate and the device's intrinsic (chargeneutral) threshold voltage. Electrons are programmed to and erased from the floating gate through the oxide layer to control the threshold voltage. This program and erase (P/E) operation is used to storage data. The threshold voltage level can be obtained by applying a wordline voltage and reading the sense amplifier output to determine if the threshold voltage has been surpassed. This process can be modeled as a point-to-point communication system with a discrete memoryless channel. Due to different types of channel degradation, the measured value of the threshold voltage often differs from the originally stored threshold voltage.

The Flash memory cells are arranged in a dense grid in a Flash memory system to form the basic storage media [1, 3, 4]. Fig. 1.2 shows the cell grid of a typical NAND Flash memory. Each row of cells are connected to the same wordline, and each column of cells are connected head-to-toe through the bitline. Program and erase operation on each row

Figure 1.2: NAND Flash memory cell grid.

or column of cells will impact the stored charge in adjacent rows and columns, and cause additional channel degradation.

In Chapter 2, the concept of dynamically voltage allocation (DVA) is presented as a novel method to combat Flash memory channel degradation. This chapter first introduces Flash channel degradation mechanisms and their corresponding models, and provides a technique to estimate the parameters in the models. From the models it can be concluded that the reliability of Flash memory suffers as the number of P/E cycles increases, thus has a limited lifetime. Then the chapter presents the DVA framework which scales the write threshold voltages of Flash memory adaptively, using lower voltages at the beginning of the lifetime, and gradually increases the scaling to combat the effect of accumulated degradation from P/E cycling. Simulation results show that DVA can significantly increase the lifetime of the system.

Through DVA and other methods, the effect of channel degradation can be greatly mitigated. However, certain amount of degradation will still manifest, causing the retrieved data to contain errors. Error correction code (ECC) is usually used to correct these errors. The ECC algorithm encodes the data to be stored into codewords which contain redundant information, and recovers the stored data using retrieved codewords. The design of the ECC has significant impact on the lifetime, reliability, latency and throughput of the storage system.

In Chapter 3, the design of error correction using shared incremental redundancy is intro-

duced as a novel ECC solution for Flash-based storage systems. Traditional variable-length (VL) codes with feedback have demonstrated to provide high throughput and reliability. The new design reinterprets the results for VL codes with feedback using ergodicity, by encoding the incremental redundancy of multiple VL codewords to a common pool of redundancy [5, 6, 7]. This chapter first introduces the inter-frame coding as the structure of the proposed design. The parallel structure and low complexity of the component short-blocklength codes in our encoder and decoder design can help improve latency. Then the chapter provides a convergence analysis of the proposed generalized peeling decoder for the system. The chapter also provides design demonstrations employing two different types of VL codes. Simulation results show that our designs without feedback approach the throughput, lifetime and reliability.

### CHAPTER 2

# Using Dynamic Allocation of Write Voltage to Extend Flash Memory Lifetime

#### 2.1 Introduction

Flash memory has been widely employed in both consumer electronic devices and industrial electronic systems because of its ability to support high-throughput and low-latency memory access. However, a fundamental issue with Flash technology is that its read channel experiences significant degradation over time which eventually produces unacceptable reliability. As modern Flash solutions provide more storage capacity in smaller form factors, the resulting increase of physical cell density and signal constellation density amplifies the degradation problem.

The degradation can be addressed in different layers in the Flash system. At the device layer three-dimensional cell structures improve durability [8, 9, 10]. At the system level channel codes such as Bose-Chaudhuri-Hocquenghem (BCH) codes [11, 12, 13] and more recently low density parity check (LDPC) codes [14, 15, 16, 17] add redundancy to protect the stored information. In [18], the authors write to cells with a lower voltage but for a longer time to cause less damage at the expense of increased write time. The resulting scheme provides lifetime extension while still guaranteeing a desired write throughput.

The degradation over time is often modeled as a function of the number of program and erase (P/E) cycles, so a direct solution is reducing the number of P/E cycles needed. Write-

once memory (WOM) codes [19, 20, 21, 22] provide one approach to reduce the number of P/E cycles required to store information by permitting multiple writes before an erase cycle is needed. Another way to reduce the number of P/E cycles is rank modulation [23, 24, 25], which stores information in the cell using the relative value (or ordering) of cell charge levels rather than the absolute value. Thus a block of cells can be rewritten without erasing by adding charge to properly re-order the cells.

Several papers have explored dynamically adjusting to the degrading read channel [26, 27, 28]. In [26], read thresholds are progressively adjusted to minimize hard decoding BER or provide better log-likelihood for soft decoding based on previous reads. In [27, 28], dynamic threshold assignment (DTA) adjusts the read thresholds to match the shifting and widening threshold voltage distributions of the read channel, significantly improving bit error rate (BER) performance.

In contrast to the P/E-cycle-based degradation model, this chapter models the degradation as a function of the cumulative effect of the charge written and erased from the cell, which we call the accumulated voltage  $V_{acc}$ . The accumulated voltage model reveals the opportunity to improve lifetime by minimizing the  $V_{acc}$  required to store a given amount of information. In particular, this chapter explores dynamically adjusting the target threshold voltage levels by using lower target write threshold voltage levels at the beginning of the device lifetime. This approach is called dynamic voltage allocation (DVA) [29, 2, 3, 4]. As the read channel becomes more degraded, the threshold voltages are gradually increased to what would be the nominal values in a standard device not employing DVA.

Fig. 2.1 illustrates the basic structure of the DVA approach. Periodically (every 100 P/E cycles in the figure) multiple reads using different read thresholds produce a histogram of the threshold voltages of the cells on the page or pages considered. A parameter-based least-squares channel estimation determines the quality of the read channel from this histogram. Based on the channel estimation, write threshold voltages are set to be as low as possible while still ensuring that the read channel has sufficient mutual information to be successfully

Figure 2.1: Estimation-based DVA framework.

decoded.

This chapter systematically explains and demonstrates the concept of DVA, and addresses several issues to support a practical implementation in the following ways:

- 1. Providing a comprehensive summary of Flash memory read channel degradation models;

- 2. Introducing the histogram-based Flash channel estimation as a method to estimate channel information in a practical system;

- 3. Summarizing the DVA algorithm, and analyzing DVA's performance with perfect channel information;

- 4. Analyzing DVA's performance when both estimation and scale-factor adjustment algorithms are simplified by using a simple Gaussian model to approximate the underlying (and more complex) ground truth channel;

- Designing and analyzing DVA specialized to match an even-odd structure for writing to cells;

- 6. Exploring the improvement obtained by DVA over DTA;

- 7. Analyzing DVA's performance when both write and read voltage values are restricted to a finite set of available voltages;

- 8. Analyzing DVA's complexity.

DVA is first explored under the assumption of perfect knowledge of the channel state as in the paper [29], except with a more complex read channel that includes cell-to-cell interference and programming errors. This chapter introduces DVA in an idealized setting and then removes ideal assumptions about channel knowledge and threshold resolution to conclude with a practical scheme that has performance similar to that of the idealized setting.

Then the performance of DVA is explored when it must gain its channel information through estimation. All dynamic schemes such as DTA and DVA require some form of information about the read channel, and different methods can be employed to acquire the information. For DTA, knowledge of the voltage distribution is needed. In [27], repetitive read operations are needed at relatively precise voltages to enable a bisection algorithm to place the read thresholds. In [28], threshold measurements of a certain number of cells are required.

As shown in Fig. 2.1, our approach to acquire read channel information is to measure a limited-resolution histogram and interpret this histogram using certain assumptions about the channel model. In [30], the authors model the Flash read channel as a multi-modal Gaussian distribution with means and variances as parameters, and demonstrate that least squares algorithms estimate the means and variances well with histograms having as few as twelve bins. These estimated parameters are used to set read thresholds according to [31].

This channel estimation is first performed with a perfect channel model. Next, this chapter explores the practical scenario in which the channel model does not perfectly represent the true channel. This mismatch is both a reflection of the imperfect characterization information available about a specific Flash device and the fact that, even with perfect knowledge of the channel model, simpler models might be preferable because they reduce the complexity of estimation.

Next, we explore how constraining the resolution of write and read thresholds affects performance. We also compare the performance of DVA to DTA and analyze complexity of the DVA framework. Possible solutions to reduce the cost of implementing DVA are proposed. Throughout the chapter, Multi-level Cell (MLC) Flash (with four levels) is assumed for all the models and simulations.

The remainder of this chapter is organized as follows: Sec. 2.2 presents the complete channel model. Sec. 2.3 introduces DVA using the complete channel model but in the idealized setting of perfect channel state information. Sec. 2.4 formulates the channel parameter estimation problem and presents the least squares algorithm and binning strategy used in this chapter. Sec. 2.5 examines the practical scenario in which channel estimation and DVA are based on a model that is not perfect but is simpler than the actual channel. Sec. 2.6 compares the performance of DTA and DVA. Sec. 2.7 adds practical constraints on the resolution of the read and write threshold voltages. Sec. 2.8 analyzes the complexity cost of DVA framework. Sec. 2.9 concludes the discussion. Sec. 2.10 provides the channel parameters used in this chapter. Sec. 2.11 presents the acknowledgment.

#### 2.2 Modeling Channel Parameters & Degradation

Because the interfaces are proprietary, we are not able to measure data from actual flash devices. Instead, we use the models introduced in this section to generate the noise that reflects the behavior of the Flash memory read channel. These models are called *ground* truth models, which means that they are used for all simulations. The term "ground truth model" distinguishes these models from less precise simple Gaussian model (which is called the channel model assumption) that are used by the channel estimation and DVA algorithms. Note that all algorithms, regardless of the models they incorporate in their calculations, are simulated on the ground truth models.

The ground truth models are not matched to a particular Flash device, but based on the academic publications we cite as we present the models. We believe these models reflect the major channel degradations and provide a reasonable degradation trajectory over the lifetime of Flash memory. We use these qualitatively correct channel models to show that DVA can counter the major types of degradation in Flash memory channels. The models in this section can be replaced with device-specific models to apply DVA to a particular Flash memory system. In fact, we will show in Sec. 2.5 that DVA does not need a precise channel model to provide a significant improvement in lifetime.

#### 2.2.1 Channel Model with Additive Components

We formulate a Flash memory read channel model with five additive noise components as follows:

$$y = x + n_{pe} + n_p + n_w + n_{c2c} + n_r, (2.1)$$

where voltage x is the intended threshold voltage written to a cell, and y is the measured threshold voltage. Noise  $n_p$  denotes the programming noise,  $n_w$  denotes the wear-out noise,  $n_r$  denotes the retention noise,  $n_{c2c}$  denotes the cell-to-cell interference, and  $n_{pe}$  denotes the programming error.

Fig. 2.2 shows an example of voltage distribution probability distribution functions (PDFs) which demonstrates the additive effect of each noise component. The arrows in the figure represent delta functions.

#### Programming Error $n_{pe}$ [4, 32]

Programming errors occur when a bit of the lower page is mis-read in preparation for writing a bit of the upper page to an MLC cell. Essentially, as the bit of the upper page is written, the error of the first bit is amplified. The programming error is modeled with a probability mass function (PMF). For an intended level x, channel parameter  $P_{x,y} = P(Y = y|X = x)$

Figure 2.2: Flash read channel PDFs illustrating how the probability density of voltage thresholds is affected by various noise components.

is the conditional probability of actually writing y. For MLC Flash, we have

$$P_{x,0} + P_{x,1} + P_{x,2} + P_{x,3} = 1, (2.2)$$

for each  $x \in \{0, 1, 2, 3\}$ . These channel parameters are strongly related to the number of P/E cycles.

This distortion changes the distribution of stored data. For example, if there is no other noise component and the original data is uniformly distributed (i.e. each level is equally likely), programming errors move some writes to higher levels so that the levels are no longer equally likely. Results in [32] indicate that the impact of programming errors becomes significant only after a large number of P/E cycles.

#### Programming Noise $n_p$ [29, 2, 3, 4, 33, 34]

The programming noise is modeled as a Gaussian noise for each level, and the noise variance of programmed states is smaller than that of the erased state because the feedback control loop associated with programming reduces threshold variation. The PDF of the programming noise is represented as

$$f_{n_p}(n_p|x=l) = \begin{cases} \mathcal{N}(0, \sigma_e^2) & \text{if } l = 0\\ \mathcal{N}(0, \sigma_p^2) & \text{if } l > 0 \end{cases}$$

(2.3)

where  $\sigma_e > \sigma_p$ . Index *l* represents the level of the intended threshold voltage level. For MLC Flash,  $l \in \{0, 1, 2, 3\}$  where l = 0 indicates the erased state. Standard deviations  $\sigma_e$  and  $\sigma_p$ are the channel parameters for this component, and remain constant throughout the lifetime of the device.

Figure 2.3: Spacial relationship between the interfering cells (red) and interfered cells (green). Flash memory is written wordline by wordline, i.e., wordline i + 1 is written after wordline i. For the interference shown above, within a wordline even cells are written before odd cells.

#### Wear-out Noise $n_w$ [29, 2, 3, 4, 35, 36, 37, 38, 39, 40]

The wear-out noise is modeled as a positive-side exponential<sup>1</sup> noise for each level, and the slope of the distribution is characterized by the channel parameter  $\lambda$ . The PDF is

$$f_{n_w}(n_w) = \begin{cases} \frac{1}{\lambda} e^{-\frac{n_w}{\lambda}} & \text{if } n_w \ge 0, \\ 0 & \text{if } n_w < 0. \end{cases}$$

(2.4)

Parameter  $\lambda$  increases as the device experiences more P/E cycles (or larger  $V_{acc}$ ).

#### Cell-to-cell Interference $n_{c2c}$ [4, 41, 42]

The cell-to-cell interference experienced by a cell is a weighted sum of the voltage increases in neighboring cells that occur *after* the cell of interest has been written [43]. Fig. 2.3

<sup>&</sup>lt;sup>1</sup>For various device implementations wear-out noise can also be a negative-side exponential or a doublesided exponential (Laplace) distribution. The DVA and channel estimation techniques we present can be applied in all these cases.

shows the spacial relationships between the interfering cells and the cell of interest for Flash memories employing the common even-odd structure for writing and for reading. The green circle indicates the cell of interest, and the red circles indicate the interfering cells. Fig. 2.3(b) shows that even cells, which are written first, suffer interference from the odd cells in that wordline, which are written after the even cells. As is shown in Fig. 2.3(a), the odd cells do not suffer any interference from the even cells in the same wordline because the odd cells are written after the even cells. All the cells in wordline i suffer interference from the neighboring cells in wordline i + 1, which is written after wordline i. The threshold voltage disturbance (increase) of odd cells  $V_{c2c,odd}$  and even cells  $V_{c2c,even}$  caused by this interference can be modeled as

$$V_{n_{c2c,odd}} = \gamma_a V_a + \gamma_b V_b + \gamma_c V_c \,, \tag{2.5}$$

$$V_{n_{c2c,even}} = V_{n_{c2c,odd}} + \gamma_d V_d + \gamma_e V_e \,. \tag{2.6}$$

As shown in Fig. 2.3,  $V_a$ ,  $V_b$ , and  $V_c$  are voltage increases from the cells in the next wordline.  $V_b$  is from the cell directly above the cell of interest.  $V_a$  and  $V_c$  are voltage increases in cells diagonally adjacent on the next wordline that are located either upper left ( $V_a$ ) or upper right ( $V_c$ ). The voltage increases  $V_d$  and  $V_e$  are from adjacent cells on the same wordline that are to the left ( $V_d$ ) or right ( $V_e$ ). When these cells are programmed (subsequent to the programming of the cell of interest), they interfere with the cell of interest according to the coupling factors ( $\gamma$ 's) between the interfering cells and the cell of interest. The magnitude of this noise component is thus related to two factors: the values of the voltage increases as the adjacent cells are written to their intended thresholds and the coupling factors  $\gamma$ .

#### Retention Noise $n_r$ [29, 2, 3, 4, 44, 45, 46, 36, 41]

The retention noise is modeled as a Gaussian random variable with PDF

$$f_{n_r}(n_r) = \frac{1}{\sigma_r \sqrt{2\pi}} e^{-\frac{(n_r - \mu_r)^2}{2\sigma_r^2}}.$$

(2.7)

Both  $\mu_r$  and  $\sigma_r^2$  (characterized in detail below in Sec. 2.2.2) are dynamic channel parameters determined by the number of P/E cycles (or  $V_{acc}$  which will be introduced next), retention time and intended threshold voltage.

#### 2.2.2 Channel Parameter Degradation Model

This subsection presents a model describing how the parameters describing the additive noise terms degrade as a function of P/E operations and retention time. From the discussion in Sec. 2.2.1, this degradation occurs for all the channel parameters except those describing the programming noise  $n_p$ .

#### Degradation model due to P/E operations [29, 2, 3, 4]

The degree of damage to a Flash cell's oxide layer caused by P/E operations is directly related to the volume of charge traveling through the oxide layer [47]. While the channel degradation caused by P/E operations is often modeled as a function of the number of P/E cycles, this model essentially assumes that approximately the same volume of charge travels through the oxide layer during each P/E cycle. The novel approach of DVA is to realize that the intended threshold voltages themselves can be varied over time so that less charge travels through the oxide layer during early P/E cycles when the channel is favorable. Because it is the charge stored in the floating gate that changes the threshold voltage, the difference between the intended threshold voltage and the erased state voltage is a good indicator of the amount of charged transferred. Thus, we define the voltage-based metric  $V_{acc}/V_{max}$  to

characterize P/E cycling where  $V_{acc}$  denotes the accumulated voltage over P/E cycles

$$V_{acc} = \sum_{j=1}^{N} (V_p^{(j)} - V_e), \qquad (2.8)$$

and  $V_{max}$  is the maximum voltage difference between programmed and erased states of a Flash cell. In (2.8), N is the number of P/E cycles,  $V_p^{(j)}$  is the intended threshold in *j*th P/E operation, and  $V_e$  is the intended threshold voltage of the erased state. Only the programming process is considered in this model, because program and erase are symmetric operations from the perspective of the amount of charge passing through the floating gate.

#### Degradation model for the wear-out noise parameter [39, 40]

P/E cycling operations cause the formation of oxide traps and interface traps in the cells [36, 35, 38, 37]. In [45] a power law describes how interface trap density depends on P/E cycle count as follows:  $A_w \cdot (P/E \text{ cycle count})^{k_i}$ , where  $k_i$  and  $A_w$  are constant degradation parameters determined by the underlying physical properties of the Flash device. Replacing the P/E cycle count with  $V_{acc}/V_{max}$  yields our expression for interface trap density:  $A_w \cdot ((V_{acc}/V_{max})^{k_i}))$ . Based on this expression and [39, 40], the wear-out channel parameter  $\lambda$  in (2.4) has a degradation model that can be formulated as

$$\lambda = C_w + A_w \cdot \left(\frac{V_{acc}}{V_{max}}\right)^{k_i},\tag{2.9}$$

where  $C_w$  is another constant degradation parameters in addition to  $k_i$  and  $A_w$ .

#### Degradation model for the retention noise parameter [36, 45, 41]

Retention noise models channel degradation in the form a gradual decrease of threshold voltage. Both trap recovery and electron detrapping contributes to this degradation [44, 45, 46]. In addition to the interface trap density model, [45] suggests that oxide trap density as well can be modeled by a power of the P/E cycle count. With the  $V_{acc}$ -based characterization of P/E cycling, total trap density can be represented as  $A_r \cdot (V_{acc}/V_{max})^{k_i} + B_r \cdot (V_{acc}/V_{max})^{k_o}$ . From [36, 45, 41], we define the degradation model for the retention noise channel parameters  $\mu_r$  and  $\sigma_r^2$  of (2.4) as [29],

$$\mu_r = -(V - V_0) \ln\left(1 + \frac{t}{t_0}\right) \left[A_r \left(\frac{V_{acc}}{V_{max}}\right)^{k_i} + B_r \left(\frac{V_{acc}}{V_{max}}\right)^{k_o}\right],\tag{2.10}$$

$$\sigma_r^2 = 0.1(V - V_0) \ln\left(1 + \frac{t}{t_0}\right) \left[A_r \left(\frac{V_{acc}}{V_{max}}\right)^{k_i} + B_r \left(\frac{V_{acc}}{V_{max}}\right)^{k_o}\right]^2, \qquad (2.11)$$

where voltage V is the intended threshold voltage, and  $V_0$  is the erased state threshold voltage. Degradation parameters  $k_i$ ,  $k_o$ ,  $A_r$  and  $B_r$  are constants determined by the physical properties of individual Flash memory product. Parameter t is the retention time and  $t_0$  is its normalization factor. In this chapter, we study Flash read channel characteristics at a fixed retention target of one year (t = 8760 hours). The techniques presented in this chapter can, of course, be applied for any target retention time.

Note that often in practical systems the calculations in the equations (2.10) and (2.11) may not be easy to implement. The formulae can be simplified to

$$\mu_r = \gamma_{\mu_r} (V - V_0), \tag{2.12}$$

$$\sigma_r = \gamma_{\sigma_r} \sqrt{V - V_0}.$$

(2.13)

#### Cell-to-cell Interference Parameter Model [42]

In [42], the  $\gamma$  parameters in (2.5) are modeled as random variables with truncated Gaussian distributions. The authors of [42] mention that the means of interfering cells'  $\gamma$ 's in the next wordline to be programmed are also random. We simplify the model by assuming the means of all the  $\gamma$ 's are constant. In our research, the parameter model provided in [42] is utilized, and the cell-to-cell interference strength factor is set to s = 0.2 which yields the full set of cell-to-cell interference parameters given in Sec. 2.10. This setting generates a pair of even-cell and odd-cell read channels with sufficient difference and reasonable typicality.

#### Programming Error Parameter Degradation Model [32]

We employ the programming error parameter degradation model proposed in [32].  $P_{X,Y}$  has an exponential relationship with P/E cycle counts.

$$P_{X,Y} = \exp(c_1 x + c_0) \tag{2.14}$$

The parameters  $c_1$  and  $c_0$  are different for each  $P_{X,Y}$ , and variable x indicates the normalized P/E cycle count where the manufacture specified lifetime is used as the normalization factor. In this chapter, the normalization factor is set to 3000 P/E cycles. The resulting  $P_{X,Y}$  expressions for our model are given in the Sec. 2.10.

# 2.2.3 Models Used in This Chapter

The results presented in this chapter are software simulation results based on two channel models that we have constructed based on the literature. Model 1 is the channel model used in [2], which consists of programming noise, wear-out noise and retention noise. Model 2 is the complete channel model introduced in Sec. 2.2.1.

#### Model 1

The channel model in [2] is an exponentially modified Gaussian distribution for each level. Cell-to-cell interference and programming error are not considered in this model. As a result, the channel characteristics of even and odd cells are the same. This channel model is still very similar to the multi-modal Gaussian model.

#### Model 2

The channel model proposed in Sec. 2.2.1 differentiates the even and odd cell read channels, and considers the effect of programming error and cell-to-cell interference.

# 2.3 Dynamic Voltage Allocation with Ideal Channel Information

Dynamic Voltage Allocation (DVA) [29] is an algorithm that uses a single scaling factor  $\alpha$  to attenuate the standard threshold voltages used to write to the cells. The DVA algorithm computes the appropriate scaling factor such that the read channel achieves at least a certain minimal value of mutual information required to support the rate at which information is stored (the rate indicated by the channel code). The range between the smallest and largest intended voltages is scaled so that it expands as the channel becomes more degraded until it reaches the range that would be employed in a system without DVA. In some Flash devices it may be possible to increase the range beyond the standard range without DVA, but that is not a focus of this chapter.

For Flash memory described by Model 1, the mutual information is calculated as the difference of marginal and conditional differential entropies as follows [48]:

$$I(X;Y) = h(Y) - h(Y|X) . (2.15)$$

Random variable Y describes the measured threshold voltage, and X represents the intended threshold voltage. The probability distribution of Y is the channel distribution  $f_Y(y)$ , so

$$h(Y) = -\int_{-\infty}^{+\infty} f_Y(y) \log(f_Y(y)) \,\mathrm{d}y \;. \tag{2.16}$$

The relevant conditional differential entropy is calculated as

$$h(Y|X) = -\int_{-\infty}^{+\infty} \sum_{i=1}^{4} f_{X,Y}(x_i, y) \log\left(f_{Y|X}(y|x_i)\right) dy \quad , \tag{2.17}$$

where the joint distribution is  $f_{X,Y}(x,y) = f_{Y|X}(y|x)P_X(x)$ ,  $P_X(x)$  is the probability mass function of X, and  $f_{Y|X}(y|x)$  is the conditional PDF of Y when the cell is written to a single level indicated by x. Let  $\{v_i\}$  represent the set of default intended threshold voltages, the intended threshold voltage after scaling is  $x_i = \alpha v_i$ , where  $\alpha$  is the scaling factor. As a result, adjusting the scaling factor will change both h(Y) and h(Y|X).

Because the cell-to-cell interference of a certain cell is a function of the threshold voltages of its surrounding cells, the Flash channel described by model 2 is a channel with memory. From [41], equation (2.15) is a lower bound on the actual mutual information because it treats interference as independent noise. Although equation (2.15) underestimates the mutual information, it is still a valid optimization objective function for DVA when cell-to-cell interference is treated as noise by the controller. If cell-to-cell interference is cancelled by signal processing in the controller, then the portion of cell-to-cell interference that is cancelled should be removed from the modeled noise before computing the mutual information.

As discussed in Sec. 2.2, the channel probability distribution function is determined by the distributions of the five noise components. In general, the distribution can be calculated by convolving the five distributions. In [49], a model very similar to the one in Sec. 2.2 is presented and the analytical channel distribution function is calculated. The expression has a relatively high complexity. In this chapter, numerical convolution is used to calculate an approximation of  $f_{Y|X}(y|x)$ . Note that for generating noise used in Monte Carlo simulation it is not necessary to compute this convolution. Rather, the individual noise terms, each of which is relatively simple in distribution, can be generated and added to the original signal.

Our implementation uses a bisection algorithm to find the scaling factor  $\alpha$ . The scaling factor has a range of [0,1], where a scaling factor of 1 corresponds to the maximum allowed threshold voltage for each level (the levels that would be used by a system not implementing DVA). There are two modes for the DVA algorithm. In the first mode, DVA makes adjustments based on the current channel distribution, and aligns the mutual information to a preset threshold that builds in a fixed margin to account for degradation before the scale factor is adjusted again. In the second mode, DVA makes adjustments based on the prediction of channel conditions in a future time point corresponding to the next DVA scale factor update. In this mode, if the channel model and channel parameter degradation models are correct, the mutual information at that future time point will be the target value. We use the first mode in this chapter, because in practice the channel degradation models (especially the parameters in the models) may not accurately reflect the degradation process for device from different manufactures or for the same device under different working conditions (e.g. temperature).

Assuming ideal channel information, which is the exact model and parameters of the channel, a simulation can be conducted where the DVA algorithm adjusts the scale-factor every certain number of P/E cycles. In this chapter, DVA functions every 100 P/E cycles for simplicity. The number of P/E cycles between DVA operations depends on how quickly the channel is varying and the appropriate interval itself might change over the lifetime of the device. For example, near the end of life when the channel is degrading rapidly a smaller interval might be appropriate.

In each iteration of the simulation, the DVA algorithm scales the intended threshold voltages to increase the channel mutual information to a predefined threshold. Because perfect knowledge of the channel state is assumed, the performance indicates the theoretical limit of the algorithm under these ideal conditions. For this ideal simulation we use Model 2, the full channel model presented in Sec. 2.2.

DVA is most effective in extending lifetime when the major channel degradation is caused by the accumulated effect of charge traveling through the oxide layer of the Flash memory cells. Retention loss is the major degradation in this case. In this chapter, the retention time is set to be a year to represent the worst possible channel for which a device is rated. If the actual retention time exceeds the fixed value, the channel could still provide enough mutual information depending on the distance between the actual channel mutual information and the mutual information limit for the channel code. DVA's performance when the retention time is 0 is not investigated, as we believe the lifetime extension achieved by DVA will be limited in this case.

In this chapter, all simulations assume MLC Flash (four levels) with each level used

equally likely, and the target mutual information is 1.945 bits per cell for both even and odd channels. Because raw BER is determined by both the channel condition and the placement of read threshold voltages, there is no simple way to translate between mutual information and BER. However, simulation results show that a target of 1.945 bits achieves a raw BER of  $10^{-2}$  in Fig. 2.12 using DTA to allocate read thresholds. We note that the raw BER of  $10^{-2}$  is shown in [17] to be an operating point for Code 2 in [17] with 6 reads using a version of mutual-information-based DTA. In any case, the mutual information target can be adapted easily to whatever mutual information is needed to support a specific channel code (LDPC, BCH, or other). The target for the DVA algorithm is set to be 1.965 bits to provide an additional 0.02 bits of margin above the code-based target to allow for channel degradation before the next DVA update. The retention time is set to be one year. The default lifetime measured in P/E cycles for the programming error model is set to be 3000 P/E cycles.

The default intended threshold voltages are described by the vector T = [2.8, 5.2, 6.4, 7.86][29]. The actual threshold voltages resulting from DVA updates have the form  $\alpha T$ , and Fig. 2.6 shows how the scale factor  $\alpha$  varies over time. When using fixed voltage allocation, the scaling factor  $\alpha$  is fixed to be 1, so the default intended threshold voltages are used for each level through the entire lifetime of the device. When using DVA the scaling factor  $\alpha$  starts at a value smaller than 1 and increases as the channel degrades until it reaches the value of 1 which corresponds to the maximum voltage levels supported by the device. The full set of channel parameters is given in Sec. 2.10.

For Flash memories using the even-odd write structure presented in Sec. 2.2, the even-cell and odd-cell read channel characteristics are different as even cells are written before odd cells. The even cells experience more severe cell-to-cell interference and provide less mutual information under the same intended threshold voltage allocation. One approach to optimize this type of Flash memory is to have a single DVA optimization process controlled by the mutual information of the even cells, which face the more severe channel conditions. This

Figure 2.4: DVA performance with ideal channel information versus fixed allocation's performance. (Ground truth channel is Model 2. DVA targets even channel. Channel parameters are listed in the Sec. 2.10.)

approach guarantees the worst-case performance. Fig. 2.4 shows that with this approach the DVA algorithm can improve the lifetime of even cells by 65.7% from 2136 P/E cycles to 3540 P/E cycles and odd cells by 53.6% from 2517 P/E cycles to 3867 P/E cycles for the channel defined by the parameters in Sec. 2.10. Fig. 2.6 shows the scale factor  $\alpha$  used for all cells (the black curve). Note the rapid reduction in the mutual information trajectory shown in Fig. 2.4 around the end of lifetime. This rapid reduction occurs after the scaling factor has become one and cannot be further increased as shown in Fig. 2.6.

One problem with the previous approach is that there is a significant performance difference between the even and odd cells. The intended threshold voltages provide too much mutual information margin for the odd cells. In fact, Fig. 2.4 shows the odd-cell mutual information margin increasing over P/E cycles.

This situation is improved by using two separate DVA optimization processes in the

Figure 2.5: DVA performance with ideal channel information and the performance of the fixed allocation. (The ground truth channel is Model 2. The writing order of pages is switched every 100 P/E cycles. Joint DVA is use to adjust both scaling factors for even and odd cells. Channel parameters are listed in Sec. 2.10.)

system, one for the even-cell channel and one for the odd-cell channel. This solution will remove the excessive mutual information margin of the odd-cell channel, but the performance difference measured by lifetime will not be narrowed. One fundamental cause of the problem is that even cells experience more accumulated damage than odd cells.

To address this disparity, we alternate the writing order between even cells and odd cells every 100 P/E cycles. For example, even cells are written before odd cells from 0 to 99 P/E cycles, and odd cells are written before even cells from 100 P/E cycles to 199 P/E cycles. In this way, the two channels can experience similar accumulated damage by switching which channel receives the more severe cell-to-cell interference periodically. We apply DVA to this alternating-write-first approach with distinct scaling factors for the even-cell channel and the odd-cell channel, and use a joint DVA algorithm to adjust the two factors. The mutual information of the two channels will reach the predefined target together after each iteration.

Figure 2.6: Scaling factors generated by DVA with ideal channel information. (Result corresponds to Fig. 2.4 and 2.5. Ground truth model is Model 2. Channel parameters are listed in Sec. 2.10. The starting value of  $\alpha$  is 0.37.)

This approach equalizes the accumulated voltage  $V_{acc}$  of even-cell and odd-cell channel, and narrows the difference of the two channels' characteristics. Fig. 2.5 shows that with this approach the DVA algorithm can improve the lifetime of even cells by 68.5% from 2136 P/E cycles to 3600 P/E cycles and odd cells by 40.7% from 2517 P/E cycles to 3542 P/E cycles for the channel defined by the parameters in Sec. 2.10. Fig. 2.6 shows the scale factor  $\alpha$ used for even and odd cells as the red and blue curves respectively.

If the overall lifetime is defined as the number of P/E cycles until the mutual information of either channel crosses below the 1.945 bits target, joint DVA with the alternating-writefirst approach extends the lifetime by 65.8% from 2136 P/E cycles to 3542 P/E cycles. It may seem surprising that the overall lifetime is improved by 65.8% when the lifetime of odd cells only improves by 40.7%, but the odd cells were lasting longer than the even cells to begin with so that the overall lifetime improvement is primarily driven by the improvement in the even cell lifetime.

Recall that the single DVA targeting even-cell channel extends the lifetime by 65.7% from 2136 P/E cycles to 3540 P/E cycles, so that the joint DVA did not improve lifetime significantly more than the simpler single DVA process for this channel model. When the strength factor of cell-to-cell interference *s* increases, the average distortion of the interference for even-cell and odd-cell channels will rise, and the performance gain brought by the joint DVA approach will be more significant. For the remainder of this chapter, the joint DVA with the alternating-write-first approach or its approximations will be used to implement DVA when the channel model in the simulation is Model 2, which includes cell-to-cell interference.

#### 2.4 Channel Parameter Estimation

In order to dynamically allocate intended thresholds in a real system, the channel characteristics must be determined dynamically as they evolve. Channel estimation can be achieved by estimating the channel parameters in a channel model assumption. In [30], the authors demonstrate that accurate channel estimation can be achieved with limited computational complexity using multi-modal Gaussian channel model assumption and least squares algorithms.

Using both the channel model and the parameter degradation model, the channel characteristics after a specific number of P/E cycles can be predicted for a specified retention time. However, the exact channel model and parameter degradation model need to be known in advance to enable this approach. When considering on-the-fly scenarios, we may also want to use actual measurements from the working device to determine the channel parameters without making detailed assumptions about the parameter degradation model or perhaps even the channel model itself.

In practical scenarios, empirical histograms of the threshold voltage can be measured with multiple read operations. Combined with the knowledge of the read reference voltages used in the measurements, the empirical distributions provide enough information about the ground truth channel (voltage) distribution. For a given channel model, this measured histogram can be used to estimate the model parameters using a least squares algorithm. This approach does not require the channel parameter degradation model.

In both [2] and [30], the channel model assumptions are constructed to be as close to the ground truth model as possible. Later in this chapter, the idea of using the simple multimodal Gaussian model assumption, different from the ground truth model, is explored. For intended threshold voltage  $x_i, i \in \{1, \dots, 4\}$ , the conditional channel model assumption is

$$f_{Y|X}^{(\text{asm})}(y|x_i) = \frac{1}{\sigma_i \sqrt{2\pi}} e^{-\frac{(y-x_i-\mu_i)^2}{2\sigma_i^2}},$$

(2.18)

where  $\mu_i$  is the bias of the mean and  $\sigma_i$  is the standard deviation. Each intended threshold voltage level is treated as equally likely.

## 2.4.1 Channel Parameter Estimation Problem Formation

The channel parameter estimation is formulated as an optimization problem where a cost function is to be minimized by estimating the channel parameters. In [2], the channel model assumption is the same as the ground truth (both are Model 1), so the channel parameters to be estimated  $\mathcal{P} = [\lambda, \sigma_p, \sigma_e, \gamma_{\sigma_r}, \gamma_{\mu_r}]$  are the ones defined in the ground truth model. In Sec. 2.5 and later sections, the channel model assumption is a multi-modal Gaussian distribution, so the parameters to be estimated are the four biases and standard deviations of the four levels  $\mathcal{P} = [\mu_1, \mu_2, \mu_3, \mu_4, \sigma_1, \sigma_2, \sigma_3, \sigma_4]$ .

Regardless of the choice of the ground truth model and channel model assumption. the cost function is formulated as follows. Define  $[q_0, q_1, \ldots, q_M]$  as the boundaries of the M bins where  $q_0 = -\infty$ , and  $q_M = \infty$ . The expected number of cells in each bin can be computed as

$$\hat{N}_{bin,i} = \sum_{k=1}^{L} N_k P(q_i < y < q_{i+1} | x_k), \qquad (2.19)$$

where  $P(q_i < y < q_{i+1}|x_k) = \int_{q_i}^{q_{i+1}} f_{Y|X}^{(\text{asm})}(y|x_k) \, \mathrm{d}y$  denotes the probability of a measured thresh-

old falling in the *i*th bin when the intended threshold is  $x_k$  according to the channel model assumption. L = 4 is the number of intended threshold levels, and  $N_k$  is the number of cells in each level for the stored data. The cost function is defined as the normalized square Euclidean distance between the expected histogram induced by the estimated parameters and the reference histogram

$$C_M = \sum_{i=0}^{M-1} \left( \frac{N_{bin,i} - \hat{N}_{bin,i}}{N} \right)^2 \,, \tag{2.20}$$

where N is the total number of cells measured, and  $N_{bin,i}$  is the *i*th bin's cell count in the reference histogram. The gradient of the cost function is defined as

$$\nabla \boldsymbol{C}_{M}(\boldsymbol{\mathcal{P}}) = 2 \cdot (\boldsymbol{J}_{\boldsymbol{G}_{M}}(\boldsymbol{\mathcal{P}}))^{T} \cdot \boldsymbol{G}_{M}(\boldsymbol{\mathcal{P}}), \qquad (2.21)$$

where  $J_{G_M}(\mathcal{P})$  is the Jacobian matrix of the normalized difference vector  $G_M$  between the estimated histogram and the measured histogram.

#### 2.4.2 Least Squares Algorithms

Least squares algorithms have been widely used to fit a parameterized model to a data set. Three algorithms are examined in the following discussion.

#### Gradient Descent (GD)

GD minimizes the cost function by refining initial estimation of the parameters based on a linear approximation. In each iteration, the estimation is renewed by a step vector following the gradient of the cost function.

Algorithm 1 Gradient Descent Algorithm

1: Initialize step size  $\beta$  and  $\mathcal{P} = \mathcal{P}^{(0)}$ 2: while  $\|\mathcal{P}^{(k+1)} - \mathcal{P}^{(k)}\| > \eta$  and k < MaxIteration do 3: Compute  $J_{G_M}(\mathcal{P}^{(k)})$  and  $G_M(\mathcal{P}^{(k)})$ 4: Compute  $\nabla C_M(\mathcal{P}^{(k)}) = 2 \cdot (J_{G_M}(\mathcal{P}^{(k)})^T \cdot G_M(\mathcal{P}^{(k)})$ 5:  $\mathcal{P}^{(k+1)} = \mathcal{P}^{(k)} - \beta \cdot \nabla C_M(\mathcal{P}^{(k)})$ 6: k = k + 17: end while

#### Gauss-Newton (GN)

A quadratic model is employed to provide more accurate approximations of the cost function. The iterative relation can be represented as

$$\boldsymbol{\mathcal{P}}^{(k+1)} = \boldsymbol{\mathcal{P}}^{(k)} - (\boldsymbol{J}_{\boldsymbol{G}_{M}}^{T} \boldsymbol{J}_{\boldsymbol{G}_{M}})^{-1} \boldsymbol{J}_{\boldsymbol{G}_{M}}^{T} \boldsymbol{G} = \boldsymbol{J}_{\boldsymbol{G}_{M}}^{+} \boldsymbol{G} , \qquad (2.22)$$

where  $J_{G_M}^+$  is the pseudo-inverse of  $J_{G_M}$ . Gauss-Newton algorithm can then be formulated as follows:

Algorithm 2 Gauss-Newton Algorithm 1: Initialize  $\mathcal{P} = \mathcal{P}^{(0)}$ 2: while  $\|\mathcal{P}^{(k+1)} - \mathcal{P}^{(k)}\| > \eta$  and k < MaxIteration do 3: Compute  $J_{G_M}(\mathcal{P}^{(k)})$  and  $G_M(\mathcal{P}^{(k)})$ 4:  $\mathcal{P}^{(k+1)} = \mathcal{P}^{(k)} - (J_{G_M}(\mathcal{P}^{(k)}))^+ \cdot G_M(\mathcal{P}^{(k)})$ 5: k = k + 16: end while

#### Levenberg-Marquardt (LM) [50]

By combining GD and GN, LM possesses the advantages of both algorithms. The update vector  $\boldsymbol{\delta}_{\mathcal{P}}$  is calculated by solving  $(\boldsymbol{J}_{G_M}^T \boldsymbol{J}_{G_M} + \beta \cdot \operatorname{diag}((\boldsymbol{J}_{G_M})^T \boldsymbol{J}_{G_M}))\boldsymbol{\delta}_{\mathcal{P}} = \boldsymbol{J}_{G_M}^T \boldsymbol{G}$  where  $\beta$  acts as a weight to combine the two algorithms.

In [2], we studied the performance of the three algorithms with the ground truth model and the channel model assumption both to be Model 1. In this case, the channel parameters need to be estimated are  $\mathcal{P} = [\lambda, \sigma_p, \sigma_e, \gamma_{\sigma_r}, \gamma_{\mu_r}]$  as is defined in Sec. 2.2. Fig. 2.7 compares

Algorithm 3 Levenberg-Marquardt Algorithm

1: Initialize  $\beta, v, \mathcal{P} = \mathcal{P}^{(0)}$  and UpdateFlag = 12: while  $\|\mathcal{P}^{(k+1)} - \mathcal{P}^{(k)}\| > \eta$  and k < MaxIteration do if UpdateFlag = 1 then 3: Compute  $\widetilde{J}_{G_M}(\mathcal{P}^{(k)})$  and  $G_M(\mathcal{P}^{(k)})$ 4: end if 5:Solve  $((\boldsymbol{J}_{\boldsymbol{G}_{M}})^{T}\boldsymbol{J}_{\boldsymbol{G}_{M}} + \beta \cdot diag((\boldsymbol{J}_{\boldsymbol{G}_{M}})^{T}\boldsymbol{J}_{\boldsymbol{G}_{M}}))\boldsymbol{\delta}_{\boldsymbol{\mathcal{P}}} = (\boldsymbol{J}_{\boldsymbol{G}_{M}})^{T}\boldsymbol{G}_{M}$ Compute  $\boldsymbol{J}_{\boldsymbol{G}_{M}}(\boldsymbol{\mathcal{P}}^{(k)})$  and  $\boldsymbol{G}_{M}(\boldsymbol{\mathcal{P}}^{(k)})$ 6: 7:  $\mathcal{P}_{temporary} = \mathcal{P} - \delta_{\mathcal{P}}$ if  $\sum (err(\mathcal{P}))^2 > \sum (err(\mathcal{P}_{temporary}))^2$  then 8: 9: UpdateFlag = 110:  $\beta = \beta \cdot v$ 11:  $\mathcal{P} = \mathcal{P}_{temporary}$ 12: else 13:UpdateFlag = 014:  $\beta = \beta/v$ 15:end if 16:17:k = k + 118: end while

Figure 2.7: Estimation result versus ground truth for  $\gamma_{\mu_r}$  using 10-bin equal-probability histogram.

| No. of Reads | GD | GN | LM |

|--------------|----|----|----|

| 6            | 0  | 1  | 12 |

| 9            | 0  | 3  | 13 |

| 12           | 0  | 4  | 11 |

Table 2.1: Converge counts of least square algorithms (over 14 cases).

the estimating results of  $\gamma_{\mu_r}$  with the ground truth, where the estimation algorithms employ 10-bin equal-probability histograms (will be defined in Sec. 2.4.3) as input. The simulations are conducted over 14 different P/E cycle conditions. The LM algorithm performs significantly better than GD and GN in terms of both the estimation accuracy and the ability to adapt to different channel conditions.