# UC Berkeley UC Berkeley Electronic Theses and Dissertations

#### Title

A Modular Design Flow for NoC-embedded FPGAs

#### Permalink

https://escholarship.org/uc/item/6zg505rh

#### Author

Nguyen, Tan Quoc Duy

# **Publication Date**

2023

Peer reviewed|Thesis/dissertation

A Modular Design Flow for NoC-embedded FPGAs

By

Tan Quoc Duy Nguyen

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy

$\mathrm{in}$

Engineering – Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor John Wawrzynek, Chair Professor James Demmel Professor Sophia Shao Dr. Stephen Neuendorffer

Fall 2023

A Modular Design Flow for NoC-embedded FPGAs

Copyright 2023 by Tan Quoc Duy Nguyen

#### Abstract

#### A Modular Design Flow for NoC-embedded FPGAs

by

#### Tan Quoc Duy Nguyen

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor John Wawrzynek, Chair

With the increasing growth of complexity and heterogeneity of modern FPGA fabrics, the conventional digital design flow relying on the standard vendor tools, from synthesis to implementation, has become more arduous than ever. This leads to an inordinate turn-around time which severely impacts the productivity of application developers in their quest to explore the design space. We propose an open-source tool flow built upon three principles: modularity, composability, and reusability to address the FPGA tooling productivity issue. Our tool flow features the design and implementation of Spatially Distributed Ensemble of Sockets (SPADES). SPADES modularizes an application into a parallel system of socket engines interconnected by a Network-on-chip. Each socket contains a fixed and reusable component for control and communication in addition to a custom partition tailored to specific application computation and memory demands. SPADES also presents a customized backend tool that allows flexible and rapid composition of the socket physical implementations to generate a complete design. The results demonstrate that SPADES is 7.1x faster on average by reducing hours of compile time to minutes, while achieving comparable system-level performance when compared to a standard vendor tool for a set of benchmarks targeting a state-of-the-art FPGA architecture.

# Contents

| Co            | onten | ts                                         | i             |

|---------------|-------|--------------------------------------------|---------------|

| Li            | st of | Figures                                    | iv            |

| $\mathbf{Li}$ | st of | Tables                                     | ii            |

| 1             |       | oduction                                   | $\frac{1}{2}$ |

|               | 1.1   | Contribution                               | Ζ             |

| <b>2</b>      | Bac   | ground and Related work                    | <b>5</b>      |

|               | 2.1   | FPGA Architecture                          | 5             |

|               | 2.2   | FPGA Tooling                               | 7             |

|               |       | 2.2.1 Synthesis and Implementation         | 7             |

|               |       | 2.2.2 High-level Synthesis                 | 9             |

|               | 2.3   | Embedding NoC on FPGAs 1                   | 10            |

|               |       | 2.3.1 Academic Perspectives                | 10            |

|               |       | 2.3.2 Commercial Architectures             | 1             |

|               | 2.4   | Overlays                                   | 12            |

|               | 2.5   | Separate Compilation and Task Partitioning | 13            |

| 3             | From  | n SPADES to Socket 1                       | .5            |

|               | 3.1   | SPADES execution model                     | 15            |

|               | 3.2   | SPADES Realization on Programmable Logic   | 17            |

|               | 3.3   | Socket Microarchitecture Design            | 18            |

|               |       | e e e e e e e e e e e e e e e e e e e      | 18            |

|               |       | 3.3.1.1 AXI Logic                          | 18            |

|               |       | 3.3.1.2 DMA Logic                          | 20            |

|               |       | 3.3.1.3 Load Store Unit                    | 23            |

|               |       | $3.3.1.4$ Controller $\ldots$ $2$          | 27            |

|               |       | 3.3.2 Socket Custom Logic                  | 29            |

|               |       |                                            | 32            |

|               |       | 3.3.4 Multi-clock domains                  | 34            |

ii

| 4        | Socket Physical Implementation                                                                                                                                     | 35        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|          | 4.1 Socket Floorplanning                                                                                                                                           | 35        |

|          | 4.1.1 Routing conflicts                                                                                                                                            | 36        |

|          |                                                                                                                                                                    | 37        |

|          | 1                                                                                                                                                                  | 38        |

|          | 1                                                                                                                                                                  | 39        |

|          | 4.3 Static Logic Region                                                                                                                                            | 42        |

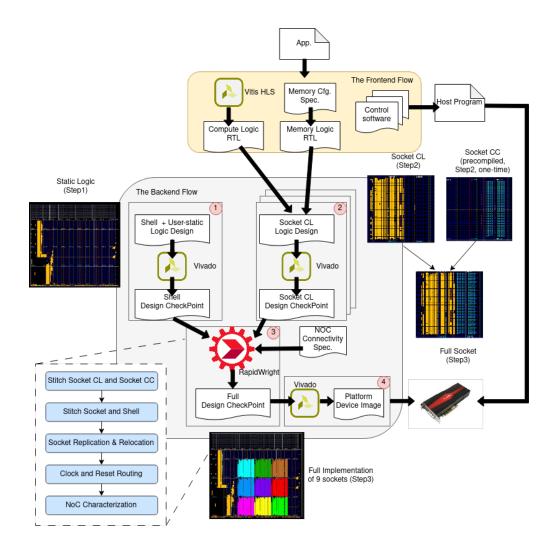

| <b>5</b> | The Backend Flow                                                                                                                                                   | 44        |

|          | 5.1 Static Logic Compilation                                                                                                                                       | 44        |

|          |                                                                                                                                                                    | 47        |

|          | 5.2.1 Socket CC Compilation $\ldots \ldots \ldots$ | 47        |

|          |                                                                                                                                                                    | 49        |

|          | 0                                                                                                                                                                  | 50        |

|          | 0                                                                                                                                                                  | 51        |

|          | v                                                                                                                                                                  | 53        |

|          | 5.4 Bitstream Generation                                                                                                                                           | 59        |

| 6        | The Frontend Flow                                                                                                                                                  | 61        |

|          | 6.1 Design Principles                                                                                                                                              | 61        |

|          |                                                                                                                                                                    | 64        |

|          | 0                                                                                                                                                                  | 64        |

|          | 6.2.2 Optimizations                                                                                                                                                | 71        |

| <b>7</b> | Evaluation                                                                                                                                                         | <b>74</b> |

|          | 7.1 Experimental Setup and Benchmarks                                                                                                                              | 74        |

|          | 7.2 Compile Time of the Full Design                                                                                                                                | 75        |

|          | J I                                                                                                                                                                | 77        |

|          |                                                                                                                                                                    | 78        |

|          |                                                                                                                                                                    | 79        |

|          | •                                                                                                                                                                  | 81        |

|          |                                                                                                                                                                    | 83        |

|          |                                                                                                                                                                    | 84        |

|          |                                                                                                                                                                    | 85        |

|          | 7.7 Mapping complex applications                                                                                                                                   | 87        |

| 8        | Conclusions                                                                                                                                                        | 91        |

|          | 8.1 Concluding Remarks                                                                                                                                             | 91        |

|          | 1                                                                                                                                                                  | 91        |

|          | 8.3 Reflections and Lessons Learned                                                                                                                                | 94        |

|          |                                                                                                                                                                    |           |

## Bibliography

| $\mathbf{A}$ | A Controller Software |                 | 107 |

|--------------|-----------------------|-----------------|-----|

|              | A.1                   | Matrix Multiply | 107 |

# List of Figures

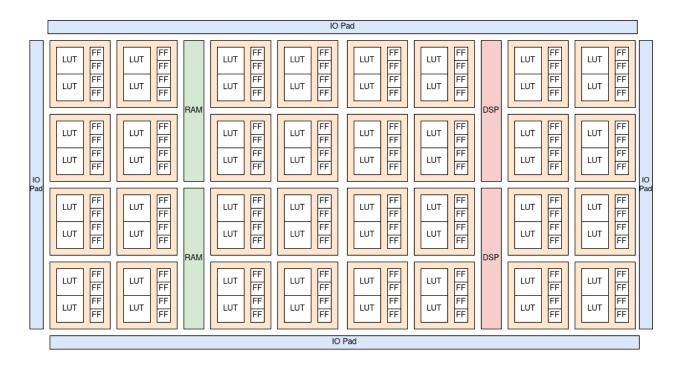

| 2.1          | A hypothetical tile-based, columnar FPGA architecture of 4x8 Configurable Logic<br>Blocks (CLB). Each CLB consists of 2 LUTs and 4 FFs. There is a column of<br>on-chip RAM blocks and another DSP slice mixing between. At the rear are the<br>IO pads for interfacing with IO devices. Not shown in this figure is the intra-site<br>routing resource within a tile, the inter-site routing among the tiles, as well as |        |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

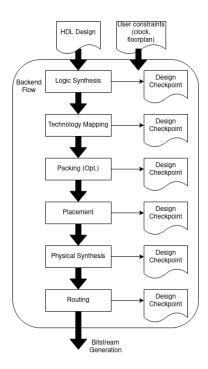

| 2.2          | the clocking network                                                                                                                                                                                                                                                                                                                                                                                                      | 6<br>8 |

|              | of the step                                                                                                                                                                                                                                                                                                                                                                                                               | 0      |

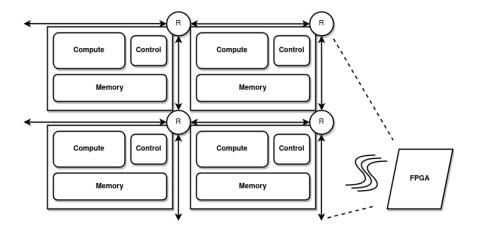

| $3.1 \\ 3.2$ | SPADES featuring a parallel, distributed system of socket engines Each task of an application could be assigned to different groups of SPADES'                                                                                                                                                                                                                                                                            | 16     |

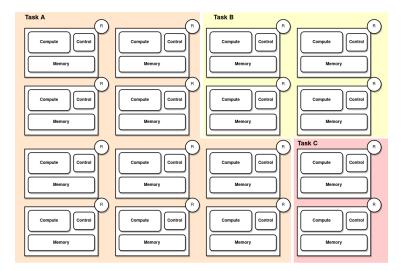

| 0.2          | sockets.                                                                                                                                                                                                                                                                                                                                                                                                                  | 16     |

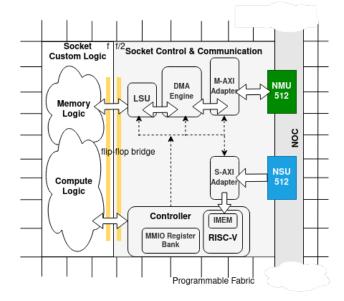

| 3.3          | Socket Microarchitecture. The thick arrows denote the direction of data flows                                                                                                                                                                                                                                                                                                                                             | 10     |

|              | (e.g., read/write, request/response). The thin black arrows denote control rela-<br>tionships.                                                                                                                                                                                                                                                                                                                            | 18     |

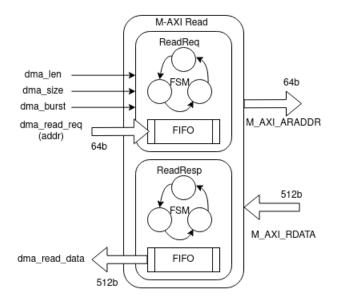

| 3.4          | Master AXI MM Read design. Separate FSMs control the request and response                                                                                                                                                                                                                                                                                                                                                 | 10     |

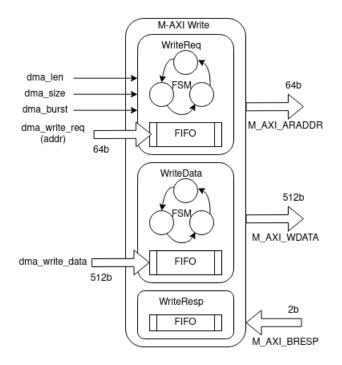

| 3.5          | logic. FIFOs are used to buffer incoming requests or responses                                                                                                                                                                                                                                                                                                                                                            | 20     |

|              | tional logic to handle the write response                                                                                                                                                                                                                                                                                                                                                                                 | 21     |

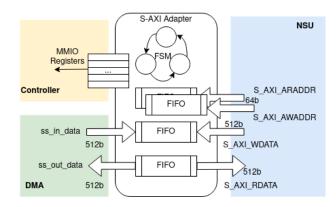

| 3.6          | Slave AXI MM block design. There is a single FSM that governs both read and write operations. FIFOs are used to buffer requests/responses via the NSU and data streams via the DMA. The Slave AXI adapter uses a set of MMIO registers                                                                                                                                                                                    |        |

|              | accessed by external masters via the NSU to interact with the controller                                                                                                                                                                                                                                                                                                                                                  | 21     |

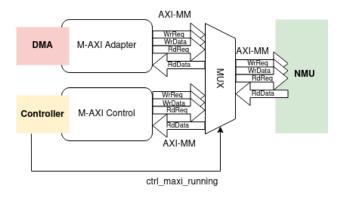

| 3.7          | MUXing Master AXI-MM between AXI Adapter and AXI Control. Only one                                                                                                                                                                                                                                                                                                                                                        | 41     |

| 0.1          | could interface with the NMU at a time. The selection is statically governed by                                                                                                                                                                                                                                                                                                                                           |        |

|              | the controller.                                                                                                                                                                                                                                                                                                                                                                                                           | 22     |

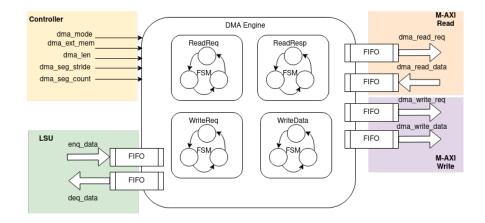

| 3.8          | DMA Engine Block diagram. There are 4 separate FSMs for each read/write request and response logic for an M-AXI Read and Write module. The DMA sends or receives a data stream from an LSU. It receives the configuration from                                                                                                                                                                                            |        |

|              | the controller.                                                                                                                                                                                                                                                                                                                                                                                                           | 22     |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                           |        |

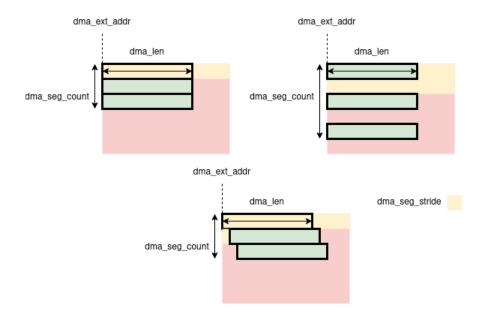

| 3.9        | Several examples of external memory layouts specified by different DMA config-<br>urations                                                                        | 23              |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

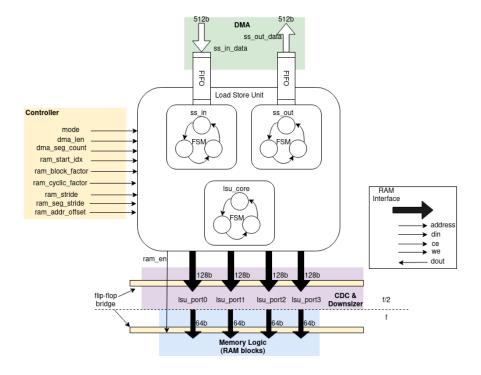

| 3.10       | LSU Block Diagram                                                                                                                                                 | 25              |

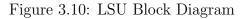

|            | Several examples of different (block, cyclic) settings                                                                                                            | $\overline{25}$ |

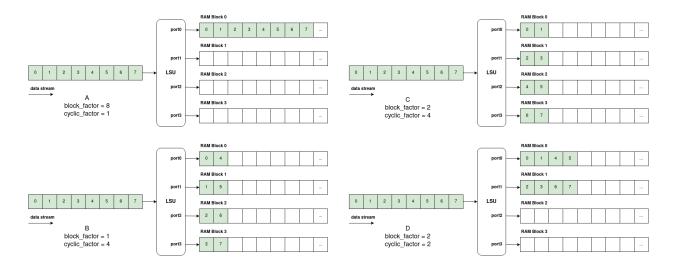

|            | Controller Block diagram                                                                                                                                          | $\overline{28}$ |

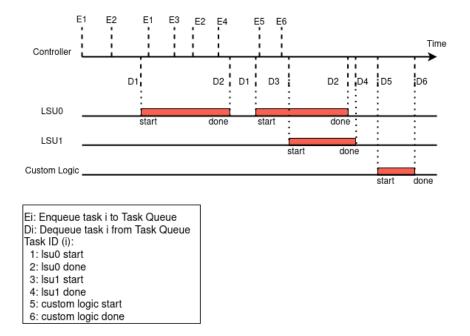

|            | Task Queue timing diagram                                                                                                                                         | 30              |

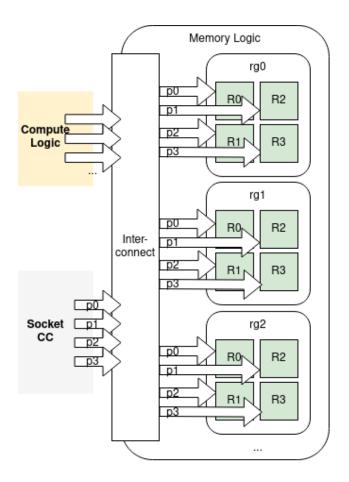

|            | Memory Logic organization                                                                                                                                         | 31              |

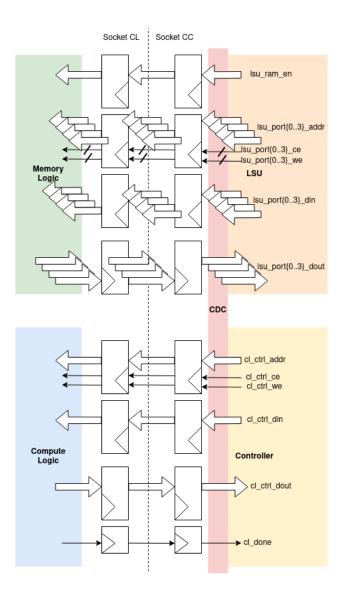

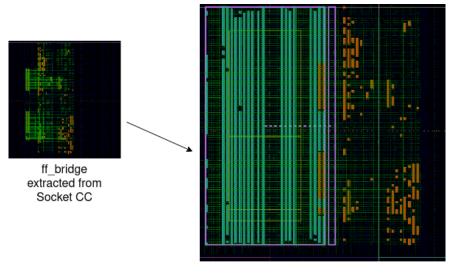

|            | Flip-flop bridge connecting the interfaces of Socket CC and Socket CL. CDC stands for "Clock-domain crossing". Socket CC operates at half the speed of Socket CL. | 33              |

|            |                                                                                                                                                                   | 00              |

| 4.1        | The target FPGA device contains multiple clock regions. Some clock regions have                                                                                   |                 |

|            | similar fabric structures.                                                                                                                                        | 36              |

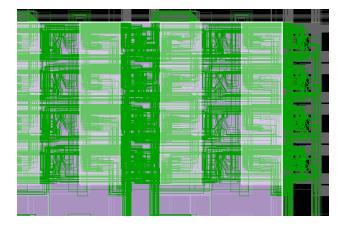

| 4.2        | Routing expansion issue. The routed nets (in green color) bleed over to the                                                                                       |                 |

|            | adjacent INT column outside the floorplan (white box)                                                                                                             | 37              |

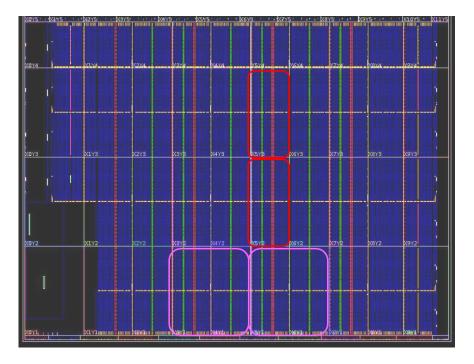

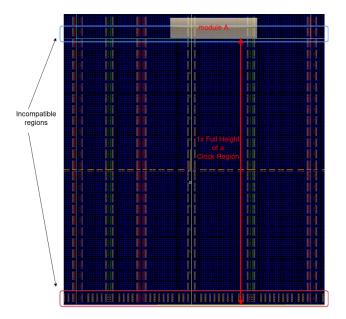

| 4.3        | Fabric irregularity. The bottom four rows (highlighted by the red oval box) do not                                                                                |                 |

|            | have any logic elements. It is incompatible with the region marked by the blue oval                                                                               |                 |

|            | box, since the latter does contain logic slices (such as LUTs and FFs). Therefore,                                                                                |                 |

|            | module $A$ whose implementation contains resources in that region could not be                                                                                    |                 |

|            | relocated vertically to the clock region below (by a distance of one clock region's                                                                               |                 |

|            | height) due to incompatible fabrics.                                                                                                                              | 38              |

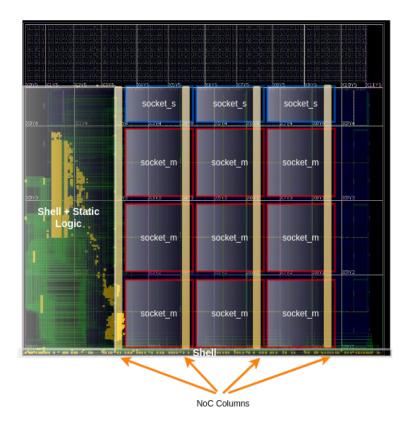

| 4.4        | SPADES floorplaning scheme. $socket_m$ denotes medium-sized socket, whereas $socket_s$ denotes small-sized socket. The leftmost NoC column is already used by     |                 |

|            | the shell and static logic. <i>socket_s</i> is roughly half the size of <i>socket_m.</i>                                                                          | 40              |

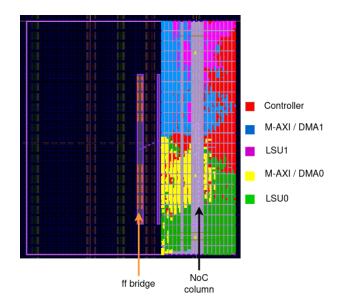

| 4.5        | Socket CC pre-implementation. There are two NMUs and one NSU in this im-                                                                                          |                 |

|            | plementation. The remaining logic of the PBlock is reserved for Socket CL netlist.                                                                                | 41              |

| 51         |                                                                                                                                                                   | 45              |

| 5.1        | The SPADES flow                                                                                                                                                   | 45              |

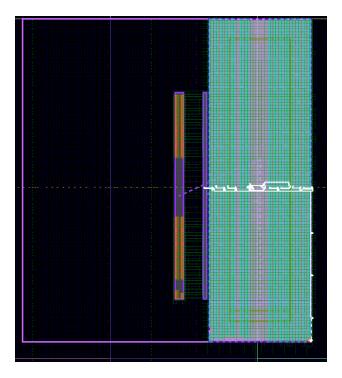

| 5.2<br>5.2 | Socket CC floorplan. FF Bridge cells are highlighted in orange.                                                                                                   | 49              |

| 5.3        | Socket CL floorplan. FF bridge cells are highlighted in orange. The cells outside                                                                                 | ۲1              |

| F 4        | of the floorplan are from Socket CC.                                                                                                                              | 51              |

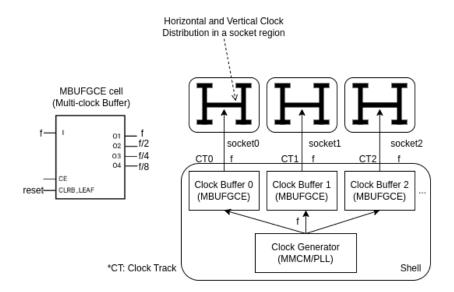

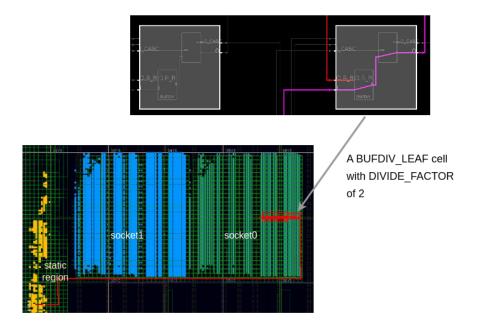

| 5.4        | Each socket owns a unique Clock track driven by a separate MBUFGCE clock                                                                                          |                 |

|            | buffer. Note that, although a socket uses two clock domains $(f \text{ and } f/2)$ , there                                                                        |                 |

|            | requires only a single physical clock net routed from a clock buffer. The frequency                                                                               |                 |

|            | division is achieved by the buffer division cells (BUFDIV_LEAF) located in the                                                                                    | EC              |

| E F        | horizontal clock distribution inside every socket region                                                                                                          | 56              |

| 5.5        | Routing of the reset signal (highlighted in red) originated from the static logic region to the reset ping of the BUEDIV LEAE colls in code to region. We exploit |                 |

|            | region to the reset pins of the BUFDIV_LEAF cells in socket0 region. We exploit                                                                                   | <del>ر</del> م  |

|            | the gap beneath the sockets (unused fabric regions) for fast routing                                                                                              | 57              |

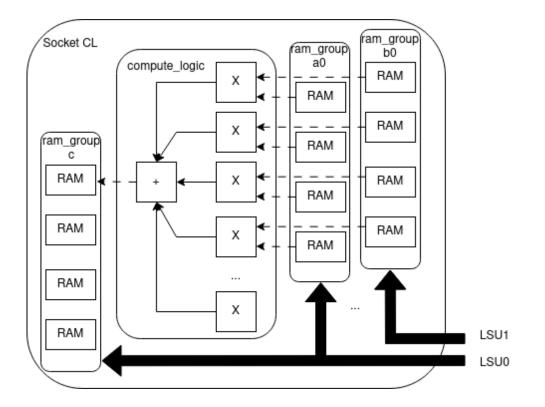

| 6.1 | Custom Logic design showing the dot product engine and connected RAM blocks.<br>The dash lines denote RAM read/write operations. The thin dash black lines<br>denote the datapath within the compute logic. The thick black lines denote the<br>LSU interfaces with the RAM groups. An LSU interface consists of 4 sets of |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | RAM interfaces, one for each RAM block within a group                                                                                                                                                                                                                                                                      | 67 |

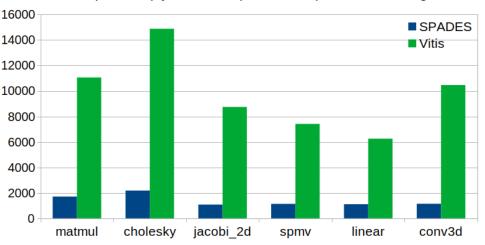

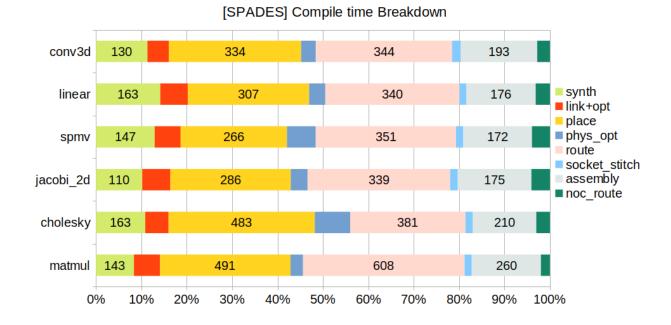

| 7.1 | Total Compile Time of a 9-socket design: SPADES vs. Vitis (lower is better)                                                                                                                                                                                                                                                | 76 |

| 7.2 | A breakdown showing the task runtime percentages of the overall SPADES com-<br>pile time. Time-consuming tasks are annotated with their runtimes in seconds.                                                                                                                                                               | 77 |

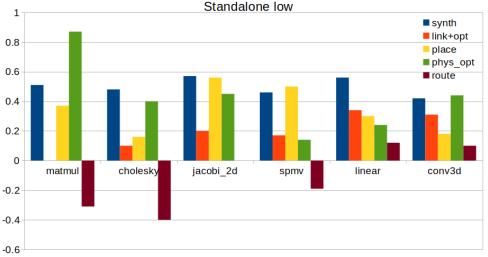

| 7.3 | Runtime improvement of steps from Pre-compiled flow over Standalone flow for a socket                                                                                                                                                                                                                                      | 79 |

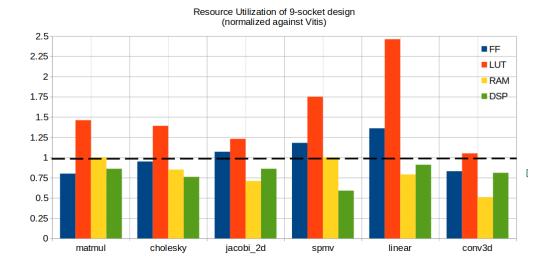

| 7.4 | Resource utilization of a 9-socket design (SPADES results normalized against Vitis). Lower is better.                                                                                                                                                                                                                      | 81 |

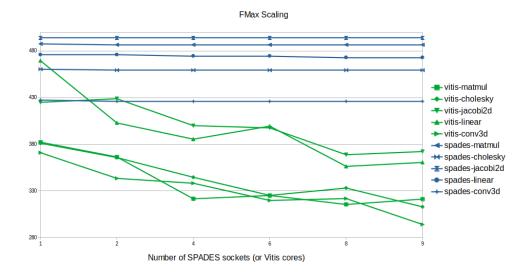

| 7.5 | Maximum Achievable Frequency scaling concerning the number of sockets (cores) in the design                                                                                                                                                                                                                                | 83 |

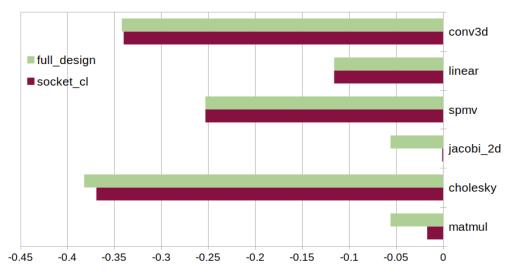

| 7.6 | Worst-case negative slack: Socket CL vs. Full design                                                                                                                                                                                                                                                                       | 84 |

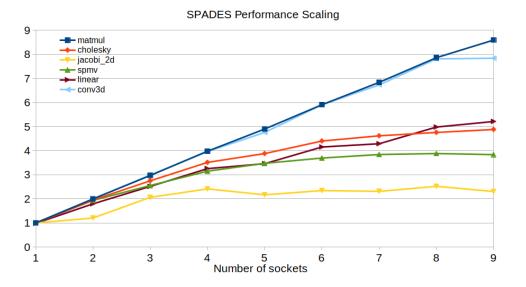

| 7.7 | SPADES System Performance scaling concerning the number of sockets in the                                                                                                                                                                                                                                                  |    |

|     | design $\ldots$                                                                                                                                                                                                                           | 87 |

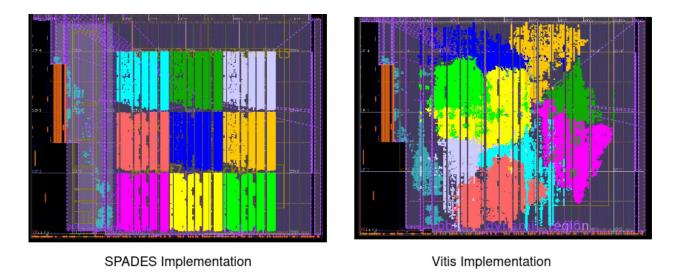

| 7.8 | SPADES and Vitis Implementations for Configuration $\{4x \ conv3d, 5x \ linear\}$ .                                                                                                                                                                                                                                        | 88 |

|     |                                                                                                                                                                                                                                                                                                                            |    |

# List of Tables

| 3.1  |                                                                                      | 23 |

|------|--------------------------------------------------------------------------------------|----|

| 3.2  | LSU Registers                                                                        | 24 |

| 4.1  | Socket Area                                                                          | 42 |

| 7.1  | Benchmarks                                                                           | 75 |

| 7.2  | Socket Compile time of Pre-compiled flow vs. Standalone flow per socket              | 79 |

| 7.3  | Socket QoR Comparison (Pre-compiled flow / Standalone flow)                          | 80 |

| 7.4  | FMax of the Full design                                                              | 82 |

| 7.5  | WNS results and Routing runtimes for clock and reset signals in different approaches | 85 |

| 7.6  | Performance Comparison (SPADES / Vitis / SPADEStd12)                                 | 86 |

| 7.7  | Small CNN layer specification                                                        | 89 |

| 7.8  | Performance Comparison                                                               | 89 |

| 7.9  | FMax Comparison                                                                      | 89 |

| 7.10 | Compile time Comparison                                                              | 90 |

# Listings

| 6.1 | Tiled Matrix Multiply                              | 65  |

|-----|----------------------------------------------------|-----|

| 6.2 | Task-based Matrix Multiply                         | 66  |

| 6.3 | DMA/LSU configurations for reading C               | 68  |

| 6.4 | DMA/LSU configurations for reading A and B         | 68  |

| 6.5 | Example of overlapping multiple DMA operations     | 69  |

| 6.6 | DMA/LSU configurations for writing C               | 70  |

| 6.7 | CL configuration                                   | 71  |

| 6.8 | Closing code                                       | 71  |

| A.1 | Optimized controller software for benchmark matmul | 107 |

#### Acknowledgments

Graduate school is an arduous journey. Now that there is light at the end of the tunnel, thinking back, I would not have made it to this point without the support of many people.

First, I would like to thank my former colleagues and supervisors from the hardware group at Illinois Research Center in Singapore (ADSC): Kyle Rupnow, Swathi Gurumani, Liwei Yang, Yao Chen, and Professor Deming Chen (UIUC). I gained valuable research experience and skills thanks to the time that I worked with them. The experience that I had earned at ADSC continued to help me throughout my graduate study.

I would also like to thank my advisor, John Wawrzynek, for bringing me to Berkeley to join his research group, as well as his guidance and patience over the years. I was frustrated with myself in the first few years of my study for not meeting my own expectations on the progress of my research. Yet, John was very encouraging and tolerating. John gave me ample freedom to explore the research topics that I found most interesting. At the same time, he also put effort into making himself available whenever I would like to reach out for his advice. He took great care in ensuring that we were feeling comfortable and inclusive in our group. There are two things that I always try to learn from John. First is the ability to ask follow-up questions to guide the discussions and conversations. Second is managing busy schedules, such as teaching large classes while maintaining an optimistic outlook and enjoying life. Thank you, John.

The other person who had the most significant impact on my graduate study is Stephen Neuendorffer. Steve was my manager during my internships at Xilinx Research Labs. Steve was generous with his time by agreeing to be on my Qualifying and Dissertation committee member and advised my dissertation topic. Steve gave me plenty of advice — be it research, career, or life. When I felt unsure if I should pick a particular research problem; "If you do not do anything, you are not going to make any progress"; what he had said then still strikes me today. In retrospect, that was one of the most helpful advice I have gotten during my graduate school. Thank you, Steve.

I would like to thank Professor James Demmel and Professor Sophia Shao for serving on my Qualifying and Dissertation committee. Thank you for offering your advice on my research at the Qual, proofreading my thesis, and giving constructive feedback.

I would like to thank my industrial collaborators and researchers, in particular, Zachary Blair and Dr. Chris Lavin from AMD/Xilinx. Zac initiated the socket idea when I worked with him as an intern and continued to give me helpful advice related to the Vivado tool throughout this project. Chris was always prompt and active in giving technical assistance of the RapidWright software, or when I needed some feature requests. This work would not have been possible without the RapidWright developers and contributors. I also thank Dr. Jonathan Greene, Dr. Alan Mischenko, and Dr. Eddie Hung for giving feedback on our research as well as sharing their projects during our group's FPGA seminars.

I am grateful for the VCK5000 card donation from the AMD Xilinx University Program. This work was supported in part by the CONIX Research Center, one of six centers in JUMP, a Semiconductor Research Program (SRC) sponsored by DARPA. I also acknowledge the gift funding from AMD/Xilinx.

I thank the staff at Berkeley Wireless Research Center (BWRC) for providing a great facility and environment so that we can do our work more productively. Special thanks to Brian Richards for the software tool support and maintenance of the computing infrastructure. I also acknowledge the administrative staff Candy, Mikaela, and Shirley for helping us navigate through complex paperwork and admin procedure to meet the program deadlines.

I thank my fellow students in the research group from whom I have learned so much. I am fortunate to be a part of a group of bright and hardworking individuals: James Martin, Jenny Huang, Chris Yarp, Arya Reais-Parsi, Josh Kang, Yukio Miyasaka. I also thank them for giving their opinions and suggestions on improving this work. Special acknowledgments to Chris and Arya. Chris was my BWRC buddy who kept me in good company whenever I worked in the office. Arya is the most gregarious person I have ever known. Arya was always generous in hosting us at his house for various social events of our group.

I thank my longtime high school close friends, Thanh Dat and Quoc Vu, for staying in touch despite the distance and each being busy with his own life. Vu and I made long phone calls every end of the year to check on each other's updates and give encouragement. Dat and I occasionally had some fun hangouts. They made me aware that there is a life outside of graduate school. I hope our friendship continues to go strong.

Lastly, I would like to thank my parents in Vietnam. When I decided to attend graduate school in the US, Mom was worried because of the rigor of the program and the long distance from home. Yet they still keep supporting and sending love in every possible way they can over the years. I could endure many lonely moments during my graduate study by knowing that I have great emotional comfort to lean on back home. Looking back, I have always earned what I wished for from my parents. I cannot thank them enough. This dissertation is dedicated to you, Mom and Dad. We made it.

# Chapter 1 Introduction

With the end of Dennard Scaling [23] and the slowing down of Moore's law [53], we are entering a new era of domain-specific accelerators to unlock higher performance and better energy efficiency than the traditional multi-processor systems. Among many different accelerator types, Field Programmable Gate Arrays (FPGAs) offer a compelling solution thanks to their reconfigurability and spatial parallelism nature. FPGAs have been shown to outperform general-purpose processors and Graphic Processing Units (GPGPUs) in certain applications. Thus, they have been increasingly gaining their footing in many applications ranging from data centers in the cloud to embedded devices on the edge. For instance, Microsoft uses FPGAs to accelerate their web search engine [12], and deep learning workloads [24]. They are also being used for signal processing at wireless base stations [51], and computer vision pipelines in the automotive industry [7]. Besides application acceleration, FPGAs are well-suited for Application-Specific Integrated Circuits (ASICs) prototyping and emulation before chip tapeouts [10].

To cope with the growing computation and communication demands, FPGA vendors have been augmenting their devices with millions of logic elements in addition to a multitude of heterogeneous hardened blocks [82, 35]. This further exacerbates the longstanding, pathological FPGA tooling issues which severely affects their usability and inhibits their accessibility and applicability outside the niche community of hardware design experts.

To begin with, programming an FPGA is not straightforward. The programming model is Register Transfer Level (RTL) which captures bits and cycles. The act of programming an FPGA entails describing a hardware circuit (composed of logic gates and memory blocks) and its behavioral cycle-by-cycle in a Hardware Description Language (HDL) such as Verilog/VHDL. It is a tedious and error-prone process. High-level Synthesis [19] aims to bridge the gap between software programmers and low-level RTL designs by introducing a parallel software model that embraces procedural languages such as C/C++, thus improving programmers' productivity [43].

The next hurdle is vendor tools may consume hours or days to generate a bitstream of a hardware implementation, especially for some large and complex designs. If the implementation failed to satisfy user-defined constraints, such as desirable operating frequency, area, or functionality, the whole development cycle would repeat, further hurting the productivity. Therefore, we think that the FPGA compilation time is among, if not the most, important problem to be addressed as we deal with the continuing trend of future FPGA device and design scaling.

The primary challenge is how we could improve the compile time while minimizing the impact on Quality-of-Result (QoR). The QoR is primarily concerned with two metrics: area utilization and maximum achievable frequency. The former measures how much on-chip resource consumed by an implementation. The latter informs the maximum clock speed that the implementation can operate. To mitigate the compile time issue, one could virtualize an FPGA with overlays. An overlay is typically a pre-defined architectural RTL design that gets implemented on an FPGA. The implementation usually does not change throughout running one or several applications. The overlay serves as a virtualization layer so that users do not need to interact with the FPGA directly. The overlay technique raises the abstraction level by allowing users to program an FPGA using a higher-level programming language than HDLs in tandem with a software-like compilation experience, thereby improving overall productivity. In addition, the overlay approach eschews the tooling problem entirely, since one usually does not need to modify the underlying overlay implementation. However, the key limitation of the overlay approach is that it yields sub-optimal QoR in comparison to custom hardware design. Therefore, overlays are often designed for domain-specific classes of applications [17, 78, 62] to achieve high efficiency. General-purpose overlays, such as softcore CPUs often leads to poor performance due to low QoR. They are mainly used for housekeeping tasks such as control and monitoring that do not require significant processing power [79]. In some cases, they provide a starting point for newly adopters to leverage to reduce the barrier to FPGA usability, and then a more custom solution could be built over time if needed.

In many applications, it is possible to modularize their design structures into smaller partitions. Some partitions, either within the same or from different applications, can share similar implementations. Unfortunately, the conventional vendor CAD flows fail to recognize such properties. A design is usually implemented in a top-down ("flat") manner, thus failing to take advantage of the design modularity to shorten the compile time either by parallel compilations of separate partitions or reusing existing compiled results of certain partitions. In some cases, a top-down implementation might not even yield the best QoR.

#### **1.1** Contribution

Drawing from the aforementioned observations, we think that modularity is the first-order important factor to improve the compile time. We start by defining a modular execution model, namely SPADES, that well-suited for different types of parallel applications, including data- and task-parallel. We then build our tool flow on top of this model. SPADES is an ensemble of sockets. The socket physical implementations could be dropped in and out of a design without incurring any recompilation, hence facilitating design composability. The sockets could also be reusable within one or different applications. All of these requirements could not have been accomplished without the support of a customized backend tooling and the architectural features of a target device.

In summary, our contributions are as follows. <sup>1</sup> <sup>2</sup>

- 1. We design and implement a novel tool flow for mapping parallel applications onto contemporary FPGAs. Our tool achieves fast compilation by promoting three primary ideas: modularity, composability, and reusability.

- 2. We discuss various design and implementation tradeoffs that influence compile time and QoR/performance. We present the principles of mapping an application to our tool flow in order to achieve high performance.

- 3. We evaluate the effectiveness of our tool flow in a multitude of aspects, such as compile time, QoR, and system-level performance. The experimental platform is the AMD Versal VCK5000 data center card from a state-of-the-art commercial FPGA architecture.

To the best of our knowledge, this is the first work in studying the compilation issue on the Versal architecture which features a novel hardened Network-on-chip. While some prior works are proposing and evaluating parallel or separate compilations to accelerate the compile time, our work is unique in adopting a holistic approach in co-developing the frontend and the backend flow following a unified model. We also exploit design reuse at multiple levels, as well as hardware/software partitioning techniques to further improve the compile time and QoR.

The rest of the dissertation is organized as follows.

- Chapter 2: We will review some key concepts that are relevant to this dissertation. We also discuss related work to this research.

- Chapter 3: We will provide the details of the SPADES execution model, and the micro-architectural design of a socket the basic building block of our model.

- Chapter 4: We will show how to go about implementing a socket on the target device. We discuss the tradeoffs of various implementation schemes that we have considered.

- Chapter 4: We will present the backend flow which compiles the sockets to the FPGA, as well as techniques for improving QoR and compile time.

- Chapter 5: We will give some insights on how an application is mapped in our flow.

- Chapter 6: We will cover the experimental results and discussion.

<sup>&</sup>lt;sup>1</sup>Our work has been published at [57].

<sup>&</sup>lt;sup>2</sup>Our work is open-source at github.com/nqdtan/spades

• Chapter 7: We will conclude the research with closing thoughts, lessons learned, and future work.

Throughout the remaining sections, we use the terms *design* and *implementation* to describe our tool flow at various stages. When referring to *Design optimizations*, they include microarchitectural-level optimizations. This occurs at the block level (e.g., in RTL form). This also concerns scheduling optimizations related to data movements and compute executions. On the other hand, *Implementation optimizations* cover optimizations on the physical netlists. Such optimizations involve floorplanning, placement, and routing that improve QoR.

# Chapter 2

# **Background and Related work**

## 2.1 FPGA Architecture

Figure 2.1 demonstrates an example of what an FPGA looks like. An FPGA contains a multitude of logic elements and storage elements. One example of a logic element is a lookup table (LUT). There are typically two types of LUTs: logical LUT and memory LUT. The former implements a K-input Boolean function with a K-input LUT, while the latter serves as a small memory block, often known as distributed RAM. The memory LUT is asynchronous-read, synchronous-write; a read operation occurs immediately, whereas a write operation incurs one clock cycle. One other FPGA logic element is carry chain slices for implementing arithmetic circuits using fast carry lookahead. To hold the states of a circuit, there are some primitive storage elements called flip-flops (FF), or registers. The number of logic elements ranges from a few hundred in embedded FPGAs with small form factors to millions in data center-grade FPGAs. The logic elements and FFs are organized into columns of clusters, or Configurable Logic Block (CLB). Within a CLB, there can be two logic slices (or sites). A slice may contain only memory LUTs or logical LUTs. There is a fixed number of LUTs and FFs as well as carry logic per slice. The numbers of LUTs and FFs within a logic block vary from one FPGA architecture generation to another [77, 80, 81], as well as from different FPGA vendors. We refer to the logic and storage primitives of a slice as Basic Element Logic (BEL). Within a slice, some routing wires and multiplexers enable the connections between the BELs; those are the intra-site routing. The CLBs are intersite routed by the Interconnect tiles (INT tile). There are a vast number of Programmable Interconnect Points (PIPs) in an INT tile for routing signals coming from the South, East, North, and West sides.

An FPGA is reconfigurable; this essentially means there is an underlying configuration circuitry. The circuitry configures LUTs, FFs, intra-routing within a site, and inter-routing among the sites based on the content of an input bitstream generated by an FPGA tool. One can reprogram an FPGA to perform different functionalities over time. Therefore, an FPGA can often be called a programmable fabric, or programmable logic (PL). The

Figure 2.1: A hypothetical tile-based, columnar FPGA architecture of 4x8 Configurable Logic Blocks (CLB). Each CLB consists of 2 LUTs and 4 FFs. There is a column of onchip RAM blocks and another DSP slice mixing between. At the rear are the IO pads for interfacing with IO devices. Not shown in this figure is the intra-site routing resource within a tile, the inter-site routing among the tiles, as well as the clocking network.

flexibility of FPGAs is the primary advantage over ASICs. For some applications whose requirements are rapidly evolving, an ASIC solution may quickly become obsolete, leading to higher engineering costs.

To improve the performance, FPGA vendors have been augmenting their fabrics with more heterogeneous hard blocks, such as Block RAM, Ultra RAM for dense on-chip storage, and DSP slices for supporting efficient multipliers and other math operations: those that would have cost numerous logic elements if they were implemented by LUTs and FFs. Some FPGA vendors offer application-specific hard blocks on the programmable fabric, such as Tensor blocks targeting Deep learning applications.

Another important resource of an FPGA device is I/O banks which are usually located at the edges of the device. Typical examples of I/O resources are PCIe interface, HDMI interface, Ethernet interface, external DRAM interface, etc. The IO banks offer interfaces to a wide variety of connected peripherals in a system. Therefore, this brings about a tremendous advantage of using FPGAs for IO computing at the edge rather than other programmable substrates such as CPUs, since FPGAs can directly process the data coming in and out of the IO banks. One of the notable features of an FPGA is partial reconfiguration [71]. Certain regions of the programmable fabric can be reconfigured at *runtime* while the rest remains intact. Therefore, the overall compile time could be significantly reduced if we know in advance which pieces of the implementation that are fixed, and which could be changed at runtime. Typically, an FPGA design consists of two parts. One is the shell design that offers system functionality, such as clock management and data transfers via PCIe IO. The other is a custom design that implements user-specific functionality for a target application. The shell design is usually invariant, hence it is reasonable to keep its implementation unchanged, and the FPGA could be partially reconfigured for the user logic only. Previous work demonstrated how to exploit this feature to time share an FPGA with a computer vision pipeline that could not be mapped entirely to the FPGA [56].

Recent strides in FPGA architecture introduce a hardened Network-on-chip (NoC) embedded directly on the programmable fabric as well as other connected subsystems, thus forming a complex System-on-chip platform(SoC). The NoC offers many advantages to FPGA designs and implementations, chief among those are mitigating long routing wires between distant modules, or between a module and an IO interface such as a DRAM Memory Controller.

## 2.2 FPGA Tooling

#### 2.2.1 Synthesis and Implementation

An FPGA backend flow typically consists of several phases as demonstrated in Figure 2.2. Firstly, a logic synthesis engine performs logic optimizations on an input HDL design. It then translates the optimized design to a representation that uses FPGA primitives (e.g., LUTs, FFs, BRAMs, etc.), a phase known as technology mapping. Next, the backend tool performs placement on the technology-mapped design to place the cells on the target FPGAs. A router then routes the placed design using the routing muxes and wires. The placer and router will try to optimize the design so that it can meet user-specified constraints on achievable maximum frequency, or area utilization. Therefore, the tool may carry out additional optimization steps before the placement and/or routing. Those usually involve physical synthesis optimizations that operate directly on the physical FPGA netlists. The last step is generating a bitstream from the final placed-and-routed implementation to configure the target FPGA.

Among the phases of the backend flow, placement, and routing usually dominate the overall compile time. Here, we refer to compile time as the time taken from an HDL input to a final implementation. If the user constraint is extremely tight, or if the input design is complex (in terms of the gate count), the tool will take longer to produce a solution. In particular, the tool may try replacing or rerouting the implementation several times to improve the QoR.

It is also worth noting that certain vendor tool may emit an output checkpoint at every

Figure 2.2: A Standard backend flow. It takes an HDL design and user constraints as input and produces a fully placed-and-routed implementation ready for bitstream generation. At each step, a design checkpoint could be generated to save the state of the step.

step of the compilation process. These design checkpoints save the states of the implementation at the corresponding steps. The checkpoints could be imported back into the design flow to continue with the subsequent steps. This is useful in cases where we would like to reuse the results of the previous steps for different explorations of the current step. Another scenario is that one could modify a checkpoint from a certain step, then import it to the design tool and invoke the next step. RapidWright [44] is a custom backend tool providing such capability. It can read a design checkpoint generated by the standard vendor tool, perform modifications on the netlist captured in the checkpoint, and write a new checkpoint. This flexibility allows users to add their own custom modifications, such as custom placer or router [47], and bypass certain steps in the design flow to reduce the compile time.

Finally, we note that there are several open-source FPGA tools besides the commercial vendor products such as AMD Vitis [5] or Intel Quartus [34]. Yosys & nextpnr [61] presents a fully open-source FPGA toolchain from synthesis to bitstream generation. The tool can be extended to support as many FPGA devices as possible by providing an FPGA architectural description file as input. Similarly, VTR [55] is an established open-source CAD framework for FPGA CAD-related research, including improving placement and routing algorithms, modeling new architecture, and so on. Previous work also studied the QoR gap between circuits generated by open-source tools versus vendors, and showed that the open-source

tools are catching up [31, 9] thanks to the novel optimizations of the open-source logic synthesis tool ABC [1].

#### 2.2.2 High-level Synthesis

An input to a Logic synthesis tool is normally in the form of a Hardware Description Language (HDL), such as Verilog/ VHDL. HDL adopts a Register Transfer Level (RTL) model in which there is a notion of time (clock cycle); all assignments happen at every clock cycle. In addition, HDL constructs are declarative in ways that are used to compose certain graphical structures such as logical circuits. They do not share the same control and data flow semantics with procedural languages. Therefore, programming HDL requires a different thinking. It is often a tedious and error-prone process, especially for software programmers who are not familiar with hardware design.

High-level Synthesis (HLS) aims to bridge the gap introduced by the RTL model [11, 70, 33]. It allows users to write a program in procedural code, such as C/C++, and compiles the program to RTL, thus improving FPGA accessibility to software programmers. In essence, an HLS compiler transforms an untimed representation to a timed representation that eventually produces a valid, functionally corrected circuit description. That means the generated circuit must give output values that match its software counterpart. There are typically three phases in an HLS compiler: resource allocation, scheduling, and resource binding [20]. The scheduler computes the places to insert pipelined registers to break the control-data flow graph of an input program into multiple states controlled by one or several Finite State Machines (FSMs). In addition, stateful variables are mapped to registers or memory blocks in RTL. The arithmetic and memory operations of the input program are also transformed into the corresponding operations in the RTL model. Expensive arithmetic operations such as large-bitwidth multipliers could get mapped to hard blocks such as DSP slices for resourcewise efficient implementation. An important factor to consider is the QoR of the generated circuit. Ideally, we would like the generated circuit, when being implemented on an FPGA. to meet a target clock frequency. Therefore, an HLS compiler also takes as input a user clock constraint. The clock constraint impacts the HLS scheduler in how it schedules the operations, and inserts pipelined registers. It builds an estimated timing model of various operations to ensure reasonable delay estimations when performing scheduling. For example, if there is a chain of operations whose total estimated delay exceeds the target timing, the compiler will place pipelined registers on the chain to break it into smaller paths. Different target input clock constraints lead to varying generated circuits by an HLS compiler.

Besides, for an HLS compiler to produce a highly-optimal circuit, an input program needs to follow several best HLS practices or HLS model. This is due to the use of procedural languages whose model is inherently sequential execution semantics. When coding an HLSbased program, a software designer should reason how the code gets compiled to some computational structures or datapaths. Thus, the designer is still expected to possess some familiarity with hardware design concepts. Nevertheless, the advantage of relying on an HLS model is that the designer does not need to be concerned with the *time* notion, or clock cycle-based behaviors as in the RTL model. In other words, the exact timing, or cycle of any operation is not a concern to a designer and is abstracted away in the HLS model, leading to a productivity boost.

The HLS approach attempts to address the programmability issue, which in turn ameliorates productivity. Yet the detachment of an HLS tool from the backend tool may impact the overall compile time and QoR. For example, the hierarchical information of the input program may be lost during the lowering to RTL form by HLS. In addition, HLS typically generates less optimal circuits in comparison to hand-designed RTL; it may incur additional resource usage or longer critical path delays. This is primarily because it relies on some delay estimations of certain operations that may not be accurate. Nonetheless, some studies demonstrated that HLS is catching up with hand-designed RTL [60], or enabling design space exploration for performance optimizations that would have been difficult to achieve with the RTL approach [87, 84]. HLS was also employed in designing complex applications such as video decoders or deep learning accelerators [49, 13, 83]. Some studies proposed alternative HLS input languages than C/C++ in terms of explicit parallel programming models [58], or productivity and popularity with software programmers [30]. [14] took a different approach by proposing high-level synthesis on an application binary program that aims to bypass the user programming step completely. In most cases, however, the prior works usually rely on existing compiler frameworks such as LLVM [65], to perform scalar and loop optimizations on an input program (the frontend phase) before invoking HLS-specific transformations.

Traditional HLS tools that employ static schedulers suffer from generating sub-optimal circuits for applications that exhibit runtime dependencies. Since they cannot resolve the dependencies at compile time, they resort to conservative scheduling solutions. Dynamically-scheduled HLS aims to address such inefficiencies by introducing several latency-insensitive, dataflow constructs for resolving the dependencies at runtime with extra area overhead [39].

## 2.3 Embedding NoC on FPGAs

#### 2.3.1 Academic Perspectives

Traditional routing network on a programmable fabric contains wires and switchboxes. Inside a switchbox, there are PIPs for configuring the wire connections to form longer wires to route from a source to one or multiple sinks. The routing is determined by the tool (router), and implemented at compile time (loading a bitstream) using a circuit-switch routing style. A routing path is fixed and non-shareable. Circuit-switch routing is efficient in that the routed paths are static, thus the behavior of the circuit netlist is deterministic. However, the drawback is that it imposes a large routing footprint, thus leading to inefficient implementation due to long routing wires between cells that are far apart if the tool could not find any shorter connections. Another issue is routing congestion, in that there are limited amount of routing resources for a particular fabric region that are densely packed with logic cells that have high connectivity demands.

To mitigate these issues, there are existing works that build a soft NoC on top of the programmable fabric [42]. A soft NoC is constructed by primitive elements such as LUTs, FFs, and occasionally dense RAM blocks such as BRAMs. A NoC helps decentralize the routing of PL modules, thereby alleviating issues such as long connected wires and congested regions. For instance, assume a design has several modules that want to access an external DRAM controller. A typical implementation would lead to a situation in which the region near the DRAM controller (usually at the edge of a device) is highly packed and congested. Instead, if a NoC were virtualized on the fabric, the placement of the modules would spread out since each module connects to a NoC router. Furthermore, the routing from modules to the DRAM is contained within the NoC links. The apparent disadvantage of a soft NoC is due to its cost, and poor performance since it is made of programmable fabric resources. The NoC incurs extra latency on the communication paths due to the extra pipelined registers or buffers. Several works propose cost-efficient soft NoC architectures [40, 41] by reducing the amount of buffering in a NoC router. Additionally, some forms of NoC routing, such as packet-switching mode [21], do not maintain the deterministic of a circuit netlist, i.e., the communication latency could vary. Since packet-switch routing allows sharing connections, a NoC router introduces an arbitration mechanism to select among concurrent flows of signal. This typically should not be a problem if the PL modules employ some latency-insensitive communication protocol, such as handshakes. If, however, the determinism constraint is imposed on the communication between PL modules, some NoC designs allow users to configure the Quality-of-Service (QoS) to produce a NoC routing that provides deterministic latency.

Some researchers [2] propose embedding a hard NoC on an FPGA to bypass the issues of soft NoC. Similar to other hard block resources, a PL module could directly access a hard NoC resource on the programmable fabric. A hard NoC is generally cheaper and faster than its counterpart implemented by programmable logic resources. [63] discusses NoC modeling on an open-source CAD tool flow and placement optimizations to achieve better QoR in terms of congestion, critical path delay, and aggregated NoC bandwidth.

#### 2.3.2 Commercial Architectures

Versal is the latest AMD FPGA architecture featuring a novel hardened NoC [25, 64]. The NoC presents a unified communication backbone with high-bandwidth data transfer between the Programmable Logic (PL), the Processing Systems, the DDR, and other platform subsystems. According to [69], on the PL, the NoC endpoints, namely NoC Master Unit (NMU) and NoC Slave Unit (NSU) are laid out in columns. A NoC Packet Switches (NPS) performs transport and packet switching on a path between an NMU and NSU. An NMU issues requests from the PL to the network, whereas an NSU services requests from the network to the PL. The NoC supports both AXI Memory-mapped and AXI Stream interfaces. Regarding our target FPGA device, the hard NoC runs at 1GHz on a 128-bit datapath. Hence, the maximum bandwidth of a NoC link is 16GB/s. The NoC is statically routed by the vendor NoC compiler during the implementation. Users characterize the NoC configuration at the design phase, such as the connectivities between which NMUs and NSUs, the estimated bandwidth and latency requirements for each connection. The NoC compiler takes into consideration these constraints to provide a solution that satisfies them.

Another commercial FPGA architecture, Intel AgileX, also employs a hardened NoC interconnect called FlexNoC [32]. FlexNoC adopts a packet-switch routing style and 128-bit datawidth. Achronix Speedster7t builds a 2D NoC with rows and columns running through the programmable fabric whereby each row or column features two 256-bit AXI channels [4]. It also supports packet-based transactions.

## 2.4 Overlays

Overlay is a well-known technique to address productivity issues, especially those that are concerned with programmability and compile time. An overlay is a virtualization of a logical compute organization on a physical Programmable substrate. The flexibility of FPGAs lends itself adaptable to a variety of compute organizations. For example, one could implement a general-purpose processor on an FPGA. The processor could have several vector units, or support out-of-order execution. It could also incorporate multi-level caches to improve data locality. The more generality an overlay architecture possesses, the more applicability it becomes. This means it can support a wide range of applications. Therefore, it removes the need for recompilation of the FPGA design. General-purpose processors also bring the benefit of allowing programmers to write programs in high-level languages. Thus, the programmability issue could be solved as well, if the overlay implements an architecture whose Instruction Set Architecture (ISA) is supported by some existing software compiler toolchains.

One of the main applications of FPGAs is hardware emulation and validation. Before taping out, an ASIC design is synthesized into one or several FPGAs to confirm its synthesizability and functionality. In the FPGA computing domain, this emulation, or overlay, approach is utilized to provide a software-like experience to users. Nonetheless, there are a few important considerations to keep in mind when synthesizing an overlay to the programmable fabric. The first issue is the QoR of the overlay implementation. Some constructs, intended for ASIC implementation, do not map efficiently to FPGA resources. One example is a large multi-ported Register File (RF) in a CPU. In ASIC technology, an RF could be mapped to SRAMs or latches compactly. However, an RF causes a huge register pressure when mapping to FPGAs. Therefore, an overlay architecture often needs some redesigns to ensure efficient implementation on FPGAs, otherwise, it could yield a circuit with poor QoR (e.g., low achievable maximum frequency). The second point is the tradeoff between generality and performance. A more generalized overlay may entail a more expensive circuit, leading to longer critical paths. A less generic one will require recompilation more often when targeting different applications requiring distinct functionalities. The third aspect is the high-level mapping toolchain. We need to provide a tool flow that compiles an input program to the overlay architecture. This is typically not an issue if the overlay is based on some machine organization that already has supported compilers. If that is not the case, the designers must take great care in devising an effective compilation flow to reach reasonable performance.

[37, 36] exploited the DSP blocks to build efficient FPGA overlay with high throughput, and used OpenCL as an input programming language. [45] built an architectural template that allows users to vary the hardware design for design exploration, while also employing OpenCL for programming. In a similar vein, [15] translated an input program to a multistage dataflow pipeline architectural template for a more effective overlapping of memory latency and computation. [46] presented a framework for a rapid loop accelerator by building a soft coarse-grained reconfigurable array (CRGA). [66] built a CRGA with keen attention to the communication network and data movement that uses HLS for code generation. [48] is an automated framework for generating efficient domain-specific overlays by employing design space exploration techniques and is also compatible with HLS. [47] is a custom router overlay that exploits the fabric regularity to achieve fast compilation and better achievable frequency. There are overlays built towards specific domains, such as sparse matrix computation [62, 38], graph processing [29], stencil [16], or neural network [3, 88, 86, 85, 50, 8, 67, 28]. These are typically accelerator-based designs that offer programmable capability at runtime to a certain degree. On the other hand, most general-purpose overlays utilize common parallel languages/models such as OpenCL or HLS for input designs. We also note that besides computational or accelerator based overlays, there are others that serve as communication infrastructure, such as on-chip network routers, or virtualized memory architecture as shown in CoRAM [18]. Our work is similar to CoRAM in several aspects. We also develop a distributed compute-memory architecture whereby each processing element (or socket) defines its own compute and memory space, and the control of data movement between off-chip and on-chip memory is carried out by a software mechanism. Yet, the details of the control mechanism and data movement are different between both works. For example, we use DMA-based data transfers instead of stream-based communication in CoRAM. Our controller also schedules computation in addition to data movement tasks. More importantly, CoRAM does not address the compile time issue as in our work. Still, the idea of employing a control thread for explicit data movement through a high-level software code helps simplify application development, and subsequently improves the productivity.

## 2.5 Separate Compilation and Task Partitioning

Separate compilation refers to techniques that divide up an application to smaller modules for parallel compilation. Standard vendor tools make use of this approach during the synthesis phase in which there are different RTL blocks of a design that could be synthesized or implemented separately at the same time [72]. [76] used partial reconfiguration and built a packet-switched overlay network to support incremental and parallel compilation of separate modules to reduce the compile time. [75] built an array of soft processor cores and introduced a compilation flow that is akin to the traditional software compiler toolchains. [73] proposed dedicated interconnect wires between processing elements to remove the need for a soft NoC overlay for communication. HIPR [74] took advantage of an HLS tool for application mapping instead of manual RTL designs. An application is split into smaller modules for fast incremental compilation with partial reconfiguration support. [59] implemented a hierarchical partial reconfiguration flow whereby smaller partitions (or pages) can be combined into larger pages if needed to increase the flexibility of application mapping. Autobridge [26] optimized the HLS designs for multi-die FPGAs by providing the floorplanning information earlier in the HLS phase, thus facilitating the insertion of pipelined registers to optimize timing for die-crossing nets. RapidStream [27] split an HLS dataflow design into separate tasks for parallel compilation, and then assemble the physical implementations.

We adopt a similar approach in separate, parallel compilations of smaller tasks in our backend flow, and we also use HLS to provide a design entry to our flow. Nevertheless, we would like to highlight a few key differences. The uniqueness of our approach is that we tailor an input application to follow our parallel execution model, hence facilitating better mapping in terms of compile time and performance. In addition, we exploit design reuse opportunities within each separate task or processing engine. We conduct our studies on a state-of-the-art FPGA device that features a hardened NoC. While we do not attempt to implement task-level partial reconfiguration in this work due to time constraints, we think that we could benefit from previous works by extending their ideas to work with our tool flow.

# Chapter 3

# From SPADES to Socket

## 3.1 SPADES execution model

SPADES presents a parallel system of sockets connected by a NoC. As illustrated in Figure 3.1, a socket is a processing element containing a control unit, memory block, and a compute block. The control unit is the brain of a socket. It performs the scheduling of several operations such as data movements or computations that involve the memory and compute block. The control unit of one socket can also synchronize with other sockets by means of exchanging messages over the network.

The memory block is a software-managed scratchpad rather than a cache. Therefore, a socket must initiate data transfer to/from the memory block. The compute unit is not exposed to the network; it accesses the memory unit for data. Different sockets may have unique implementations of the compute units or memory units or a group of sockets may share similar implementations. Note that the socket's sizes are not necessarily identical; some sockets may require larger areas for compute or memory demand.

The NoC is statically routed; the routing is done at compile time. In addition, we adopt a packet switch routing for the NoC in this model. This allows different communication paths to share common routing channels. A routing channel is a connection path between two adjacent routers. In this model, each router is associated with one socket. There is a maximum bandwidth for each routing channel.

Here we only define the high-level organization of computation and communication, hence an execution model. The internal details of a compute, memory, or control unit remain abstract. The advantage of this model is its flexibility in adapting to different parallelism models, such as Task-level parallelism (each socket implements different tasks), or Datalevel parallelism (all sockets share the same implementation of compute and memory, but operates on different workloads.) as shown in Figure 3.2. The drawback of this model is that it is not efficient for applications consist of simple dataflow pipelines. In particulars, if each dataflow task in the pipeline is mapped to different sockets, this will incur some overhead of scheduling and coordinating the data movement between the sockets; it involves getting

Figure 3.1: SPADES featuring a parallel, distributed system of socket engines.

Figure 3.2: Each task of an application could be assigned to different groups of SPADES' sockets.