# **UC Davis**

#### **UC Davis Electronic Theses and Dissertations**

#### **Title**

Hardware/Software Co-Design for Secure High Performance Computing Systems

#### **Permalink**

https://escholarship.org/uc/item/83r536h8

#### **Author**

Akram, Ayaz

#### **Publication Date**

2023

Peer reviewed|Thesis/dissertation

# Hardware/Software Co-Design for Secure High Performance Computing Systems

By

Ayaz Akram

#### DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

Computer Science

in the

OFFICE OF GRADUATE STUDIES

of the

University of California

Davis

Approved:

Jason Lowe-Power, Chair

Venkatesh Akella

Sean Peisert

Committee in Charge

2023

Copyright © 2023 by Ayaz Akram All rights reserved.

# Contents

|          | List | of Figu | res                                                      | V   |

|----------|------|---------|----------------------------------------------------------|-----|

|          | List | of Tabl | les                                                      | Х   |

|          | Abs  | tract . |                                                          | X   |

|          | Ack  | nowledg | gments                                                   | xii |

| 1        | Intr | oducti  | on                                                       | 1   |

|          | 1.1  | Secure  | e High Performance Computing                             | 1   |

|          | 1.2  | Truste  | ed Execution Environments and High Performance Computing | 2   |

|          | 1.3  | Contri  | ibutions                                                 | 4   |

|          | 1.4  | Organ   | ization                                                  | 5   |

| <b>2</b> | Mo   | tivatio | n and Background                                         | 7   |

|          | 2.1  | Securi  | ty Issues in High Performance Computing Environments     | 7   |

|          |      | 2.1.1   | HPC vs. Cloud Systems                                    | 8   |

|          | 2.2  | Confid  | lential Computing                                        | Ö   |

|          |      | 2.2.1   | Beyond TEEs                                              | 11  |

|          | 2.3  | Confid  | lential High-Performance Computing via TEEs              | 11  |

| 3        | Lim  | itation | ns of Confidential Computing via TEEs for HPC Systems    | 13  |

|          | 3.1  | Introd  | uction                                                   | 13  |

|          | 3.2  | Comp    | uting Landscape                                          | 14  |

|          |      | 3.2.1   | History                                                  | 14  |

|          |      | 3.2.2   | Current Computing Landscape                              | 15  |

|          | 3.3  | HPC I   | Focused Trusted Execution Environments                   | 16  |

|          | 3.4  | System  | natization of TEEs                                       | 18  |

|          |      | 3.4.1   | Page Table Entry Metadata                                | 18  |

|          |      | 3.4.2   | Encryption                                               | 18  |

|          |      | 3.4.3   | Physical memory isolation via ISA extensions             | 19  |

|          |      | 3.4.4   | Use of tags/identifier in hardware                       | 19  |

|          |      | 3.4.5   | Privileged Software/Hardware                             | 19  |

|   |                   | 3.4.6                                                                                                        | Classification of TEEs                | 20                                                             |

|---|-------------------|--------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------|

|   | 3.5               | Limita                                                                                                       | ations of Existing TEEs               | 22                                                             |

|   |                   | 3.5.1                                                                                                        | Heavy Application Code Modifications  | 22                                                             |

|   |                   | 3.5.2                                                                                                        | Large Trusted Compute Base (TCB)      | 23                                                             |

|   |                   | 3.5.3                                                                                                        | Focus on Core Level Execution         | 24                                                             |

|   |                   | 3.5.4                                                                                                        | No Consideration of Side Channels     | 25                                                             |

|   |                   | 3.5.5                                                                                                        | Other Limitations                     | 25                                                             |

|   | 3.6               | Potent                                                                                                       | tial Research Directions              | 26                                                             |

|   |                   | 3.6.1                                                                                                        | Data Centric Enclaves                 | 27                                                             |

|   | 3.7               | Other                                                                                                        | Topics                                | 28                                                             |

|   |                   | 3.7.1                                                                                                        | Survey of Attacks on TEEs/Enclaves    | 28                                                             |

|   |                   | 3.7.2                                                                                                        | Tools for TEE Platforms               | 29                                                             |

|   |                   | 3.7.3                                                                                                        | Formal Verification of TEEs           | 29                                                             |

|   | 3.8               | Conclu                                                                                                       | usion                                 | 30                                                             |

|   |                   |                                                                                                              |                                       |                                                                |

| 1 | A 9               | tudy o                                                                                                       | on the Performance of Commercial TFFs | 21                                                             |

| 4 |                   | v                                                                                                            | on the Performance of Commercial TEEs | 31                                                             |

| 4 | 4.1               | Threa                                                                                                        | t Model                               | 31                                                             |

| 4 |                   | Threa Selecte                                                                                                | t Model                               | 31<br>32                                                       |

| 4 | 4.1               | Thread Selector 4.2.1                                                                                        | t Model                               | 31<br>32<br>32                                                 |

| 4 | 4.1 4.2           | Threat<br>Selected<br>4.2.1<br>4.2.2                                                                         | t Model                               | 31<br>32<br>32<br>33                                           |

| 4 | 4.1               | Threat Selected 4.2.1 4.2.2 Method                                                                           | t Model                               | 31<br>32<br>32<br>33<br>33                                     |

| 4 | 4.1 4.2           | Threa Selector 4.2.1 4.2.2 Method 4.3.1                                                                      | t Model                               | 31<br>32<br>32<br>33<br>33<br>34                               |

| 4 | 4.1 4.2           | Threa Selecter 4.2.1 4.2.2 Method 4.3.1 4.3.2                                                                | t Model                               | 31<br>32<br>33<br>33<br>34<br>34                               |

| 4 | 4.1 4.2           | Threa Selected 4.2.1 4.2.2 Method 4.3.1 4.3.2 4.3.3                                                          | t Model                               | 31<br>32<br>33<br>33<br>34<br>34<br>36                         |

| 4 | 4.1<br>4.2<br>4.3 | Threa Selector 4.2.1 4.2.2 Method 4.3.1 4.3.2 4.3.3 4.3.4                                                    | t Model                               | 31<br>32<br>33<br>33<br>34<br>34<br>36<br>37                   |

| 4 | 4.1 4.2           | Threa Selector 4.2.1 4.2.2 Method 4.3.1 4.3.2 4.3.3 4.3.4 Under                                              | t Model                               | 31<br>32<br>33<br>33<br>34<br>34<br>36<br>37<br>38             |

| 4 | 4.1<br>4.2<br>4.3 | Threa<br>Selector<br>4.2.1<br>4.2.2<br>Methor<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Under<br>4.4.1          | t Model                               | 31<br>32<br>33<br>33<br>34<br>34<br>36<br>37<br>38             |

| 4 | 4.1<br>4.2<br>4.3 | Threa<br>Selector<br>4.2.1<br>4.2.2<br>Methor<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Under<br>4.4.1<br>4.4.2 | t Model                               | 31<br>32<br>33<br>33<br>34<br>34<br>36<br>37<br>38<br>40<br>45 |

| 4 | 4.1<br>4.2<br>4.3 | Threa<br>Selector<br>4.2.1<br>4.2.2<br>Methor<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Under<br>4.4.1          | t Model                               | 31<br>32<br>33<br>33<br>34<br>34<br>36<br>37<br>38             |

|   | 4.5 | Beyond Single Node                                                        | 51 |

|---|-----|---------------------------------------------------------------------------|----|

|   |     | 4.5.1 Trusted HPC in the Cloud                                            | 52 |

|   | 4.6 | Observations on Security of SGX and SEV                                   | 54 |

|   | 4.7 | Scientific Computing Focused Trusted Execution Environment                | 55 |

| 5 | DES | SC – Data Enclaves for Scientific Computing                               | 59 |

|   | 5.1 | Introduction                                                              | 59 |

|   | 5.2 | Related Work on Confidential Computing                                    | 62 |

|   | 5.3 | Threat Model                                                              | 64 |

|   | 5.4 | DESC Based Computing Systems                                              | 65 |

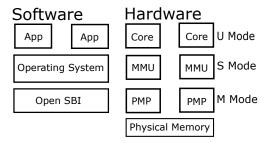

|   |     | 5.4.1 Background on today's computing systems                             | 65 |

|   |     | 5.4.2 RISC-V Isolation Mechanisms                                         | 66 |

|   |     | 5.4.3 Security Guarantee of $DESC$                                        | 66 |

|   |     | 5.4.4 Design Principles for $DESC$                                        | 68 |

|   | 5.5 | Design of Data Enclaves for Scientific Computing $(DESC)$                 | 68 |

|   |     | 5.5.1 High-Level Overview                                                 | 69 |

|   |     | 5.5.2 Case C1: Execution Mode Switch                                      | 73 |

|   |     | 5.5.3 Case C2: Data Sharing                                               | 75 |

|   |     | 5.5.4 Case C3: OS-based Resource Management                               | 76 |

|   |     | 5.5.5 Out of Scope Components of Enclave                                  | 80 |

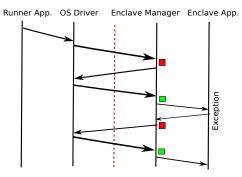

|   | 5.6 | DESC Workflow                                                             | 80 |

|   |     | 5.6.1 Enclave Creation                                                    | 81 |

|   |     | 5.6.2 Enclave Running                                                     | 82 |

|   |     | 5.6.3 Creating New Enclave Thread                                         | 83 |

|   | 5.7 | Results and Evaluation                                                    | 83 |

|   | 5.8 | Conclusion                                                                | 87 |

| 6 | Sim | ulation and Architectural Evaluation of TEEs                              | 88 |

|   | 6.1 | Keystone in gem5                                                          | 89 |

|   |     | 6.1.1 Validation                                                          | 90 |

|   | 6.2 | Case Study: Microarchitecture Impact on Performance of Secure Execution . | 92 |

| 7 | Future Work |         |                                                      |     |

|---|-------------|---------|------------------------------------------------------|-----|

|   | 7.1         | Impro   | ving Existing TEEs                                   | 94  |

|   |             | 7.1.1   | Software Frameworks                                  | 94  |

|   |             | 7.1.2   | Research Avenues for Computer Architecture           | 96  |

|   | 7.2         | Explo   | ration of New Ways to Build TEEs                     | 97  |

|   |             | 7.2.1   | New Hardware Primitives                              | 97  |

|   |             | 7.2.2   | Horizontal Privilege Levels                          | 98  |

|   |             | 7.2.3   | Capability Based Enclaves                            | 98  |

|   | 7.3         | Future  | e Work on DESC                                       | 98  |

|   |             | 7.3.1   | Disaggregated Data Enclaves for Scientific Computing | 98  |

| 8 | Con         | nclusio | a                                                    | 102 |

# LIST OF FIGURES

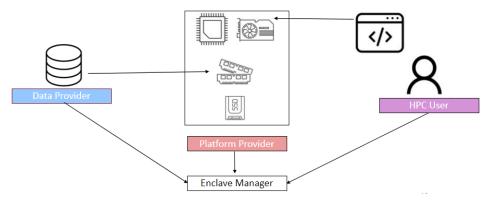

| 2.1 | Interaction of multiple actors in an HPC center                                  | 8  |

|-----|----------------------------------------------------------------------------------|----|

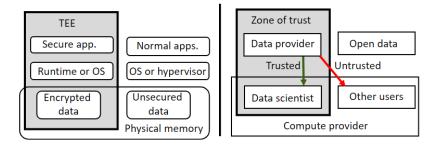

| 2.2 | Trusted execution in traditional computing systems. 'C' stands for a core.       |    |

|     | Zone of trust referst to secure computational and memory resources used by       |    |

|     | a secure application that is enabled via the used of a TEE                       | 12 |

| 2.3 | Creating a zone of trust for sensitive data in HPC centers. The figure on the    |    |

|     | left shows a general TEE and the figure on the right shows how that TEE          |    |

|     | can be used to enable a data scientist to compute on sensitive data provided     |    |

|     | by a trusted data provider and keep it secure from other entities in the system. | 12 |

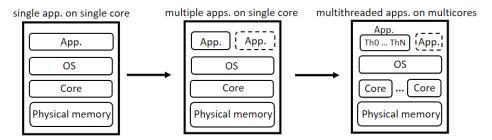

| 3.1 | History of the computing landscape. This figure shows the evolution pro-         |    |

|     | cess of traditional high-performance computing systems. Computing systems        |    |

|     | have evolved from single processes on a single-core system to multi-threaded     |    |

|     | applications on heterogeneous multi-core systems                                 | 14 |

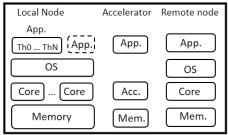

| 3.2 | Modern high performance computing systems. Applications on these systems         |    |

|     | scale across local nodes, (integrated or remote) accelerators, and remote nodes. | 17 |

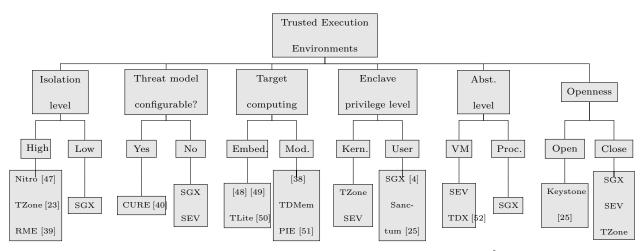

| 3.3 | Classification of TEEs and some examples of each class. [Note: Emb. :            |    |

|     | Embedded, Mod.: Modern, Kern. : Kernel, Cont. : Container, Proc. :               |    |

|     | Process, VM : Virtual Machine]                                                   | 20 |

| 3.4 | Required trusted system view. All compute elements and the memory em-            |    |

|     | ployed by the secure application should exist within a unified trust boundary.   | 27 |

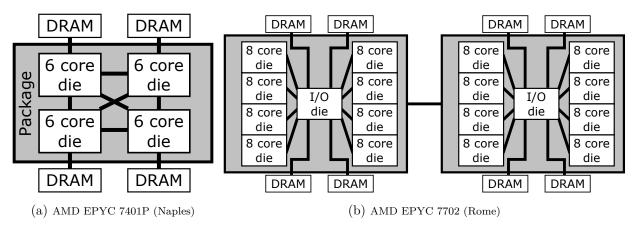

| 4.1 | Details of the non-uniform memory architecture for the two AMD systems           |    |

|     | evaluated                                                                        | 37 |

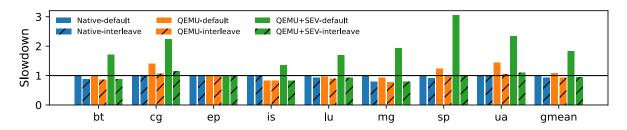

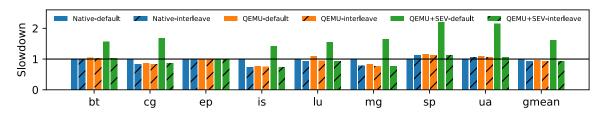

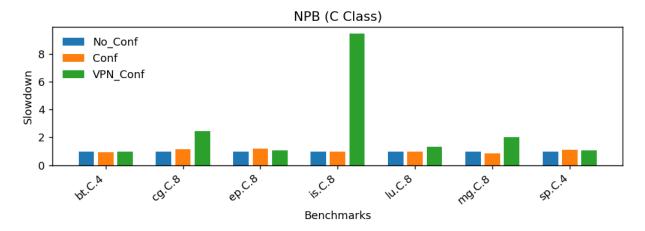

| 4.2 | Performance impact of SEV for NPB C Class on AMD Naples (24 Threads).            |    |

|     | The SEV performance overhead is mainly because of default NUMA memory            |    |

|     | allocation, most of which goes away with interleaved NUMA allocation             | 39 |

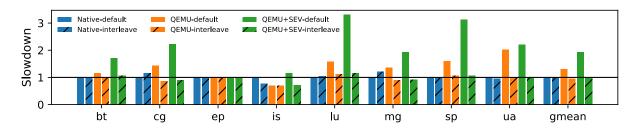

| 4.3 | Performance impact of SEV for NPB D Class on AMD Naples (24 Threads).            | 39 |

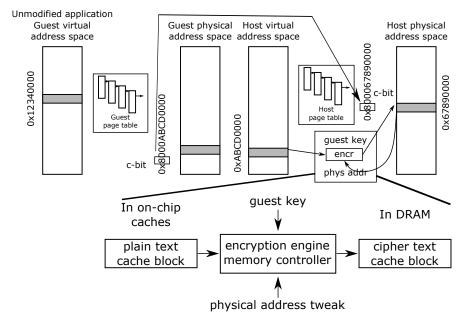

| 4.4 | Details of SEV encryption implementation                                         | 41 |

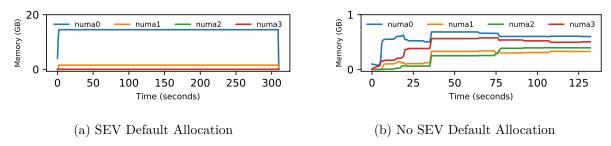

| 4.5 | Memory allocation over time using default policy                                 | 41 |

| 4.0  | Memory allocation over time using an interleave policy. Under SEV an equal      |    |

|------|---------------------------------------------------------------------------------|----|

|      | amount of memory is allocated across all nodes                                  | 43 |

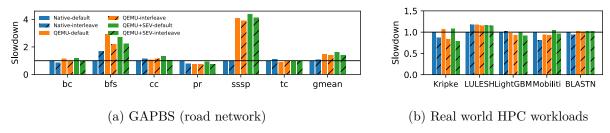

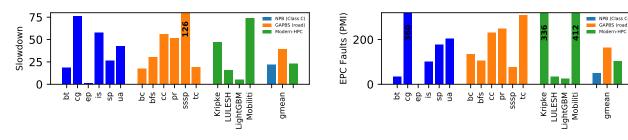

| 4.7  | Performance impact of SEV for GAPBS and other real world HPC workloads          |    |

|      | on AMD Naples (24 Threads). Interleaved NUMA allocation works for graph         |    |

|      | and other HPC workloads except BLASTN which shows high overhead mainly          |    |

|      | because of virtualized disk I/O operations.                                     | 43 |

| 4.8  | Performance impact of SEV for NPB D Class on AMD Rome (128 Threads)             | 44 |

| 4.9  | Performance impact of SEV for GAPBS and other real world HPC workloads          |    |

|      | on AMD Rome (128 Threads). NUMA placement still matters on platforms            |    |

|      | with more uniform memory architecture. Two examples where main cause of         |    |

|      | overhead is virtualization are bfs and sssp                                     | 44 |

| 4.10 | NPB D Class on AMD EPYC 7402P (24 Threads)                                      | 45 |

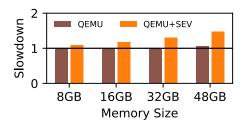

| 4.11 | Performance of VM boot (relative to QEMU-8GB)                                   | 47 |

| 4.12 | Performance Impact of SGX and its Relation to EPC (Enclave Page Cache)          |    |

|      | Faults. Slowdown and EPC faults show a strong correlation indicating that       |    |

|      | the workloads with higher secure to non-secure memory movement rates will       |    |

|      | exhibit higher slowdown                                                         | 47 |

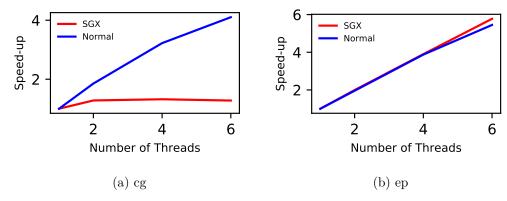

| 4.13 | Impact of Multiple Execution Threads. Workloads with high resident memory       |    |

|      | like $cg$ do not scale well with the number of execution threads in contrast to |    |

|      | low resident memory workloads like $ep$ . Handling of EPC faults by the SGX     |    |

|      | kernel driver becomes the serializing factor in case of high resident memory    |    |

|      | workloads.                                                                      | 49 |

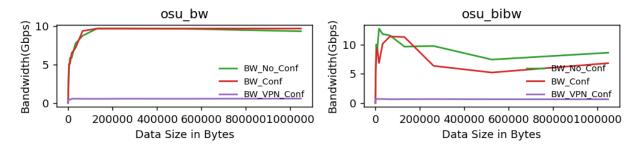

| 4.14 | Bandwidth Test from OSU Microbenchmarks                                         | 52 |

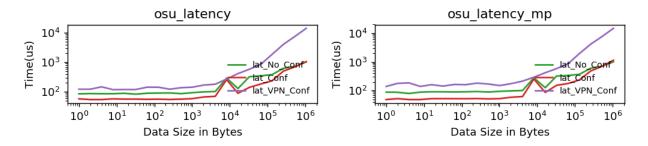

| 4.15 | Latency Test from OSU Microbenchmarks                                           | 52 |

| 4.16 | Slowdown for for NAS Parallel Benchmarks (C Class), 8 processes in total        |    |

|      | except bt and sp                                                                | 53 |

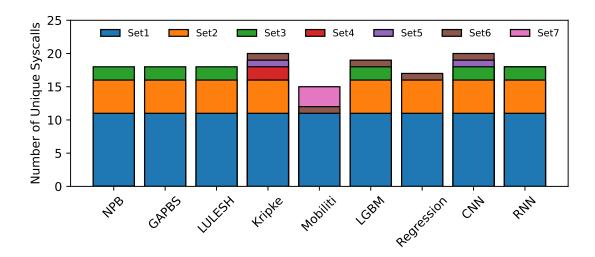

| 5.1  | Unique system calls used by all the evaluated benchmarks. Each set refers       |    |

|      | to a collection of system calls that are common across the benchmarks. The      |    |

|      | total number of unique system calls used by the evaluated workloads is $6\%$    |    |

|      | of the total available Linux system calls for RISC-V                            | 61 |

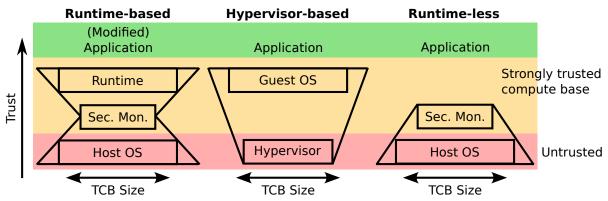

| 5.2  | A comparison of TCB size and location of trust among different enclave styles           |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | (Runtime-based, Hypervisor-based, DESC). DESC achieves the lowest size of               |    |

|      | the strongly trusted compute base                                                       | 63 |

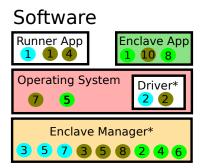

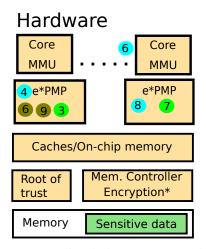

| 5.3  | Overview of RISC-V based computing system                                               | 66 |

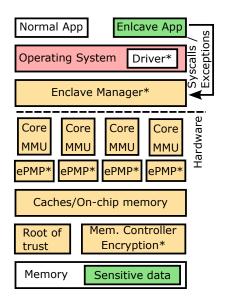

| 5.4  | High-level overview of Data Enclave for Scientific Computing. Red is un-                |    |

|      | trusted, orange is strongly trusted, green is sensitive. Stars (*) show the             |    |

|      | parts of the system we have added or extended. We discuss the driver in                 |    |

|      | Section 5.5.1.2, the <i>Enclave Manager</i> in Section 5.5.1.1, the <i>ePMP</i> in Sec- |    |

|      | tion 5.5.4.1, and encryption engine in Section 5.5.1.3.                                 | 69 |

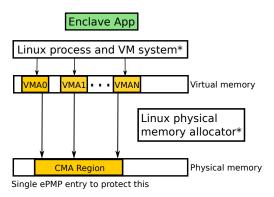

| 5.5  | Modified Linux physical memory allocation. Starred entities are modified                |    |

|      | parts of the Linux kernel and interact with other kernel and data enclave               |    |

|      | components                                                                              | 73 |

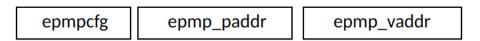

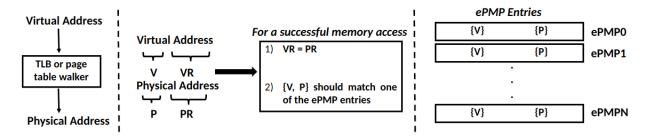

| 5.7  | Single $ePMP$ entry. $ePMP$ stores virtual address of a memory range as well            |    |

|      | in addition to the physical address                                                     | 78 |

| 5.8  | Virtual and physical addresses of a VMA range. Since, a VMA region is                   |    |

|      | given a contiguous chunk of physical memory via the modified Linux memory               |    |

|      | allocator, VR and PR bits of the addresses should match                                 | 78 |

| 5.9  | ePMP based memory access checks to ensure memory protection and address                 |    |

|      | mapping integrity.                                                                      | 78 |

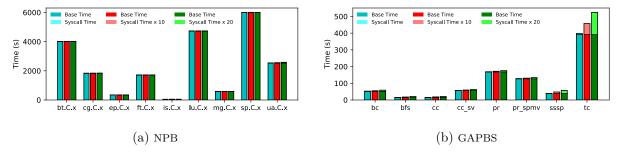

| 5.13 | Impact of change in the system call execution time on the overall execution             |    |

|      | time. The motivation behind using syscall inspection for HPC-style workloads            |    |

|      | is that the time spent in system calls (even if scaled by a large factor) is a          |    |

|      | small fraction of the overall execution time                                            | 84 |

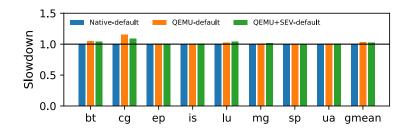

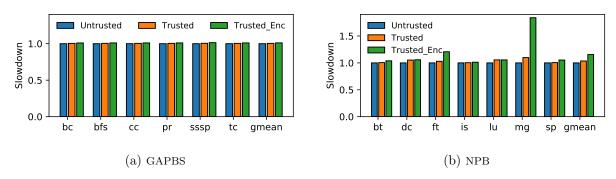

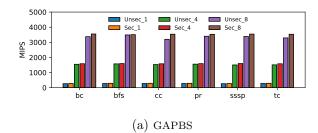

| 5.14 | Comparison of slowdown (does not include enclave creation penalty) for GAPBS            |    |

|      | and NPB benchmark suite. Trusted refers to the trusted execution of the                 |    |

|      | benchmarks (using $DESC$ ) and Trusted_Enc refers to the trusted execution              |    |

|      | with memory encryption (for data leaving the CPU package) on as well                    | 84 |

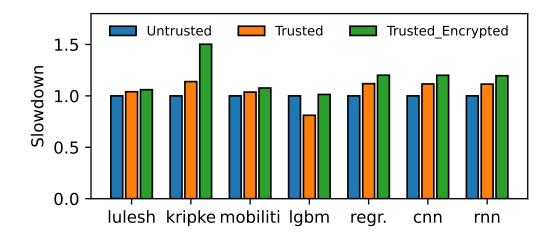

| 5.15 | Slowdown for modern HPC and ML workloads. Regression (linear regression),               |    |

|      | CNN (convolution neural net.), and RNN (recurrent neural net.) are based                |    |

|      | on Torch                                                                                | 84 |

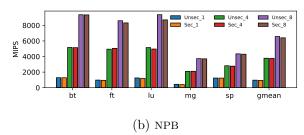

| 5.16 | Million (usermode) instructions executed per second of simulation time. This          |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | is the sum of instructions across all cores. Unsec<br>_[cores] refers to unsecure ex- |     |

|      | ecution and Sec_[cores] refers to trusted execution with $DESC$ , where [cores]       |     |

|      | is the number of threads of the benchmark and processing cores                        | 85  |

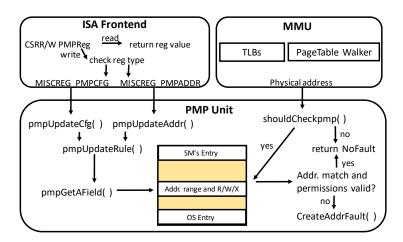

| 6.1  | PMP implementation in gem5                                                            | 90  |

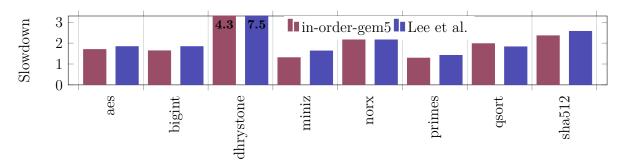

| 6.2  | Comparison of slowdowns (incurred by trusted execution using Keystone)                |     |

|      | between gem5 and Lee et al. [1]. This slowdown includes enclave creation              |     |

|      | and management time as well                                                           | 91  |

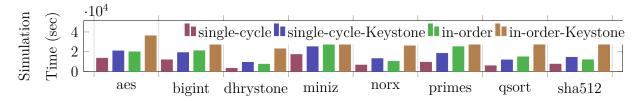

| 6.3  | Time taken by gem5 to simulate rv8 [2] benchmarks on a single cycle (Tim-             |     |

|      | ingSimpleCPU) and an in order (MinorCPU) CPU models of gem5 with and                  |     |

|      | without Keystone.                                                                     | 91  |

| 6.4  | Microarchitecture impact on performance of secure compute environments.               |     |

|      | In the legend entries SC: single cycle, IO: in-order, def: default configuration      |     |

|      | from Table 6.1, fu540: fu540-like configuration from Table 6.1, and large:            |     |

|      | large configuration from Table 6.1. 'trust-ov' stands for overhead of trusted         |     |

|      | execution                                                                             | 93  |

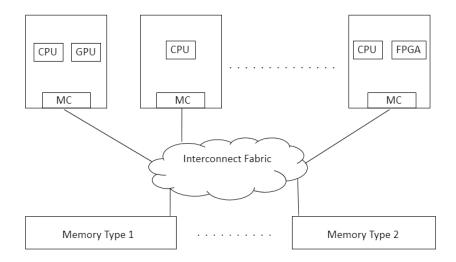

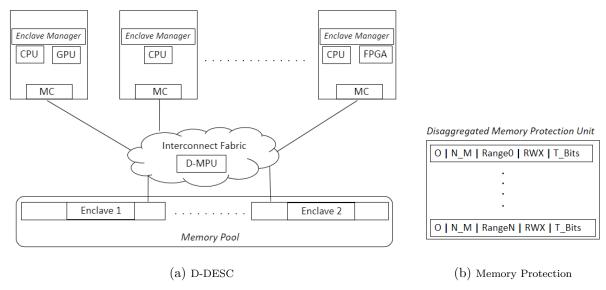

| 7.1  | An example of a disaggregated memory system (MC: memory controller)                   | 100 |

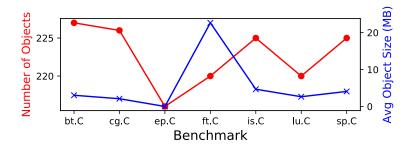

| 7.2  | Memory allocations of NPB                                                             | 100 |

| 7.3  | High level overview of Disaggregated Data Enclaves for Scientific Computing           |     |

|      | (D-DESC)                                                                              | 101 |

# LIST OF TABLES

| 2.1 | HPC Use Cases                                                              | 7  |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Primary security properties of TEEs                                        | 10 |

| 3.1 | Survey of Attacks on TEEs/Enclaves                                         | 28 |

| 3.2 | Example of Tools/Frameworks for TEEs                                       | 28 |

| 4.1 | Feature Comparison                                                         | 34 |

| 4.2 | Details of the workloads evaluated                                         | 35 |

| 4.3 | System Configurations. See Figure 4.1 for details on the two EPYC systems. | 37 |

| 5.1 | Comparison of enclave types: $DESC$ requires no application changes, has   |    |

|     | reduced TCB, and has smaller performance impact. Evaluation details of     |    |

|     | DESC are presented in Section 5.7                                          | 63 |

| 5.2 | Main feature of the configuration tested on gem5                           | 83 |

| 6.1 | Main feature of the configurations tested on gem5                          | 92 |

#### Abstract

# Hardware/Software Co-Design for Secure High Performance Computing Systems

High-performance computing (HPC) is increasingly becoming more data-centric, involving large data sets, rather than its historical focus on modeling and simulation. Sometimes, this data can be sensitive, provided by third parties to HPC centers or individual researchers, and raises security concerns regarding the confidentiality or integrity of the data. Our work aims to provide secure systems focused on HPC centers, without any significant performance reductions. Hardware-based trusted execution environments (TEEs) use hardware-backed techniques to provide some level of assurance for data and code confidentiality, and integrity. We first study the applicability of commercial hardware-based trusted execution environments (TEEs) to enable secure scientific computing. We rigorously analyze the performance impact of general purpose TEEs, AMD SEV, and Intel SGX, for diverse HPC benchmarks including traditional scientific computing, machine learning, graph analytics, and emerging scientific computing workloads. We also analyze the impact of the programming model required by these TEEs. The results show that commercial TEEs do not fit the HPC use case, either because their performance implications are intolerable, they require significant application changes (e.g., partitioning, linking applications against specific libraries), or their threat model does not include all system components that HPC applications might use. We provide a design point for enclaves that does not require an entire OS inside the enclave but can rely on a primarily untrusted OS for resource management. We implement a prototype data enclave, called *DESC*, with multithreading support on the RISC-V ISA that separates the management of the system from the protection of the sensitive data. We show how DESC allows an untrusted OS to maintain page tables, service system calls, and manage processes without compromising the enclave applications data confidentiality or integrity.

Cycle-level architectural simulation of trusted execution environments (TEEs) can enable extensive design space exploration of these secure architectures. Existing architectural simulators that support TEEs are either based on hardware-level implementations or abstract

analytic models. To this end, we enable a simulation environment using full-system architecture simulator, gem5, and a RISC-V based open source TEE, Keystone, and show how this simulation support opens new avenues for designing and studying these trusted architectures. Future HPC systems are expected to improve resource utilization by decoupling compute and memory extensively, leading to disaggregated architectures composed of different types of processing elements and remote memory pools. We also explore the expansion of our baseline TEE design (DESC) to provide scalable mechanisms that would allow a user to form a secure enclave spanning multiple processing elements.

#### ACKNOWLEDGMENTS

I extend my heartfelt gratitude to my advisor, Prof. Jason Lowe-Power, for his invaluable guidance, unwavering support, and encouragement throughout my research journey. His mentorship has been an endless source of motivation during my PhD studies. I am deeply appreciative of the knowledge and wisdom I've gained from his expertise, and I will always hold profound gratitude towards him. I am equally thankful to my collaborators, Prof. Venkatesh Akella and Prof. Sean Peisert, for their contributions to this work.

I am indebted to the other members of the Qualifying exam committee, Prof. Houman Homayoun, and Prof. Sam King, for their insightful feedback and guidance, which significantly enriched this research.

My deepest appreciation goes to my parents for their unwavering support, sacrifices, and boundless love that have been instrumental in helping me reach my academic goals. I am also grateful to my siblings for their continuous encouragement and support.

I extend my thanks to all the members of the Davis Architecture Research Group (DArchR) at UC Davis. Engaging in discussions with this diverse and talented group has provided me with invaluable insights, both technical and non-technical, and has broadened my perspective across various fields. Their support and assistance have been invaluable to me.

# Chapter 1

# Introduction

# 1.1 Secure High Performance Computing

High-performance computing (HPC) is moving away from traditional simulation and modeling to large-scale computational problems involving large datasets. Sometimes this data can be sensitive, provided by third parties to HPC centers or individual researchers, and raises security concerns. This dissertation addresses the imperative need for secure systems tailored to the unique demands of HPC centers and their users while striving to minimize the performance impact.

Security guarantees are mainly encapsulated in the CIA triad (confidentiality, integrity, and availability). Confidentiality involves the protection of sensitive and private information from unauthorized disclosure. Integrity relates to the accuracy and reliability of data and systems. Data integrity ensures that information remains unaltered and trustworthy throughout its lifecycle. And availability ensures that compute and memory resources are always available to the application of interest.

In the world of scientific computing, ensuring security, including integrity and confidentiality, is paramount. Security measures for scientific computing aim to safeguard against cyber threats, preserving valuable computational research resources. Data integrity policies and mechanisms seek to guarantee the accuracy of findings by preventing unauthorized changes, while confidentiality policies and mechanisms seek to protect sensitive information, respecting ethical boundaries and legal requirements. These properties collectively seek to safeguard research investments, maintain reputations, facilitate collaboration, and ensure

adherence to regulations, contributing to the advancement of knowledge and innovation. By enabling secure HPC facilities, we can ensure regulatory compliance and ultimately propel the frontiers of scientific discovery.

Security solutions designed for the cloud computing environment may not apply to highperformance computing (HPC) due to differences in architectural requirements, performance

priorities, and data handling workflow between the two types of platforms. On one hand,

scientific computing revolves around research-oriented simulations and analyses, often necessitating specialized environments and high-performance computing capabilities. In contrast,

cloud computing presents adaptable and diverse resources applicable to various industries,

underpinned by features like virtualization and a wide array of services. The convergence

of these domains is exemplified by cloud platforms accommodating scientific workloads, providing researchers with immediate access to potent computational resources. While shared

security concerns like data integrity and unauthorized access are present in both realms, they

manifest uniquely due to differing contexts. Scientific computing underscores research credibility and data safeguarding, whereas cloud computing prioritizes fortifying shared resources,

data confidentiality, and adhering to regulations. Given these contrasting computational

landscapes, solutions tailored for secure cloud computing might not seamlessly translate to

high-performance computing (HPC) environments.

# 1.2 Trusted Execution Environments and High Performance Computing

Hardware-based trusted execution environments (TEEs) use hardware-backed techniques to provide a certain level of assurance for data and code confidentiality and integrity. In this thesis, we present a systematization of the existing trusted execution environments in industry and academia. We also highlight the common mechanisms these TEEs employ to provide different security guarantees and offer a detailed comparative analysis of different TEE proposals. TEEs are anticipated to be a promising solution for the security challenges in the high-performance computing (HPC) domain. However, we show why the existing TEEs are unsuitable for high-performance computing systems.

In this thesis, we rigorously analyze the performance impact of commercial general pur-

pose TEEs, AMD SEV [3], and Intel SGX [4], for diverse HPC benchmarks including traditional scientific computing, machine learning, graph analytics, and emerging scientific computing workloads. We also analyze the impact of the programming model required by these TEEs. The results show that the existing commercial TEEs do not fit the HPC use case, either because their performance impact is too high, they require significant application changes (e.g., partitioning, linking applications against specific libraries), or their threat model does not include all system components that HPC applications might use.

In this thesis, we present a novel data-centric confidential computing approach that leverages an operating system (OS) for resource management while circumventing the need to integrate the OS into the trusted computing base (TCB). Existing TEEs either require heavy application modifications (because they re-implement a limited set of system calls inside the enclave) or allow unmodified applications but include an entire OS as part of the TCB (e.g., VM-based enclaves). Both of these requirements pose challenges particularly in the context of high-performance computing (HPC) oriented systems.

Our contribution introduces an alternative enclave design paradigm that does not necessitate an entire OS within the enclave but instead relies on a mostly untrusted OS for resource management. To demonstrate this, we implement a prototype data enclave, named data enclave for scientific computing (DESC), with multithreading support on the RISC-V ISA that separates the management of the system from the protection of the sensitive data. We show how DESC allows an untrusted OS to maintain page tables, service system calls, and manage processes without compromising the enclave applications data confidentiality or integrity. We evaluate DESC using gem5 [5,6] for performance and QEMU [7] for functional correctness (as executing complete applications in a simulated environment can be impractical). We show that our design correctly executes a set of scientific computing workloads (NAS Parallel Benchmarks, graph workloads, and other modern scientific computing and machine learning workloads) on 1–8 cores. Further, we show there is only minor overhead (less than 5\% geometric mean for all benchmark suites) compared to running outside the enclave, even when modeling a 30-cycle memory encryption overhead (less than 20\% geometric mean). Cycle-level simulation of TEEs using architectural simulators is vital for comprehensive a design space exploration of these secure architectures. Current TEE simulators stem

from hardware-level implementations or abstract models. To this end, we enable a simulation environment using the full-system architecture simulator, gem5, and the RISC-V based open-source TEE, Keystone [1]. This simulation framework provides fresh opportunities for the design and analysis of trusted architectures. We use the same simulation framework for evaluation of DESC referred in the previous paragraph.

Lastly, we delve into potential extensions of our proposed trusted execution environment to diverse heterogeneous environments, such as disaggregated memory systems and accelerators.

In conclusion, the growing utilization of large sensitive datasets within HPC centers underscores the paramount importance of secure data processing. The concept of confidential computing presents a potential avenue for mitigating security risks associated with sensitive data in HPC. Nevertheless, current TEEs, despite being pivotal to confidential computing do not align with the requirements of HPC due to performance issues, programming models, and thread models. Through the proposition of a data-centric TEE, *DESC*, and the vision of extending this paradigm to disaggregated memory systems and accelerator architectures, this dissertation paves the way for robust data protection in future HPC systems.

#### 1.3 Contributions

Following are the main contributions of this work:

- Striking the Balance Between Security and Performance in High-Performance

Computing: We emphasize the imperative of integrating robust security measures

into high-performance computing systems while preserving optimal performance and

usability.

- Identifying Challenges and Advancements in TEE Applicability: We delineate critical challenges and intricacies pertaining to the effective utilization of Trusted Execution Environments (TEEs) within the realm of high-performance computing.

- Comprehensive Analysis of TEE-based Confidential Computing Architectures: We rigorously evaluate the suitability of prevalent commercial TEE architectures for the unique demands of high-performance computing environments, shedding

light on performance, compatibility, and security considerations.

- Data-Centric Enclave Design (*DESC*) for Scientific Computing Workloads:

This thesis presents an innovative enclave design paradigm, *DESC*, that eliminates the need for a complete OS within the enclave, and still allows an untrusted OS to manage resources for an unmodified enclave application. Tailored specifically for scientific computing workloads, the design choices underpinning *DESC* are both pragmatic and effective within HPC environments, yielding minimal performance overhead due to limited interaction between the OS and HPC applications. Moreover, *DESC* does not require modifications in the applications and allows them to leverage a multitude of operating system management optimizations vital attributes for HPC workloads.

- Simulation of Trusted Execution Environments in a Controlled Environment: We present our approach to simulating trusted execution environments, contributing to the understanding and advancement of secure architectures.

- Envisioning Future Enhancements and Extensions: Our work sets the stage for future explorations and enhancements, providing a comprehensive list of potential extensions that can build upon the foundation of our proposed enclave design (DESC).

By addressing these key contributions, our research underscores the significance of secure data processing in high-performance computing and paves the way for innovative solutions that bridge the gap between security, performance, and usability.

# 1.4 Organization

The remainder of this document is structured as follows: Chapter 2 offers a contextual background on the problem of secure HPC and the historical development of confidential computing. Chapter 3 presents a systematic analysis of the existing confidential computing architectures, focusing on their limitations for HPC applications. Chapter 4 thoroughly examines the performance implications of current commercial TEEs on HPC applications and identifies the specific requirements for a TEE tailored to scientific computing needs. Chapter 5 outlines the details of our proposed data enclave design called *DESC*. In Chapter 6, we explore the support of *gem5*-based simulations for evaluating secure compute environments,

serving as the baseline for assessing the ideas presented in this document. Chapter 7 outlines the prospects for future research and development. Finally, our conclusions are summarized in Chapter 8.

# Chapter 2

# Motivation and Background

In this chapter, we delve deeper into the rationale behind the security requirements within HPC centers and explore the unfolding developments in confidential computing over recent years.

Table 2.1: HPC Use Cases

| Domain         | Data Provider         | Data types              | Applications        |

|----------------|-----------------------|-------------------------|---------------------|

| Health care    | Hospital              | Health records, medical | Machine learning    |

|                |                       | images, gene sequences  | models              |

| Transportation | Public transportation | Driving routes          | Graph analysis      |

|                | authority             |                         |                     |

| Energy         | Utility company       | Home and building en-   | Real time demand or |

|                |                       | ergy usage              | response            |

# 2.1 Security Issues in High Performance Computing Environments

Some computational scientific research requires the use of high-performance computing (HPC) centers, that can provide large-scale computing and storage resources to users (researchers). Some scientific computing problems are large-scale and involve large data sets as well. This data is often provided by a third-party (data provider) and involve sensitivity of some kind. Figure 2.1 provides a high level overview of how a data provider, an HPC platform provider,

Figure 2.1: Interaction of multiple actors in an HPC center.

and an HPC user might interact with each other. Table 2.1 provides a few examples of scenarios where different data providers might provide some sensitive data to researchers to perform some type of analysis through their applications.

The use of sensitive data in HPC centers make it imperative to build HPC systems that can be secure and can be trusted by all the entities involved in a successful scientific workflow. These entities include, multiple users (who might be sharing all or a part of HPC system resources), HPC platform provider, and the data provider. HPC platform providers have tried to tackle this problem already [8, 9]. However, the current solutions have significant usability challenges. For example, processing sensitive health data requires dramatically different environments compared to those typically used in National Science Foundation (NSF) or Department of Energy (DOE) Office of Science high-performance computing facilities. Processing capabilities are limited to only a handful of racks and access requires virtual private networks (VPNs) and/or remote desktops. These onerous usability requirements are particularly cumbersome for the scientific community that is mostly used to working in very open, collaborative, and distributed environments, potentially with users from all over the globe.

### 2.1.1 HPC vs. Cloud Systems

The focus of this thesis is on high-performance computing systems, such as those that might be used in HPC centers (e.g., DOE National Labs).

HPC systems prioritize performance as their primary goal. This is in contrast to tra-

ditional virtualized cloud systems, which tend to emphasize manageability and flexibility over sheer performance. HPC systems are designed for executing complex computational tasks that require massive processing power, while virtualized cloud systems are more geared towards providing scalable and versatile computing environments for a wide range of applications. Multiple (sometimes heterogeneous) nodes, many cores per node, and integrated accelerators are some characteristics of the HPC systems. Moreover, applications on these specialized systems often bypass the OS for performance reasons. They do so to achieve peak processing power and minimal latency by establishing direct connections with hardware components, avoiding the overhead introduced by the operating system's abstraction layers. Unlike traditional HPC systems, cloud systems often employ multiple privilege layers. These layers provide enhanced control over access, resource allocation, and scalability, enabling greater adaptability and fine-grained permissions. With the advancements in cloud computing, the boundaries between scientific computing and cloud computing are increasingly getting blurred, however, the cloud computing is still not effective for large scale scientific problems [10, 11].

# 2.2 Confidential Computing

Confidential computing (which refers to the use of hardware-enforced (cryptographic) protection of data in use in contrast to the data at rest (storage) or in transit (I/O)) has recently emerged as a new paradigm of computing [12,13]. Confidential computing creates trustworthy systems rather than point-wise solutions against particular attacks. There are two primary ways to enable confidential computing: privacy-preserving computation techniques (like homomorphic encryption<sup>1</sup> and multi-party computation<sup>2</sup>) and trusted execution environments (TEEs). A comparative analysis of these techniques suggests that hardware TEEs generally incur much lower performance costs than other methods like homomorphic encryption and multi-party computation [17]. TEEs scale well to larger data sizes [13] and generally provide several additional security properties like attestability and code confiden-

<sup>&</sup>lt;sup>1</sup> Homomorphic Encryption: A form of encryption that allows computation on ciphertexts, generating an encrypted result which, when decrypted, matches the result of the operations as if they had been performed on the plaintext [14,15].

<sup>&</sup>lt;sup>2</sup>Multi-party Computation: A subfield of cryptography with the goal of creating methods for parties to jointly compute a function over their inputs while keeping those inputs private [14,16].

Table 2.2: Primary security properties of TEEs

| Property        | Definition                                                     |

|-----------------|----------------------------------------------------------------|

| Data            | unauthorized view of data is not allowed.                      |

| Confidentiality |                                                                |

| Data Integrity  | unauthorized entities are not allowed to alter the data.       |

| Code Integrity  | unauthorized entities cannot alter code in the TEE.            |

| Code            | unauthorized entities are not allowed to view the code inside  |

| Confidentiality | the TEE.                                                       |

| Authenticated   | enforcement of authorization checks before process launch.     |

| Launch          |                                                                |

| Programmability | if this is a TEE with arbitrary code or fixed function (code). |

| Attestability   | if a TEE can provide evidence/measurement of its origin &      |

|                 | current state.                                                 |

| Recoverability  | if a TEE can be recovered from a compromised state.            |

tiality (as shown in Table 2.2). A TEE is defined as follows by the Confidential Computing Consortium [13]:

"A Trusted Execution Environment (TEE) is commonly defined as an environment that provides a level of assurance of data integrity, data confidentiality, and code integrity. A hardware-based TEE uses hardware-backed techniques to provide increased security guarantees for the execution of code and protection of data within that environment."

Table 2.2 provides a set of fundamental properties inherent to a TEE. Figure 2.2 demonstrates how a trusted execution environment establishes a secure zone of trust for sensitive applications and their associated data. This process is elaborated upon in Section 3.4, that discusses the various mechanisms employed by current commercially-available TEEs to facilitate the creation of the secure enclave. In essence, a TEE constructs this realm of trust by capitalizing on the capabilities of hardware-based security features, secure boot protocols, attestation protocols, encryption, and other isolation mechanisms. These elements combine to isolate sensitive applications and data from external attackers and insider threats.

#### 2.2.1 Beyond TEEs

Fully homomorphic encryption [15], secure multi-party computation [16], and functional encryption all represent methods for computing over encrypted data by leveraging software algorithms, rather than hardware properties. Similar protection properties would apply in these cases, but with two important caveats and one potential benefit: first, these techniques are computationally expense and are therefore significantly slower than hardware TEEs. This is true even though performance has improved from being on the order of 1 trillion times slower than computing in cleartext ten years ago to perhaps only ten to a hundred times slower than computing in cleartext, depending on the technique used and the operations needing to be computed under encryption. For example database searches have been shown to be relatively fast [18–21], but operations requiring both addition and multiplication are much slower. The second caveat is that programs typically need very significant modification to use this technique, often causing each application of the technique to require extensive adaptation of the underlying cryptographic approach. A potential benefit is that leveraging some of these approaches could allow the threat model to be expanded to include protecting against malicious users.

That said, TEEs could also be used to protect against malicious users by incorporating a guard on the output of computation, such as differential privacy [22]. Indeed, a "complete" architecture that we envision is one in which "sensitive" data cannot be computed upon unless inside the TEE, and similarly, that sensitive data cannot be output unless via the TEE, which also enables output to be forced to protected through differential privacy [22] or some other kind of "guard" or gating policy.

## 2.3 Confidential High-Performance Computing via TEEs

Current solutions to provide security in HPC centers usually require specialized computing facilities and access protocols which can be cumbersome for the users/researchers. In contrast, TEE based security solutions can be built in normal computing facilities (without any restrictions on users' access mechanisms). Figure 2.3 provides a high-level picture of how TEEs can help to create a zone of trust for sensitive data in HPC centers.

This thesis focuses on building trusted execution environments for HPC systems. There

Figure 2.2: Trusted execution in traditional computing systems. 'C' stands for a core. Zone of trust referst to secure computational and memory resources used by a secure application that is enabled via the used of a TEE.

Figure 2.3: Creating a zone of trust for sensitive data in HPC centers. The figure on the left shows a general TEE and the figure on the right shows how that TEE can be used to enable a data scientist to compute on sensitive data provided by a trusted data provider and keep it secure from other entities in the system.

are a number of trusted execution environments that have been introduced by commercial processor vendors like Intel's SGX (Software Guard Extension) [4], ARM's TrustZone [23], AMD's SEV (Secure Encrypted Virtualization) [24], and research platforms like RISC-V's Keystone [1] and Sanctum [25]. A brief survey of these TEEs is provided in the Appendix. they support, the security properties they provide, and the mechanisms they use to pThese TEEs differ in terms of the programming modelrovide those properties.

We show that the current commerical TEEs do not work well for HPC use case because of multiple reasons: 1) their threat model is not a good fit for HPC, 2) programming model of current TEEs does not work well for HPC, and 3) their performance impact can be significant, specially for HPC scale workloads.

We propose a data-centric enclave design called *DESC* (discussed in Chapter 5) that enables secure scientific computing by protecting the data of scientific applications from other software (including the OS) running on a computing system. *DESC* allows the secure execution of unmodified applications while minimizing the TCB size.

# Chapter 3

# Limitations of Confidential Computing via TEEs for HPC Systems<sup>1</sup>

Trusted execution environments (TEEs) are primary enablers of confidential computing. This chapter presents a systematization of the existing trusted execution environments in industry and academia. We highlight the common mechanisms these TEEs employ to provide different security guarantees and offer a detailed comparative analysis of different TEE proposals. TEEs are anticipated to be a promising solution for addressing certain security challenges in the high-performance computing (HPC) domain. However, this chapter shows why existing TEEs are unsuitable for high-performance computing applications. Finally, we present our call for action to work to evolve the TEE technologies in conjunction with the evolving high-performance computing landscape.

### 3.1 Introduction

In this chapter, leveraging a survey of the existing literature, we identify the common mechanisms trusted execution environments (TEEs) use to isolate a sensitive application and its state from the rest of the system. We show how existing mechanisms do not fit well with the modern **high-performance computing** systems and what are the most promising directions to pursue to ensure that the high-performance computing systems can maintain

<sup>&</sup>lt;sup>1</sup>This work has been published in IEEE SEED 2022 [26]

Figure 3.1: History of the computing landscape. This figure shows the evolution process of traditional high-performance computing systems. Computing systems have evolved from single processes on a single-core system to multi-threaded applications on heterogeneous multi-core systems.

isolation of sensitive data [8, 27]. In particular:

- We provide a categorization and systematization of existing trusted execution environments (TEEs).

- We group TEEs based on the key mechanisms/ideas they rely on to figure out the underlying principles that confidential computing is based on today.

- We undertake an examination of the historical progression of conventional computing systems and the implications of this evolution on their security. Using our observations, we point out many ways in which existing TEE technologies would not fit with modern high-performance computing systems in that: 1) they require large application modifications, 2) they have large TCBs, 3) they focus on core-level execution, and 4) they do not take side-channel attacks into consideration.

- We explore future research directions that can enable TEEs to be used for highperformance computing systems.

- We also use the insights discussed in this chapter to build an HPC focused TEE, *DESC*, discussed in details in Chapter 5.

### 3.2 Computing Landscape

### 3.2.1 History

Most protection and isolation mechanisms in computing systems (e.g, virtual memory, process isolation) were developed when the computing system model was very different from the

landscape of today [28,29]. It is essential to look at the history of the computing landscape and its evolution over time. Initially, the computing system model was a single machine with a single core running one application (shown in the left-most part of Figure 3.1) [30]. The operating system would create an environment where the application perceives itself as the sole entity operating within the system [31]. This model had a vast TCB (required trusting all the components in the system). Over time, multiple applications started to share the hardware (still a single-core system, as shown in the middle part of Figure 3.1). The OS time multiplexed the applications on the same hardware. The OS started implementing virtual memory abstraction to isolate one application from the others. Eventually, the computing systems evolved such that the processor became a multi-core processor (shown in the rightmost part of Figure 3.1) [31]. Applications evolved and started to have more than one execution thread. In this model, the OS would manage multiple threads of execution on multiple cores. In summary, the systems became much more complex to manage; however, they still used the virtual memory based isolation primitives to ensure isolation among applications on these multi-core systems.

Traditionally, operating systems were responsible for managing most aspects of memory, IO, and computing. The virtual memory subsystem used for isolation also provided applications an abstract view of physical memory, allowing them to under-subscribe or oversubscribe physical memory. The virtual memory subsystem evolved, but the **coupling of isolation provision**, and **resource management** stayed intact [32,33].

### 3.2.2 Current Computing Landscape

Next, we discuss the current (and future of) computing landscape. In Section 3.5, we will discuss how these advancements in the high-performance computing landscape become the reason for limited applicability of current TEE technologies for HPC. Figure 3.2 shows a system level view of modern high performance computing systems.

Accelerator Integration: Computing systems have started to integrate different types of accelerators with general-purpose CPUs. In modern computing systems, devices like GPUs, FPGAs, and other accelerators have become a part of the virtual memory subsystem and share virtual address space with applications running on the CPU. The memory allocation is still managed by the OS on the CPU, as the accelerators do not run an OS.

Heterogeneous Memory Systems: Heterogeneous memory systems have become much more prevalent today and rely on emerging memory technologies and more traditional DRAMs. For example, Intel's Sapphire Rapids [34] will include an HBM, a DDR5, and a (byte addressable) NVM (non-volatile memory). The rationale behind using different memory technologies is to allow for different memory types to be used for different applications or phases of a single application. This trend of heterogeneous memory systems makes it necessary to have the ability to migrate data from one device (physical address) to the other (physical address).

Remote Memory Systems: With an increasing adaption of systems where the memory might live remotely (be the non-uniform memory access (NUMA) systems or disaggregated systems [35]), memory management might not be entirely done by a (local) OS. Memory management might rely on some remote software/hardware. Network interfaces today have started to rely on RDMA (remote DMA), which bypasses OS and copies the data into a process's virtual address space directly.

Highly Multi-threaded Applications: Especially, in high performance computing systems, the applications are composed of multiple threads, which might execute on multiple cores. Traditionally, the threads executed on homogeneous CPU cores, and the OS managed which threads would execute and where would they execute. In the modern computing systems, the use of accelerators, scale out architectures, and disaggregation of memory resources lead to new models of computing. The host OS might not control all the threads of execution for an application.

Direct Memory Access by Devices: Historically, whenever the devices needed to access application's memory, they had to do that via OS as well. All the memory accesses from/to the device have historically being intercepted by the OS. This is not true anymore for high performance computing systems. DMA and RDMA allow direct access to memory by the devices.

### 3.3 HPC Focused Trusted Execution Environments

Considering the evolving computing landscape and the security concerns for high-performance computing environments, in this section, we point out important requirements for which we believe that the secure architectures focused on HPC should fulfill. Following are these

#### System view today

Figure 3.2: Modern high performance computing systems. Applications on these systems scale across local nodes, (integrated or remote) accelerators, and remote nodes.

#### requirements:

- (R1) Requirement 1: HPC-focused TEEs should have a minimum performance impact on HPC-style workloads (heavily multi-threaded and have large working sets).

- (R2) Requirement 2: TEEs should not require application modifications or linking against special libraries as HPC applications often rely on third party libraries. However, we note that the application modifications could benefit security although they might impose more usability requirements on users.

- (R3) Requirement 3: HPC-focused TEEs should exclude most of the OS from the TCB. Since, modern HPC applications often bypass the OS for performance benefits (by handing I/O in user-space libraries), reliance on OS security primitives should be minimal.

- (R4) Requirement 4: HPC-focused TEEs should be capable of expanding across compute nodes as HPC applications mostly scale across multiple nodes and rely on message passing run-times like MPI for communication across these nodes. Moreover, HPC centers (like data centers) are expected to rely on disaggregated architectures (e.g. pooling of memory resources), to increase the utilization of compute/memory resources and save the cost. An HPC focused TEE should consider disaggregated resources in its threat model as well.

- (R5) Requirement 5: HPC-focused TEEs should enable enclaves which can scale to processing elements other than the general purpose CPUs.

There exist multiple TEE technologies today. In the next section, we will analyze if these existing techniques fulfill the previously mentioned requirements of an HPC-focused TEE.

### 3.4 Systematization of TEEs

In this section, we systematize and classify the existing TEEs into different categories.

Generally, TEEs provide complete control over the trusted computing base (TCB) [12]. The data/code confidentiality and integrity properties of a TEE are usually enabled by isolating an enclave's memory (via the zone of trust shown in Figure 2.2) from the rest of the system while an enclave is in use. Before providing a classification of TEEs, we will first look at some of the common primitives TEEs use to isolate an enclave from the rest of the system. We also discuss the mechanisms/ways the software or other hardware components use these primitives.

#### 3.4.1 Page Table Entry Metadata

Page table entry-level metadata refers to any physical page metadata that TEEs might maintain to identify an enclave page in the hardware. Multiple TEEs rely on this information to implement access control mechanisms. For example, SGX [4] maintains EPCM (enclave page cache map) entries which keep track of the enclaves that own the pages in EPC (enclave page cache), along-with information on the validity of the EPC page. Only SGX instructions can update the entries in the EPCM; therefore, the system software can track any unwanted change in the enclave's address map. Another example is AMD SEV [3], which uses bit 47 of the physical address in a page table entry to identify whether this page is secure. The hypervisor or the host OS manages this bit.

### 3.4.2 Encryption

Encrypting physical memory is a very common primitive used by TEEs (e.g., AEGIS [36], SGX [4], Graviton [37], HETEE [38], ARM RME [39]) to ensure confidentiality of data belonging to an enclave (and can be a strong mitigation against physical attacks). Usually, the TEEs rely on an encryption key that is generated and stored in an (isolated) trusted pro-

cessor (or some hardware component). For example, AMD SEV [3] relies on an ARM-based processor (AMD Platform Security Processor) for key management. As the cache blocks move from/to the processor chip to/from the DRAM, the key is used to encrypt/decrypt the cache blocks transparently.

#### 3.4.3 Physical memory isolation via ISA extensions

RISC-V based TEEs (e.g., Keystone [1], CURE [40], Elasticlave [41], TIMBER-V [42]) rely on the PMP (physical memory protection) ISA extension. PMP controls U (user) and S (supervisor) modes' access to certain memory regions. The allowed access (r-w-x) permissions and the memory region can be configured using PMP address (pmpaddr) and configuration (pmpcfg) registers. There also exist proposals for providing physical memory protection to IO devices via IOPMP [43].

#### 3.4.4 Use of tags/identifier in hardware

Some TEEs also use a tag or identifier to distinguish enclave data from other software in the system (for access control). For example, CURE [40] uses an enclave ID for bus arbitration to enable enclave to the peripheral binding. For this purpose, CURE [40] hardware relies on a filter engine on the system bus. Bastion [44] depends on a module ID, which is a new component in caches and TLB and acts as a tag for the currently executing process. ARM TrustZone [23] uses a single-bit identifier to distinguish between the secure and non-secure world (for device communication). SiFive's WorldGuard [45] can tag bus transactions to differentiate between software contexts that originated a request, allowing the target to determine if it trusts the requestor. HECTOR-V [46] also relies on identifiers embedded in interconnects, which helps create a safe IO path. AMD SEV [3] hardware tags all code and data with its VM ASID (inside the SoC), indicating the VM, which is the data owner.

### 3.4.5 Privileged Software/Hardware

Trusted execution environments mostly do not trust the host OS and try to bypass the host OS privileges. They usually do this through additional hardware/software components

Figure 3.3: Classification of TEEs and some examples of each class. [Note: Emb. : Embedded, Mod.: Modern, Kern. : Kernel, Cont. : Container, Proc. : Process, VM : Virtual Machine]

to perform privileged operations focused purely on security. For example, CURE [40] uses a hardware-based security monitor to monitor the system bus's access. Keystone [1] uses an M-mode software-based security monitor to manage physical memory isolation primitive (i.e., PMP). Similarly, ARM RME (realm management extension) [39] relies on a monitor to enforce its security guarantees.

#### 3.4.6 Classification of TEEs

We present a classification taxonomy of existing trusted execution environments to enable a better understanding of the vast design space that is covered by TEEs. Figure 3.3 shows this taxonomy with some examples of TEEs from each class. TEEs can be classified based on different factors. We use the following factors for this classification:

- *Isolation level:* This defines at what level the secure and non-secure components are isolated.

- Threat model configurability: This determines if the threat model of a TEE can be configured (either at the run time or the implementation time).

- Enclave privilege level: This is the privilege level at which the enclave operates.

- Openness: This determines whether a TEE is open-source or closed-source, with closed-source models often prevalent in industrial solutions and open-source models more

commonly found in academic contexts.

- Abstraction level: This is the level of abstraction at which the TEE provides an interface to the user.

- Target computing: This is the type of computing which the TEE is mainly designed for.

A more systematic and detailed comparison of different TEEs is provided in Table V (in Appendix section). Here, we provide some discussion and observations on different classes of TEEs that are shown in Figure 3.3 with important examples.

We observe that the current TEEs which provide the highest isolation level usually achieve it via physical isolation or partitioning at a very coarse granularity. For example, AWS Nitro enclaves are an example of highly isolated enclaves that provide (constrained) enclave virtual machines with no storage, network, or interactive access [47]. AWS Nitro enclaves have only a single point of connection to the outside world via a bi-directional virtual machine socket (vsock) between the parent instance and an enclave [47]. The major drawback of highly isolated enclaves is the difficulty to use them. For example, applications will have to rely on message passing, RPC or micro-services to interact with their secure compartment on the enclave virtual machine (in case of AWS Nitro). Other examples of highly isolated enclaves, ARM TrustZone [23] and Realms [39], partition the entire physical address space at a very coarse granularity (into secure and non-secure worlds).

There are also many examples of configurable TEEs (which can lead to variable TCB sizes). Configurability is a desirable property in the current heterogeneous world. Applications executing on a modern (heterogeneous) HPC system might not have the same sensitivity level (or require the same security guarantees, e.g., integrity is not essential if the application is not going to reuse previously written data). CURE [40] provides the ability to define enclave trust boundaries (at different granularity levels). AEGIS [36] provides the ability to have both a trusted and untrusted OS. ShEF [53], a trusted execution environment for FPGAs, provides the ability to customize encryption logic parallelism and authentication block size.

TEEs could opt for a specific security vs. cost tradeoff depending on the computing type

they are targeting. We observe that most of the earlier TEEs focused on general-purpose desktop/cloud or embedded computing (e.g., [3,23,48]). However, some recent examples of academic proposals target parts of modern computing systems. For example, HETEE [38] targets server rack-scale computing. Graviton [37] and HIX [54] tried to enable isolated execution on GPUs, ShEF [53] targets FPGAs and TDMem [55] focused on RDMA-based disaggregated systems.

Privilege-level based classification divides enclaves into kernel-space or user-space enclaves. Kernel-space enclaves can run trusted kernel-mode software inside the enclave, which means that these enclaves generally have a large TCB. For example, Keystone [1] requires having a kernel-space runtime (for user-space application's resource management) inside the enclave. SEV [3] allows kernel-space enclaves, where the guest OS is a part of the enclave. SGX [4], on the other hand, is a user-space enclave and has smaller TCB (compared to SEV). However, user-space enclaves have to pass the (trusted) user-space and (untrusted) kernel-space boundary to perform system-level services, which can also have security concerns.

#### 3.5 Limitations of Existing TEEs

Next, we discuss some limitations of existing trusted execution environments and show how they hinder the adoption of secure execution environments for modern computing systems.

Confidential computing environments rely on hardware primitives to protect or isolate an enclave's memory from the rest of the system. These primitives can sometimes impose restrictions on the system's resource management, decreasing the usability and efficiency of the system. We now present the following observations on the kind of limitations confidential computing can impose on modern HPC environments.

#### 3.5.1 Heavy Application Code Modifications

Currently, we lack the necessary primitives that allow fine separation of management and protection within a computing system. Consequently, in the context of confidential computing threat models, the entire operating system is generally considered untrusted.

This limitation significantly impacts the programming model of most TEEs, leading to reduced support for traditional C libraries. For instance, simpler libraries like muslc are favored over more complex alternatives such as glibc. Consequently, userspace applications,

particularly large ones found in high-performance computing systems, necessitate extensive modifications and experience functional limitations.

#### 3.5.2 Large Trusted Compute Base (TCB)

Given the limited trust placed in the operating system within the confidential computing threat models, entrusting resource management to the OS can introduce vulnerabilities. For example, managing an enclave's address space allows a malicious OS to launch page fault-based attacks on enclaves leaking the access patterns of the sensitive application. These attacks are possible because OS can modify access permission of enclave's pages, which would lead to page faults, and thus OS can determine the enclave access pattern. Such attacks, called *controlled channel attacks* [56] are deterministic (and noise-free) and can have large leakage bandwidth compared to other noisy side channels. The proposed solutions to the controlled channel attacks require the enclave to control its page tables and enforce secure-paging policies within an enclave. Examples of such proposals include Autarky [57], Keystone [1], and CURE [40]. The drawback of these approaches is that they lead to a *larger TCB* and more complexity in the enclave.

The scheduling and synchronization of threads by an untrusted OS can lead to multiple security issues.<sup>2</sup> For example, an untrusted OS can influence a machine learning model leading to poisoning attacks by controlling the order in which the threads of the training algorithm are executed [58]. To solve this problem, some TEEs have implemented limited thread handling inside the enclave, which reduces the system's efficiency overall. For example, enclaves (like SGX [4]) enforce a static number of threads because they might only allow statically-defined entry points for executing threads. Many of the TEEs based on SGX have similar limitations. Enclaves like Keystone [1] do not support multi-threaded execution at all at the time of writing this thesis. In summary, today's enclaves generally do not have good support for multi-threaded execution unless they are willing to have a large TCB. Interestingly, virtual machine (VM) based enclaves include a guest OS in the TCB and allow multi-threaded applications to run transparently. Not only do the VM-based enclaves have a very large TCB, but multi-threaded execution in virtual machines can also have

<sup>&</sup>lt;sup>2</sup>Scheduling based denial of service attacks are common, but generally not a part of the threat model of confidential computing systems.

significant performance implications. For example, when threads yield during synchronization operations, they can cause costly KVM exits [59,60].

#### 3.5.3 Focus on Core Level Execution