정보기술(IT) 시장에 관심 많으신 독자 여러분, 안녕하세요. 다사다난했던 2024년의 마지막 하루. 여러분은 어떻게 보내고 계신가요?

저는 세계 반도체 업계에서 올해와 내년을 관통하는 키워드가 무엇인지 생각해보고 있었는데요. 2나노(㎚·10억 분의 1m). 저는 이 키워드가 가장 먼저 떠올랐습니다.

2나노 파운드리는 현존하는 반도체 제조 공정에서 가장 미세하고 정교합니다. 내년 삼성전자와 TSMC의 최대 격전지이기도 합니다.

삼성전자는 TSMC 기술을 잡을 수 있는 또 한번의 찬스를 놓치지 않기 위해, TSMC는 자신이 압도적 1위라는 것을 증명하기 위해 사력을 다하고 있을텐데요.

이쯤에서 궁금합니다. 대만의 왕이자 삼성의 라이벌인 TSMC는 2나노를 어떻게 준비하고 있을까. 수율이 이미 60%가 넘는다던데. 그럼 어느 정도 완성돼 있을까. 어떤 기술과 데이터로 애플 등 최대 고객사들을 맞이할 준비를 하고 있을까. TSMC가 공개한 다양한 그래프와 수치로 들여다보고자 합니다. 총 2편으로 구성했습니다.

더 작게, 더 빨리, 더 효율적으로

이 논문의 출처는 이달 미국에서 열렸던 'IEDM 2024'에서 TSMC가 발표한 논문입니다. 본격적으로 시작하기 전에 딱 세 가지 키워드만 기억하고 출발하면 쉽습니다. △전력(power) △스피드 △집적도(density)입니다. 이 세 가지를 끌어올리기 위한 노력의 결과물이 이 논문이거든요.

한줄로 요약하면 이렇습니다. "고객님, 전력 효율을 올리면 성능은 떨어지고, 결국 전력 소모량(돈)을 올려야만 성능이 뛸 수밖에 없다는 딜레마가 있죠? 우리 돈 아껴야 하잖아요. TSMC는 2나노로 더 작은 반도체를 만들 수 있기 때문에 전력·성능 두 마리 토끼를 다 잡아버렸지 뭐예요!"입니다.

결론은 간단하지만 우리는 '반도체에 미친 자들' 일명 반친자니까요. 여러 테크 지식들을 버무려서 살펴봅시다.

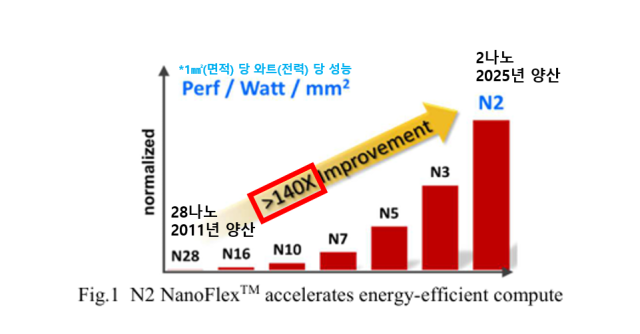

지금부터 여러 수치를 보여드리겠습니다. 우선 2나노로 들어서면 대단한 성능 개선이 있습니다. TSMC 2나노 칩은 일정한 면적(㎟)에서 동일한 전력(W)을 썼을 때, 성능이 28나노 칩보다 140배나 개선됐습니다. 28나노 공정은 2011년 양산을 시작했습니다. 2나노를 2025년에 양산한다고 가정하면 14년 새 성능이 140배 증가한 셈이네요.

자, 그럼 직전 공정인 3나노와 비교해보면 어떨까요? 2나노 소자에 3나노 칩과 같은 전력을 가하면 최대 15% 속도를 높일 수 있고요. 동일 전력으로는 최대 35% 성능 차이가 납니다.

전력효율과 스피드를 둘 다 좋아지게 하는 방법. 회로 축소로 한 칩에 더 많은 트랜지스터를 집어넣는 '집적도 증가'입니다. 엔지니어들이 스케일링(scaling)에 목숨을 거는 이유죠.

TSMC 2나노에는 회로 축소를 위해 '나노시트'가 처음으로 적용됐습니다. 여러분들에게 익숙한 게이트올어라운드(GAA), 삼성전자가 2022년 처음으로 적용한 소자 구조인데요.

말그대로 게이트가 전류가 흐르는 채널의 모든 면을 감싸고 돌기 때문에 회로를 축소해도 데이터 이동이 더 원활할 수 있다는 장점이 있습니다. 대신 공정 난도는 훨씬 증가합니다.

TSMC는 GAA의 장점에 하나를 더 얹습니다. '숏 소자(short cell)'와 '톨(tall) 소자'를 각각 만든다는 건데요. 고성능 분야는 톨·그렇지 않은 분야는 숏 소자로 설계해 적재적소에 배치(PnR, Placement and Routing)한다는 아이디어입니다. 숏·톨 소자의 정확한 정체는 등장하지 않았지만, 숏·톨 조합이 순수 숏 소자로만 회로를 설계하고 배치했을 때보다 성능이 15%나 개선됐다는 이야기를 강조했습니다. 스포츠 경기로 치면 용병술이 꽤 좋았다는 얘기로봐주시면 좋을 것 같습니다.

"죽이는 미세 공정이네요"

TSMC는 2나노 공정에서 나타나는 각종 특성도 공개했는데요. 미세하게, 불필요한 전력이 샐 틈 없이 견고하게 칩을 설계했다는 점을 어필했습니다.

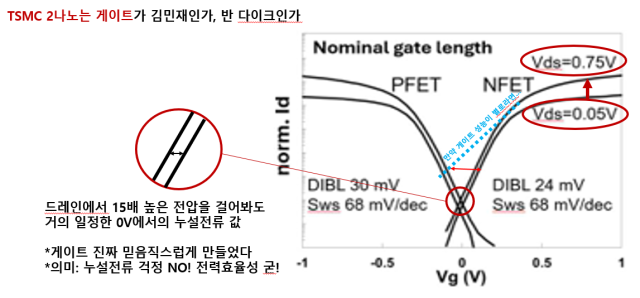

우선 GAA 설계를 아주 '빡세게' 했다는 걸 보여준 게 눈에 띕니다.

트랜지스터는 크게 소스-게이트-드레인 세 부분으로 나뉘죠. 이걸 수도관에 비유하면요. △소스는 물이 처음으로 공급되는 수도관 △게이트는 물길을 트거나 잠그는 수도꼭지 △드레인은 파이프를 통과한 물이 빠져나가는 배수구로 보시면 됩니다.

트랜지스터가 동작하려면 게이트와 드레인에 각각 전압이 걸리는데요. 이때 연산에 필요한 전자 알갱이들이 이동하기 시작합니다. 마치 수도꼭지(게이트)가 열릴 때, 배수구(드레인)에서 임의의 힘으로 배수구 쪽으로 물을 쫙 당기는 원리인 거죠.

좋은 트랜지스터, 특히 좋은 게이트는 두 가지 조건이 필요합니다.

1)게이트가 꺼진 상태에서는 드레인에서 아무리 세게 전압을 가하더라도 전자 알갱이들이 게이트를 비집고 들어가면 안됩니다. 너무 많이 새면 누설전류가 발생하니까요. 이건 게이트(채널) 길이가 짧아지면서 더 심각해지는데요. 이른바 ‘DIBL’ 현상입니다. 엔지니어들의 중요한 해결과제입니다.

2)게이트에 전압을 가했을 때, 트랜지스터 스위치가 켜지는 시간이 짧을수록 좋습니다. 이것도 전력 효율과 관련있습니다.

지금 위에서 보여드리는 그래프는 드레인 쪽에서 0.05V를 가하든, 15배가 넘는 전압인 0.75V를 가하든 오르막길 곡선(Subtheshold(S.S) 스윙)에서 큰 차이가 안보이죠. 게이트에 전압이 가해지기 전까지 어떤 외압(?)이 있더라도 누설 전류의 차이가 거의 없다는 걸 보여줍니다. 전류를 통제하는 게이트가 상당히 견고하게 만들어졌다는 의미죠.

조금 전 설명드린 조건 2)를 만족하는 S·S(Subthreshold Swing) 곡선도 아주 이상적인 수치인 68mV/dec을 만족합니다. 한마디로 물을 완전하게 틀어막을 수 있는 수도꼭지인데, 틀기만 하면 바로 콸콸 쏟아지는 최상의 제품을 만들었다는 얘깁니다.

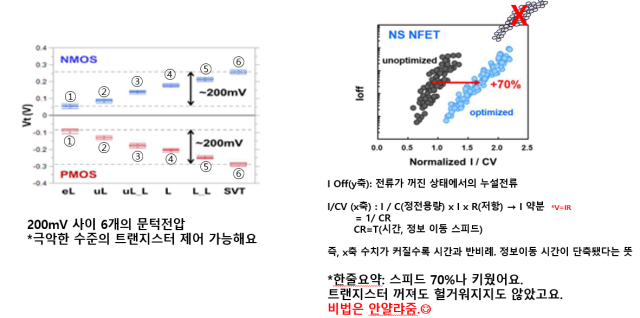

또 있습니다. 보통 데이터 속도를 높이기 위해 설계를 하다보면, 전기 알갱이가 회로를 벗어날 확률이 높아집니다. 오프-전류(current) 때, 즉 트랜지스터가 꺼졌을 때 누설전류가 증가하는 문제가 생기는데요. 무슨 방법을 썼는지는 공개하지 않았지만 최적화 공법으로 오프 전류에서의 누설 전류는 기존과 비슷하게 가져가면서도 데이터 전송 속도를 70%나 높이는 기술을 구현했습니다.

미세한 전압을 제어하는 기술에도 자신이 있는 분위기입니다. 왼쪽 그래프를 보시면, 200mV 안에 6개의 문턱전압을 넣어놨습니다. 문턱전압은 말그대로 트랜지스터가 처음 동작하기 시작하는 전압이죠. 수십~수백 억개의 트랜지스터가 6개 종류의 전압에서 각각 켜지게끔 설계됐다는 얘기인데요.

챗GPT에 검색해보니 일반적인 저전력 문턱전압 간격은 50~70mV라고 합니다. 2나노 칩의 간격은 약 40mV인데요. 간격이 좁으면 좁을수록 애매한 전압을 걸었을 때 트랜지스터가 오작동할 확률도 커지죠. TSMC는 이 문제까지 극복한 듯 합니다. 어떤 취재원은 이 그래프를 보고 "죽이는 미세공정"이라고 해석했습니다.

저전력에서의 성능 개선, 이른바 ‘전성비’도 내세웠습니다. 동작전압과 와트 당 성능의 관계를 나타낸 표인데요. 저전압인 왼쪽의 상태를 살펴보면 2나노 GAA 칩이 3나노 칩보다 와트 당 성능이 우월하다는 결과를 내놓았습니다. 예컨대 애플 스마트폰 AP를 2나노로 만들면 3나노 때보다 적은 전력을 쓰면서도 3나노 칩보다 더 뛰어난 성능을 낼 수 있다는 뜻을 내포한 거겠죠.

2편에서도 말씀드리겠지만 논문에서 약간 아쉬운 부분도 있습니다. TSMC는 "우리가 이렇게 했어요" 까지는 보여주지만 "어떤 방법으로 이걸 최적화했어요"는 보여주지 않았습니다. 영업 비밀이라서 따로 설명하지 않은 것으로 보이는데, 아무튼 결과만 봤을 때 이렇게만 만들어지면 TSMC가 2나노 GAA에서도 굉장한 진보를 이뤘다는 해석이 많습니다.

이제 2편에는 2나노에 적용된 공정들에 대한 자료를 보여드리려고 합니다. 하이브리드 본딩과 배선에서의 새로운 시도, SRAM에 관한 이야기도 등장합니다. 올해 강해령의 하이엔드 테크 연재에 관심 가져주셔서 진심으로 감사드립니다. 1월 2일 TSMC 2나노 2탄으로 찾아뵙겠습니다.

< 저작권자 ⓒ 서울경제, 무단 전재 및 재배포 금지 >

hr@sedaily.com

hr@sedaily.com